# Advanced Micro Devices

# PAL20X10A Series AmPAL20L10B/-20/AL

XOR Registered 24-pin TTL Programmable Array Logic

### DISTINCTIVE CHARACTERISTICS

- XOR gates on registered outputs

- **■** Efficient implementation of counters

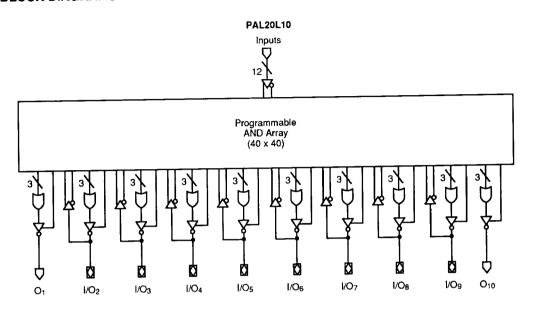

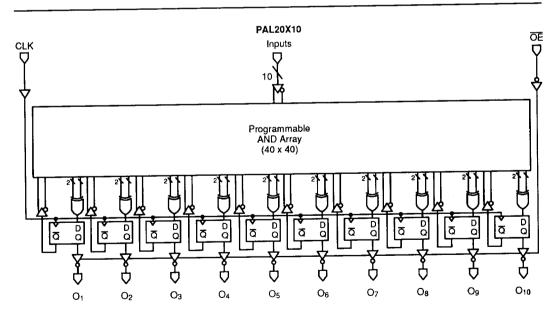

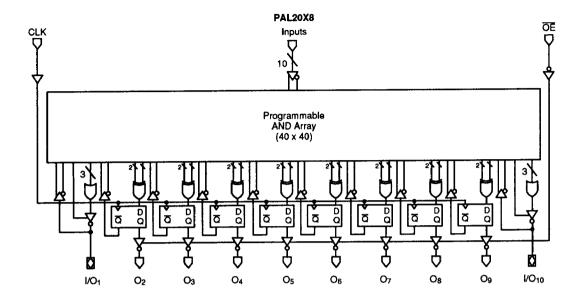

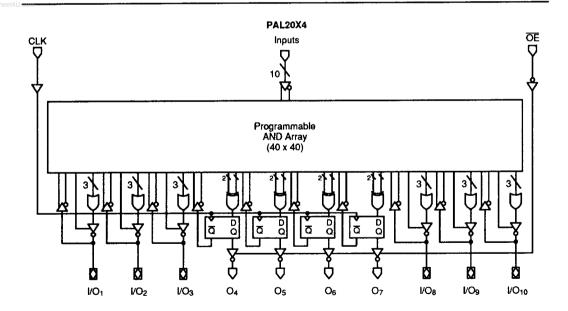

- Popular 24-pin architectures: 20L10, 20X10, 20X8, 20X4

- Programmable replacement for high-speed

TTL logic

- Power-up reset for initialization

- Register preload for testability

- Easy design with PALASM<sup>®</sup> software

- Programmable on standard PAL® device programmers

- 24-pin SKINNYDIP® and 28-pin PLCC packages save space

### GENERAL DESCRIPTION

The PAL20X10A Series offers Exclusive-OR gates preceding each flip-flop. The XOR gate combines two sum terms, each composed of two product terms. This extra level of logic is very efficient for counter applications.

The combinatorial member of the family, the PAL20L10, offers three product terms per output with no XOR gate. A fourth product term provides the enable term. While the registered devices are offered in only one performance option, the 20L10 is offered in four performance grades. Note that three of these options follow the "old" AMD part numbering system while the fourth follows the "old" MMI part numbering system, as do the registered devices.

The family utilizes Advanced Micro Devices' advanced bipolar process and fuse-link technology. The devices provide user-programmable logic for replacing conventional SSI/MSI gates and flip-flops at a reduced chip count.

The family allows the systems engineer to implement the design on-chip, by opening fuse links to configure AND and OR gates within the device, according to the desired logic function. Complex interconnections between gates, which previously required time-consuming layout, are lifted from the PC board and placed on silicon, where they can be easily modified during prototyping or production.

The PAL device implements the familiar Boolean logic transfer function, the sum of products. The PAL device is a programmable AND array driving a fixed OR array. The AND array is programmed to create custom product terms, while the OR array sums selected terms at the outputs. In addition, the PAL device provides the following options:

- Variable input/output pin ratio

- Programmable three-state outputs

- Registers with feedback

Product terms with all fuses opened assume the logical HIGH state; product terms connected to both true and complement of any single input assume the logical LOW state. Registers consist of D-type flip-flops that are loaded on the LOW-to-HIGH transition of the clock. Unused input pins should be tied to Vcc or GND.

The entire PAL device family is supported by the PALASM software package. The PAL family is programmed on conventional PAL device programmers with appropriate personality and socket adapter modules. See the Programmer Reference Guide for approved programmers. Once the PAL device is programmed and verified an additional fuse may be opened to prevent pattern readout. This feature secures proprietary circuits.

### PRODUCT SELECTOR GUIDE

| DEVICE                                                    | DEDICATED INPUTS | OUTPUTS            | PRODUCT TERMS/<br>OUTPUT | FEEDBACK    | ENABLE         | tpD<br>(ns)          | lcc<br>(mA)              |

|-----------------------------------------------------------|------------------|--------------------|--------------------------|-------------|----------------|----------------------|--------------------------|

| AmPAL20L10B<br>AmPAL20L10-20<br>AmPAL20L10AL<br>PAL20L10A | 12               | 8 comb.<br>2 comb. | 3 3                      | I/O<br>-    | prog.<br>prog. | 15<br>20<br>25<br>30 | 210<br>165<br>105<br>165 |

| PAL20X10A                                                 | 10               | 10 reg.            | 4, XOR                   | reg.        | pin            | 30 (ts)              | 180                      |

| PAL20X8A                                                  | 10               | 8 reg.<br>2 comb.  | 4, XOR<br>3              | reg.<br>I/O | pin<br>prog.   | 30                   | 180                      |

| PAL20X4A                                                  | 10               | 4 reg.<br>6 comb.  | 4, XOR<br>3              | reg.<br>I/O | pin<br>prog.   | 30                   | 180                      |

PAL, PALASM, and SKINNYDIP are registered trademarks of Advanced Micro Devices. This part is covered by various U.S. and foreign patents owned by Advanced Micro Devices

Publication # 10303 Rev. B Amendment/0

Issue Date: January 1990/W. DataSheet 4U.com

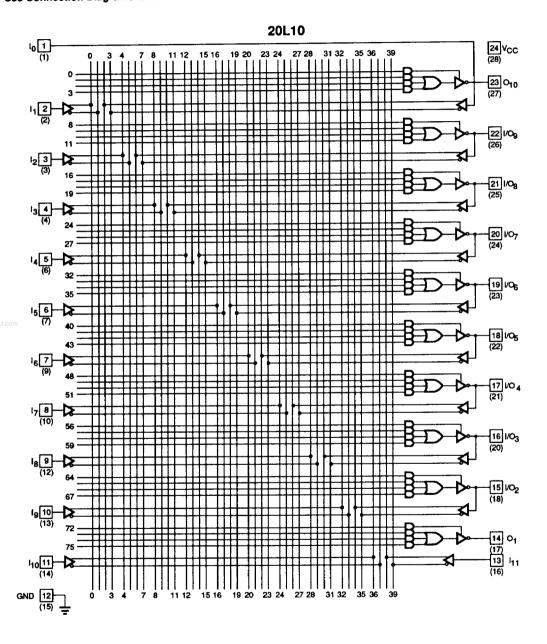

### **BLOCK DIAGRAMS**

10303-001A

10303-002A

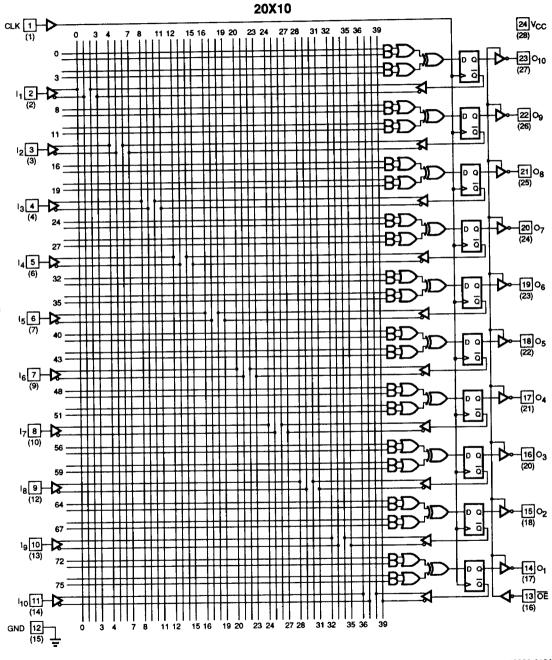

### **BLOCK DIAGRAMS**

10303-003A

10303-004A

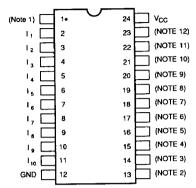

# CONNECTION DIAGRAMS Top View

### SKINNYDIP/FLATPACK

10303-005A

| Note | 20L10            | 20X10           | 20X8              | 20X4              |

|------|------------------|-----------------|-------------------|-------------------|

| 1    | lo               | CLK             | CLK               | CLK               |

| 2    | i <sub>11</sub>  | ŌĒ              | ŌĒ                | ŌĒ                |

| 3    | O <sub>1</sub>   | O <sub>1</sub>  | I/O <sub>1</sub>  | I/O <sub>1</sub>  |

| 4    | I/O <sub>2</sub> | O <sub>2</sub>  | O <sub>2</sub>    | I/O <sub>2</sub>  |

| 5    | I/O <sub>3</sub> | O <sub>3</sub>  | О3                | I/O <sub>3</sub>  |

| 6    | 1/04             | O <sub>4</sub>  | O <sub>4</sub>    | O <sub>4</sub>    |

| 7    | I/O <sub>5</sub> | O <sub>5</sub>  | O <sub>5</sub>    | O <sub>5</sub>    |

| 8    | I/O <sub>6</sub> | O <sub>6</sub>  | O <sub>6</sub>    | O <sub>6</sub>    |

| 9    | 1/07             | O <sub>7</sub>  | 07                | O <sub>7</sub>    |

| 10   | I/O <sub>8</sub> | O <sub>8</sub>  | O <sub>8</sub>    | I/O <sub>8</sub>  |

| 11   | I/O <sub>9</sub> | O <sub>9</sub>  | O <sub>9</sub>    | l/O <sub>9</sub>  |

| 12   | O <sub>10</sub>  | O <sub>10</sub> | I/O <sub>10</sub> | I/O <sub>10</sub> |

### PIN DESIGNATIONS

| CLK | Clock          |

|-----|----------------|

| GND | Ground         |

| 1   | Input          |

| 1/0 | Input/Output   |

| NC  | No Connect     |

| 0   | Output         |

| ŌĒ  | Output Enable  |

| Vcc | Supply Voltage |

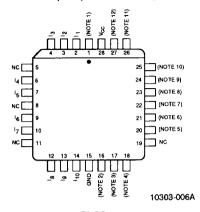

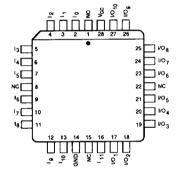

### PLCC (except AmPAL20L10)

PLCC AmPAL20L10 only

10303-007A

10303-008A

Note:

Pin 1 is marked for orientation.

www.DataSheet4U.com

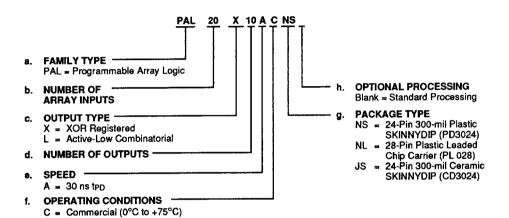

### **ORDERING INFORMATION**

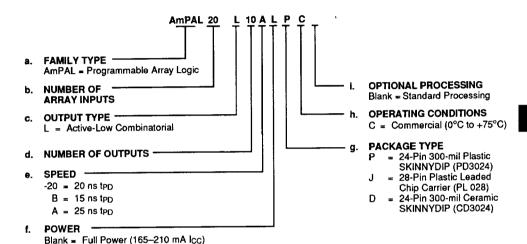

# **Commercial Products (MMI Marking Only)**

AMD commercial programmable logic products are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

- Family Type

- b. Number of Array Inputs

- **Output Type**

- d. Number of Outputs

- e. Speed

- **Operating Conditions**

- g. Package Type

- h. Optional Processing

| Valid Combinations |           |  |

|--------------------|-----------|--|

| PAL20L10A          |           |  |

| PAL20X10A          | CNS, CNL, |  |

| PAL20X8A           | CNS, CNL, |  |

| PAL20X4A           |           |  |

### Valid Combinations

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, and to check on newly released combinations.

Note: Marked with MMI logo.

# ORDERING INFORMATION Commercial Products (AMD Marking Only)

AMD commercial programmable logic products are available with several ordering options. The order number (Valid

Combination) is formed by a combination of:

- a. Family Type

- b. Number of Array Inputs c. Output Type

- d. Number of Outputs

- e. Speed

- f. Power

- g. Package Type

- h. Operating Conditions

- i. Optional Processing

| Valid Combinations |               |               |  |  |

|--------------------|---------------|---------------|--|--|

| AmPAL20L10         | B, -20,<br>AL | PC, JC,<br>DC |  |  |

L = Low Power (105 mA lcc)

### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, and to check on newly released combinations.

Note: Marked with AMD logo.

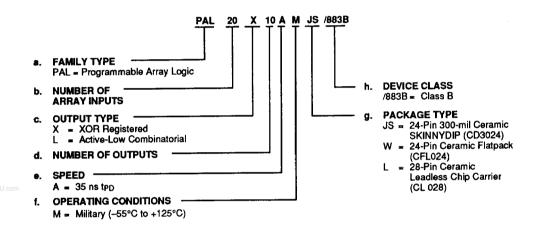

### **ORDERING INFORMATION**

### **APL Products**

AMD programmable logic products for Aerospace and Defense applications are available with several ordering options. APL (Approved Products List) products are fully compliant with MIL-STD-883 requirements. The order number (Valid Combination) is formed by a combination of:

- a. Family Type

- b. Number of Array Inputs

- c. Output Type

- d. Number of Outputs

- e. Speed

- f. Operating Conditions

- g. Package Type

- h. Device Class

| Valid Co  | mbinations          |

|-----------|---------------------|

| PAL20L10A |                     |

| PAL20X10A | MJS/883B,           |

| PAL20X8A  | MW/883B,<br>ML/883B |

| PAL20X4A  |                     |

### Valid Combinations

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

Note: Marked with MMI logo.

### **Group A Tests**

Group A Tests consist of Subgroups: 1, 2, 3, 7, 8, 9, 10, 11.

### Military Burn-In

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Methods 1015, Conditions A through E. Test conditions are selected at AMD's option.

### **FUNCTIONAL DESCRIPTION**

Four different devices are available in the 20X10 Series, including both registered and combinatorial devices. All parts are produced with a fuse link at each input to the AND gate array, and connections may be selectively removed by applying appropriate voltages to the circuit. Utilizing an easily-implemented programming algorithm, these products can be rapidly programmed to any customized pattern. Information on approved programmers can be found in the Programmer Reference Guide. Extra test words are pre-programmed during manufacturing to ensure extremely high field programming yields, and provide extra test paths to achieve excellent parametric correlation.

### Variable Input/Output Pin Ratio

The registered devices have ten dedicated input lines, and each combinatorial output is an I/O pin. The 20L10 has twelve dedicated input lines, and only eight of the ten combinatorial outputs are I/O pins. Buffers for device inputs have complementary outputs to provide user-programmable input signal polarity. Unused input pins should be tied to  $V_{\rm CC}$  or GND.

### **Programmable Three-State Outputs**

Each output has a three-state output buffer with three-state control. On combinatorial outputs, a product term controls the buffer, allowing enable and disable to be a function of any product of device inputs or output feedback. The combinatorial output provides a bidirectional I/O pin, and may be configured as a dedicated input if the buffer is always disabled. On registered outputs, an input pin controls the enabling of the three-state outputs.

### Registers with Feedback

Registered outputs are provided for data storage and synchronization. Registers are composed of D-type flip-flops that are loaded on the LOW-to-HIGH transition of the clock input.

### **Power-Up Reset**

All flip-flops power-up to a logic LOW for predictable system initialization. Outputs of the PAL20X10A Series will be HIGH due to the active-low outputs. The  $V_{\rm CC}$  rise must be monotonic and the reset delay time is 1000 ns maximum.

### Register Preload

The register on the PAL20X10A Series can be preloaded from the output pins to facilitate functional testing of complex state machine designs. This feature allows direct loading of arbitrary states, making it unnecessary to cycle through long test vector sequences to reach a desired state. In addition, transitions from illegal states can be verified by loading illegal states and observing proper recovery.

### **Security Fuse**

After programming and verification, a PAL20X10 Series design can be secured by programming the security fuse. Once programmed, this fuse defeats readback of the internal programmed pattern by a device programmer, securing proprietary designs from competitors. When the security fuse is programmed, the array will read as if every fuse is programmed.

### **Pinouts**

All members of the PAL20X10 Family have the same SKINNYDIP pinouts independent of technology, performance, and operating conditions. Because the 24-pin SKINNYDIP requires four no-connects when mapped into the 28-pin PLCC/LCC packages, the PLCC/LCC pinouts can vary.

Two different PLCC pinouts are offered. The AmPAL20L10 and all future devices will follow the JEDEC electronics committee's standard pinout ("JEDEC pinout") with no-connects on pins 1, 8, 15, and 22. The older PAL20X10A Series devices retain their original pinouts, with no-connects on pins 5, 8, 11, and 19.

A different LCC pinout is offered for military products. The older PAL20X10A Series devices retain their original pinouts, with no-connects on pins 4, 11, 18, and 25.

| Series                               | Com'l<br>PLCC<br>No-connects | Mil<br>LCC<br>No-connects |

|--------------------------------------|------------------------------|---------------------------|

| AmPAL20L10<br>B/-20/AL               | 1, 8, 15, 22<br>(JEDEC)      | N/A                       |

| PAL20X10A Series<br>(inc. PAL20L10A) | 5, 8, 11, 19                 | 4, 11, 18, 25             |

### **Quality and Testability**

The PAL20X10 Series offers a very high level of built-in quality. Extra programmable fuses provide a means of verifying performance of all AC and DC parameters. In addition, this verifies complete programmability and functionality of the device to provide the highest programming yields and post-programming functional vields in the industry.

### Technology

The PAL20X10A Series is fabricated with AMD's advanced junction-isolated bipolar process. The array connections are formed with proven TiW fuses for reliable operation.

The AmPAL20L10 is fabricated with the IMOX<sup>™</sup> oxideisolated bipolar process using proven PtSi fuses.

www.DataSheet4U.com

# LOGIC DIAGRAM SKINNYDIP (PLCC, PAL20L10A only) Pinouts See Connection Diagrams for LCC and AmPAL20L10 PLCC Pinouts

10303-009A

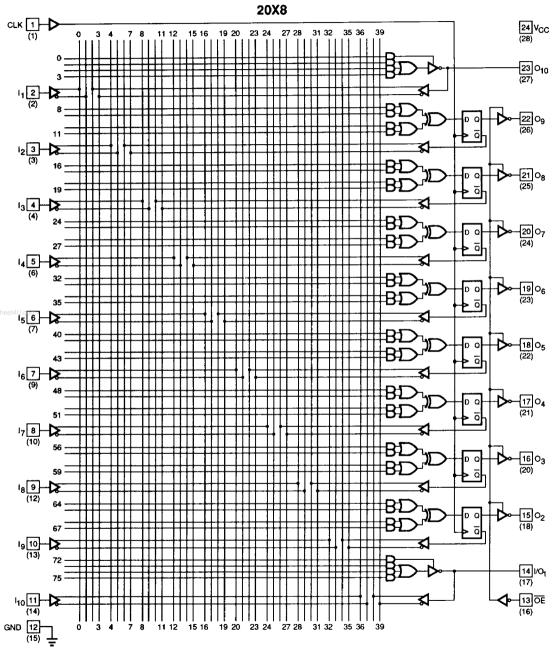

# LOGIC DIAGRAM SKINNYDIP (PLCC) Pinouts See Connection Diagrams for LCC Pinout

10303-010A

# LOGIC DIAGRAM SKINNYDIP (PLCC) Pinouts See Connection Diagrams for LCC Pinout

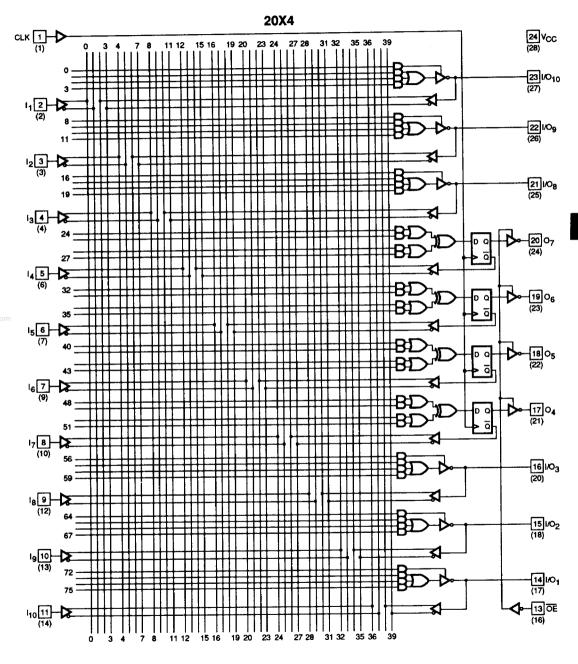

10303-011A

# LOGIC DIAGRAM SKINNYDIP (PLCC) Pinouts See Connection Diagrams for LCC Pinout

10303-012A

2-199

### **ABSOLUTE MAXIMUM RATINGS**

-65°C to +150°C Storage Temperature

Ambient Temperature with

Power Applied

-55°C to +125°C

Supply Voltage with

Respect to Ground

-0.5 V to +7.0 V

DC Input Voltage

-1.5 V to V<sub>CC</sub> + 0.5 V

DC Output or I/O Pin Voltage

-0.5 V to  $V_{CC} + 0.5 \text{ V}$

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### OPERATING RANGES

Commercial (C) Devices

Ambient Temperature (TA)

Operating in Free Air

Supply Voltage (Vcc)

with Respect to Ground

+4.75 V to +5.25 V

0°C to +75°C

Operating ranges define those limits between which the func-

tionality of the device is guaranteed.

### DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                   |                            | Min. | Max. | Unit |

|---------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------|------|------|------|

| V <sub>OH</sub>     | Output HIGH Voltage                      | $i_{OH} = -3.2 \text{ mA}$ $V_{IN} = V_{IH} \text{ or } V_{CC} = \text{Min.}$                                     | V <sub>IL</sub>            | 2.4  |      | >    |

| Vol                 | Output LOW Voltage                       | $I_{OL} = 24 \text{ mA}$ $V_{IN} = V_{IH} \text{ or } V_{CC} = \text{Min.}$                                       | · V <sub>IL</sub>          |      | 0.5  | >    |

| VIH                 | Input HIGH Voltage                       | Guaranteed Input Logical F<br>Voltage for all Inputs (Note                                                        |                            | 2.0  |      | V    |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical L<br>Voltage for all Inputs (Note                                                        |                            |      | 0.8  | ٧    |

| V <sub>I</sub>      | Input Clamp Voltage                      | $I_{IN} = -18$ mA, $V_{CC} = Min$ .                                                                               |                            |      | -1.5 | ٧    |

| H-                  | Input HIGH Current                       | V <sub>IN</sub> = 2.4 V, V <sub>CC</sub> = Max. (N                                                                | ote 2)                     |      | 25   | μΑ   |

| l <sub>L</sub>      | Input LOW Current                        | V <sub>IN</sub> = 0.4 V, V <sub>CC</sub> = Max. (No                                                               | ote 2)                     |      | -250 | μΑ   |

| l <sub>i</sub>      | Maximum Input Current                    | $V_{IN} = 5.5 \text{ V}, V_{CC} = \text{Max}.$                                                                    |                            |      | 100  | μΑ   |

| lozh                | Off-State Output Leakage<br>Current HIGH | V <sub>OUT</sub> = 2.4 V, V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 2) |                            |      | 100  | μА   |

| lozi                | Off-State Output Leakage<br>Current LOW  | Vout = 0.4 V, Vcc = Max.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 2)                         |                            |      | -100 | μА   |

| Isc                 | Output Short-Circuit Current             | $V_{OUT} = 0.5 \text{ V}, V_{CC} = \text{Max}.$ (Note 3)                                                          |                            | -30  | -130 | mA   |

| lcc                 | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open<br>(lout = 0 mA), V <sub>CC</sub> = Max.                                      | 20X10A,<br>20X8A,<br>20X4A |      | 180  | mA   |

|                     |                                          |                                                                                                                   | 20L10A                     |      | 165  |      |

- 1. These are absolute values with respect to device ground and all overshoots due to system and/or tester noise are included.

- 2. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

- 3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second. Vout = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

# SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 1)

| Parameter<br>Symbol | Parameter Description              |                                                |               | Min.           | Max. | Unit |     |

|---------------------|------------------------------------|------------------------------------------------|---------------|----------------|------|------|-----|

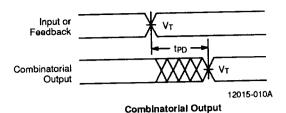

| tPD                 | Input or Feedba<br>Combinatorial ( |                                                | ck to         |                |      | 30   | ns  |

| ts                  | Setup Time from                    | m Input or Feedback to                         | Clock         |                | 30   |      | ns  |

| tн                  | Hold Time                          |                                                | or Feedback   |                | 0    |      | ns  |

| tco                 | Clock to Output                    | or Feedback                                    |               |                |      | 15   | ns  |

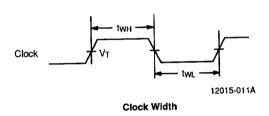

| twL                 |                                    | LOW                                            |               | 20X10A, 20X8A, | 25   |      | ns  |

| twn                 | Clock Width                        | HIGH                                           |               | 20X4           | 15   |      | ns  |

|                     | Maximum                            | External Feedback                              | 1/(ts + tco)  |                | 22.2 |      | MHz |

| 1 <sub>MAX</sub>    | Frequency<br>(Note 2)              | No Feedback                                    | 1/(tw+ + twL) |                | 25   |      | MHz |

| t <sub>PZX</sub>    | OE to Output E                     | nable                                          |               |                |      | 20   | ns  |

| texz                | OE to Output D                     |                                                |               |                |      | 20   | ns  |

| tea.                |                                    | ut to Output Enable Using Product Term Control |               | 20L10A, 20X8A, |      | 30   | ns  |

| ter                 |                                    | Disable Using Product                          |               | 20X4A          |      | 30   | ns  |

- See Switching Test Circuit for test conditions.

These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where frequency may be affected.

### ABSOLUTE MAXIMUM RATINGS

-65°C to +150°C Storage Temperature

Ambient Temperature

with Power Applied

-55°C to +125°C

Supply Voltage with

Respect to Ground

-0.5 V to +7.0 V

DC Input Voltage

-1.5 V to 5.5 V

DC Output or I/O Pin Voltage

-0.5 V to 5.5 V

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ. Absolute Maximum Ratings are for system design reference; parameters given are not tested.

### OPERATING RANGES

Military (M) Devices (Note 1)

Ambient Temperature (T<sub>A</sub>)

Operating in Free Air

-55°C Min.

Operating Case (Tc)

Temperature

125°C Max.

Supply Voltage (Vcc)

with Respect to Ground +4.50 V to +5.50 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

#### Note:

1. Military products are tested at T<sub>C</sub> = +25°C, +125°C, and -55°C per MIL-STD-883.

### DC CHARACTERISTICS over MILITARY operating ranges unless otherwise specified (Note 2)

| Parameter<br>Symbol            | Parameter Description                    | Test Conditions                                                                                                   | Min. | Max. | Unit |

|--------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>OH</sub>                | Output HIGH Voltage                      | $I_{OH} = -2 \text{ mA}$ $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$V_{CC} = \text{Min.}$                           | 2.4  |      | >    |

| Vol                            | Output LOW Voltage                       | $I_{OL} = 12 \text{ mA}$ $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$V_{CC} = \text{Min.}$                           |      | 0.5  | ٧    |

| V <sub>IH</sub>                | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 3)                                                  | 2.0  |      | ٧    |

| <sup>com</sup> V <sub>IL</sub> | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 3)                                                   |      | 0.8  | ٧    |

| V <sub>I</sub>                 | Input Clamp Voltage                      | I <sub>IN</sub> = -18 mA, V <sub>CC</sub> = Min.                                                                  |      | -1.5 | V    |

| l <sub>ін</sub>                | Input HIGH Current                       | V <sub>IN</sub> = 2.4 V, V <sub>CC</sub> = Max. (Note 4)                                                          |      | 25   | μА   |

| l <sub>iL</sub>                | Input LOW Current                        | V <sub>IN</sub> = 0.4 V, V <sub>CC</sub> = Max. (Note 4)                                                          |      | -250 | μА   |

| l <sub>l</sub>                 | Maximum Input Current                    | V <sub>IN</sub> = 5.5 V, V <sub>CC</sub> = Max.                                                                   |      | 1    | mΑ   |

| lozh                           | Off-State Output Leakage<br>Current HIGH | V <sub>OUT</sub> = 2.4 V, V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 4) |      | 100  | μА   |

| lozL                           | Off-State Output Leakage<br>Current LOW  | V <sub>OUT</sub> = 0.4 V, V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 4) |      | -100 | μА   |

| Isc                            | Output Short-Circuit Current             | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max. (Note 5)                                                         | -30  | -130 | mA   |

| lcc                            | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open 20X8A, (I <sub>OUT</sub> = 0 mA), V <sub>CC</sub> = Max. 20X4A                | ١,   | 180  | mA   |

|                                |                                          | 20L10A                                                                                                            |      | 165  |      |

- 2. For APL Products, Group A, Subgroups 1, 2, and 3 are tested per MIL-STD-883, Method 5005, unless otherwise noted.

- 3. Vil and ViH are input conditions of output tests and are not themselves directly tested. ViL and ViH are absolute voltages with respect to device ground and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

- 4. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

- 5. Not more than one output should be shorted at a time. Duration of the short-circuit should not exceed one second. V<sub>OUT</sub> = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

# **SWITCHING CHARACTERISTICS over MILITARY operating ranges (Note 1)**

| Parameter<br>Symbol | Parameter Des                      | Parameter Description        |               |                         | Min. | Max. | Unit |

|---------------------|------------------------------------|------------------------------|---------------|-------------------------|------|------|------|

| tPD                 | Input or Feedba<br>Combinatorial C |                              |               | 20L10A, 20X8A,<br>20X4A |      | 35   | ns   |

| ts                  | Setup Time from                    | n Input or Feedback to       | Clock         |                         | 40   |      | ns   |

| tн                  | Hold Time                          |                              |               |                         | 0    |      | ns   |

| tco                 | Clock to Output                    | or Feedback                  |               |                         |      | 25   | ns   |

| twL                 |                                    | LOW                          |               | 20X10A, 20X8A,          | 35   |      | ns   |

| twn                 | Clock Width                        | HIGH                         |               | 20X4A                   | 20   |      | ns   |

|                     | Maximum                            | External Feedback            | 1/(ts + tco)  |                         | 15.4 |      | MHz  |

| <b>f</b> MAX        | Frequency<br>(Note 2)              | No Feedback                  | 1/(tw+ + twL) |                         | 18.2 |      | MHz  |

| tpzx                | OE to Output Er                    | nable (Note 3)               |               |                         |      | 25   | ns   |

| texz                | OE to Output Di                    | sable (Note 3)               | ****          |                         |      | 25   | ns   |

| tea                 | Input to Output<br>Term Control (N | Enable Using Product lote 3) |               | 20L10A, 20X8A,          |      | 35   | ns   |

| ter                 |                                    | Disable Using Product        |               | 20X4A                   |      | 35   | ns   |

- See Switching Test Circuit for test conditions. For APL products Group A, Subgroups 9, 10, and 11 are tested per MIL-STD-883, Method 5005, unless otherwise noted.

- 2. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where frequency may be affected.

- These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where these parameters may be affected.

### ABSOLUTE MAXIMUM RATINGS

-65°C to +150°C Storage Temperature

Ambient Temperature with

Power Applied

-55°C to +125°C

Supply Voltage with

Respect to Ground -0.5 V to +7.0 V

DC Input Voltage -0.5 V to +5.5 V

DC Output or I/O Pin Voltage -0.5 V to Vcc Max.

-30 mA to +5 mA DC Input Current

ity. Programming conditions may differ.

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliabil-

### **OPERATING RANGES**

Commercial (C) Devices

Ambient Temperature (TA)

Operating in Free Air

0°C to +75°C

Supply Voltage (Vcc)

with Respect to Ground

+4.75 V to +5.25 V

Operating ranges define those limits between which the func-

tionality of the device is guaranteed.

### DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                   | Min. | Max.              | Unit     |

|---------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|-------------------|----------|

| VoH                 | Output HIGH Voltage                      | $I_{OH} = -3.2 \text{ mA}$ $V_{IN} = V_{IH} \text{ or } V_{IL}$ $V_{CC} = \text{Min.}$                            | 2.4  |                   | <b>V</b> |

| Vol                 | Output LOW Voltage                       | $I_{OL} = 24 \text{ mA}$ $V_{IN} = V_{IH} \text{ or } V_{IL}$ $V_{CC} = \text{Min.}$                              |      | 0.5               | ٧        |

| V <sub>IH</sub>     | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                                  | 2.0  | 5.5               | V        |

| V <sub>IL</sub>     | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                                   |      | 0.8               | V        |

| Vi                  | Input Clamp Voltage                      | $I_{IN} = -18$ mA, $V_{CC} = Min$ .                                                                               |      | -1.2              | ٧        |

| tн                  | Input HIGH Current                       | V <sub>IN</sub> = 2.7 V, V <sub>CC</sub> = Max. (Note 2)                                                          |      | 25                | μΑ       |

| lıL                 | Input LOW Current                        | V <sub>IN</sub> = 0.4 V, V <sub>CC</sub> = Max. (Note 2)                                                          |      | -100              | μA       |

| lı                  | Maximum Input Current                    | V <sub>IN</sub> = 5.5 V, V <sub>CC</sub> = Max.                                                                   |      | 1                 | mA       |

| lozн                | Off-State Output Leakage<br>Current HIGH | $V_{OUT} = 2.7 \text{ V}, V_{CC} = \text{Max}.$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 2)}$          |      | 100               | μА       |

| lozL                | Off-State Output Leakage<br>Current LOW  | V <sub>OUT</sub> = 0.4 V, V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 2) |      | -100              | μА       |

| Isc                 | Output Short-Circuit Current             | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max. (Note 3)                                                         | -30  | 90                | mA       |

| lcc                 | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open<br>(I <sub>OUT</sub> = 0 mA) V <sub>CC</sub> = Max. 20L10AL                   |      | 210<br>165<br>105 | mA       |

- 1. These are absolute values with respect to device ground and all overshoots due to system and/or tester noise are included.

- 2. I/O pin leakage is the worst case of IIL and IOZE (or IIH and IOZH).

- 3. Not more than one output should be shorted at a time. Duration of the short-circuit should not exceed one second. Vout = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

## **CAPACITANCE (Note 1)**

| Parameter<br>Symbol | Parameter Descri  | ption                | Test Conditions          | 3                                                    | Тур.    | Unit |

|---------------------|-------------------|----------------------|--------------------------|------------------------------------------------------|---------|------|

| CIN                 | Input Capacitance | Pins 1, 13<br>Others | $V_{IN} = 2.0 \text{ V}$ | $V_{CC} = 5.0 \text{ V}$ $T_A = +25^{\circ}\text{C}$ | 11<br>6 | ρF   |

| Соит                | Output Capacitanc | e                    | V <sub>OUT</sub> = 2.0 V | f = 1 MHz                                            | 9       |      |

### Note:

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

# **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)**

| Parameter<br>Symbol |                                                       | 20L10B |      | 20L10-20 |      | 20L10AL |      |      |

|---------------------|-------------------------------------------------------|--------|------|----------|------|---------|------|------|

|                     | Parameter Description                                 | Min.   | Max. | Min.     | Max. | Min.    | Max. | Unit |

| t <sub>PD</sub>     | Input or Feedback to<br>Combinatorial Output          |        | 15   |          | 20   |         | 25   | ns   |

| tea                 | Input to Output Enable Using<br>Product Term Control  |        | 18   |          | 20   |         | 25   | ns   |

| ten                 | Input to Output Disable Using<br>Product Term Control |        | 15   |          | 20   |         | 25   | ns   |

### Notes:

2. See Switching Test Circuit for test conditions.

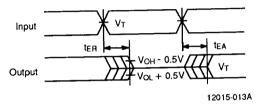

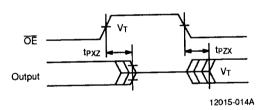

# **SWITCHING WAVEFORMS**

input or Feedback Clock Registered Output 12015-012A

Registered Output

Input to Output Disable/Enable

OE to Output Disable/Enable

- 1.  $V_T = 1.5 V$

- Input pulse amplitude 0 V to 3.0 V.

Input rise and fall times 2–5 ns typical.

### **KEY TO SWITCHING WAVEFORMS**

| WAVEFORM        | INPUTS                                 | OUTPUTS                                             |

|-----------------|----------------------------------------|-----------------------------------------------------|

|                 | Must be<br>Steady                      | Will be<br>Steady                                   |

|                 | May<br>Change<br>from H to L           | Will be<br>Changing<br>from H to L                  |

|                 | May<br>Change<br>from L to H           | Will be<br>Changing<br>from L to H                  |

|                 | Don't Care;<br>Any Change<br>Permitted | Changing,<br>State<br>Unknown                       |

| <b>&gt;&gt;</b> | Does Not<br>Apply                      | Center<br>Line is High-<br>Impedance<br>"Off" State |

KS000010-PAL

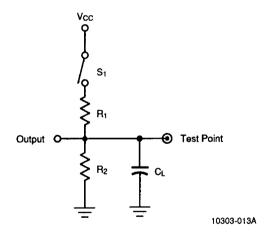

### **SWITCHING TEST CIRCUIT**

|                                    | S <sub>1</sub>               | CL    | Commercial     |                | Military       |                | Measured                                                                     |  |

|------------------------------------|------------------------------|-------|----------------|----------------|----------------|----------------|------------------------------------------------------------------------------|--|

| Specification                      |                              |       | R <sub>1</sub> | R <sub>2</sub> | R <sub>1</sub> | R <sub>2</sub> | Output Value                                                                 |  |

| tpp, tco                           | Closed                       |       |                |                |                |                | 1.5 V                                                                        |  |

| tpzx, tea                          | Z → H: Open<br>Z → L: Closed | 50 pF | 200 Ω          | 390 Ω          | 390 Ω          | 750 Ω          | 1.5 V                                                                        |  |

| t <sub>PXZ</sub> , t <sub>ER</sub> | H → Z: Open<br>L → Z: Closed | 5 pF  |                |                |                |                | $H \rightarrow Z$ : $V_{OH} - 0.5 V$<br>$L \rightarrow Z$ : $V_{OL} + 0.5 V$ |  |

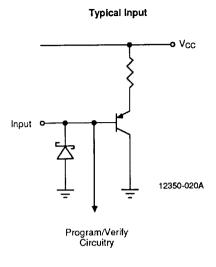

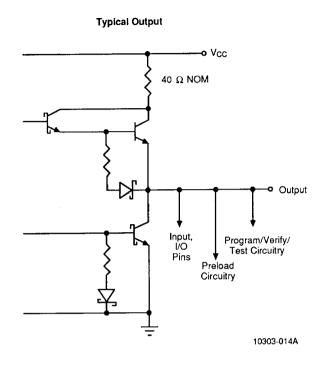

# INPUT/OUTPUT EQUIVALENT SCHEMATICS

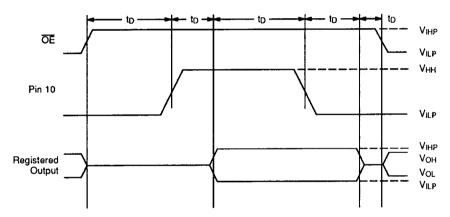

### **OUTPUT REGISTER PRELOAD**

The preload function allows the register to be loaded from the output pins. This feature aids functional testing of sequential designs by allowing direct setting of output states. The procedure for preloading follows.

- 1. Raise Vcc to Vcch.

- 2. Set  $\overline{OE}$  to  $V_{IHP}$  to disable output registers.

- 3. Raise pin 10 to V<sub>HH</sub> to enter preload mode.

- 4. Apply either  $V_{IHP}$  or  $V_{ILP}$  to all registered outputs. Use  $V_{IHP}$  to preload a HIGH in the flip-flop; use  $V_{ILP}$  to

- preload a LOW in the flip-flop. Leave combinatorial outputs floating.

- 5. Lower pin 10 to VILP.

- 6. Remove VILP/VIHP from all registered output pins.

- 7. Lower OE to VILP to enable the output registers.

- Verify V<sub>OL</sub>/V<sub>OH</sub> at all registered output pins. Note that because of the output inverter, a register that has been preloaded HIGH will provide a LOW at the output.

| Parameter<br>Symbol | Parameter Description       | Min. | Rec. | Max. | Unit |

|---------------------|-----------------------------|------|------|------|------|

| V <sub>HH</sub>     | Super-level input voltage   | 19   | 20   | 21   | ٧    |

| V <sub>ILP</sub>    | Low-level input voltage     | 0    | 0    | 0.5  | ٧    |

| V <sub>IHP</sub>    | High-level input voltage    | 2.4  | 5.0  | 5.5  | ٧    |

| Vccн                | Power supply during preload |      | 4.5  |      | ٧    |

| t <sub>D</sub>      | Delay time                  | 100  | 200  | 1000 | ns   |

10303-015A

**Output Register Preload Waveform**

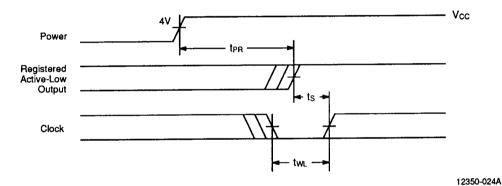

### **POWER-UP RESET**

The power-up reset feature ensures that all flip-flops will be reset to LOW after the device has been powered up. The output state will be HIGH due to the inverting output buffer. This feature is valuable in simplifying state machine initialization. A timing diagram and parameter table are shown below. Due to the synchronous operation of the power-up reset and the wide range of ways Vcc

can rise to its steady state, two conditions are required to ensure a valid power-up reset. These conditions are:

- 1. The V<sub>CC</sub> rise must be monotonic.

- Following reset, the clock input must not be driven from LOW to HIGH until all applicable input and feedback setup times are met.

| Parameter<br>Symbol | Parameter Description        | Max.          | Unit            |  |  |

|---------------------|------------------------------|---------------|-----------------|--|--|

| ten                 | Power-up Reset Time          | 1000          | ns              |  |  |

| ts                  | Input or Feedback Setup Time | See Switching |                 |  |  |

| twL                 | Clock Width LOW              | Characterist  | Characteristics |  |  |

Power-Up Reset Waveform