## OCTAL BUS TRANSCEIVER/REGISTER WITH 3 STATE OUTPUTS

- HIGH SPEED:

- f<sub>MAX</sub> = 60 MHz (TYP.) at V<sub>CC</sub> = 4.5V ■ LOW POWER DISSIPATION:

- LOW POWER DISSIPATION:  $I_{CC} = 4\mu A(MAX.) \text{ at } T_A=25^{\circ}C$

- COMPATIBLE WITH TTL OUTPUTS :

V<sub>IH</sub> = 2V (MIN.) V<sub>IL</sub> = 0.8V (MAX)

- SYMMETRICAL OUTPUT IMPEDANCE:

|I<sub>OH</sub>| = I<sub>OL</sub> = 6mA (MIN)

- BALANCED PROPAGATION DELAYS: t<sub>PLH</sub> ≅ t<sub>PHL</sub>

- PIN AND FUNCTION COMPATIBLE WITH 74 SERIES 646

#### DESCRIPTION

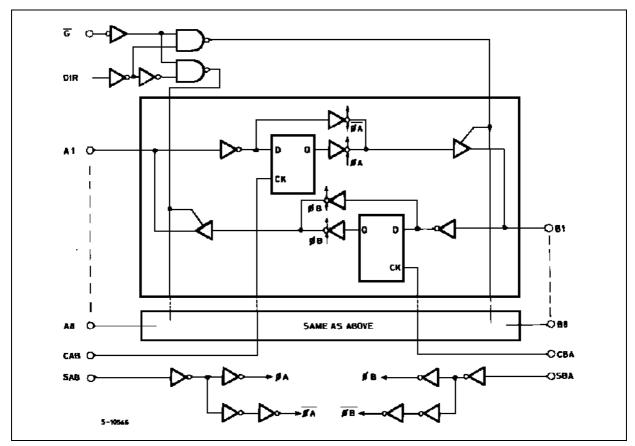

The 74HCT646 is an advanced high-speed CMOS OCTAL BUS TRANSCEIVER AND REGISTER (3-STATE) fabricated with silicon gate  $C^2$ MOS technology.

This device consists of bus transceiver circuits with 3 state, D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal registers. Data on the A or B bus will be clocked into register on the low to high transition of the appropriate clock pin (Clock AB or Clock BA). Enable (G) and direction (DIR) pins are provided to control the transceiver functions. In the transceiver mode, data present at the high-impedance port may be stored in either register or in both. The select controls (Select AB

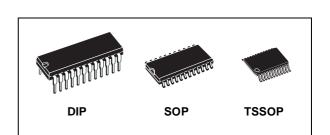

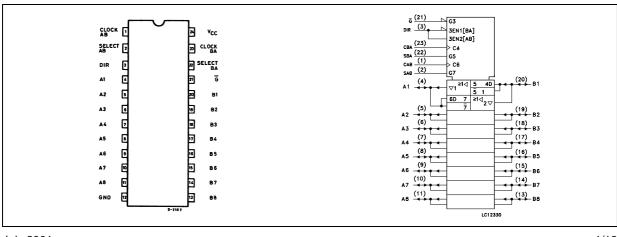

#### PIN CONNECTION AND IEC LOGIC SYMBOLS

#### **ORDER CODES**

| PACKAGE | TUBE         | T & R           |

|---------|--------------|-----------------|

| DIP     | M74HCT646B1R |                 |

| SOP     | M74HCT646M1R | M74HCT646RM13TR |

| TSSOP   |              | M74HCT646TTR    |

select BA) can multiplex stored and real time (transparent mode) data. The direction control determines which bus will receive data when enable  $\overline{G}$  is active (low). In the isolation mode (enable  $\overline{G}$  high), "A" data may be stored in one register and/or "B" data may be stored in the other register. When an output function is disabled, the input function is still enabled and may be used to store and transmit data. Only one of the two buses, A or B, may be driven at a time.

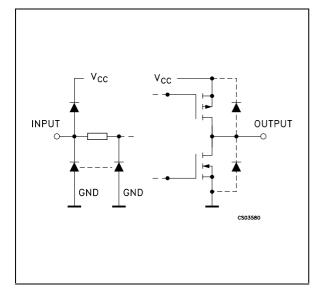

All inputs are equipped with protection circuits against static discharge and transient excess voltage.

#### INPUT AND OUTPUT EQUIVALENT CIRCUIT

**PIN DESCRIPTION**

| PIN No                               | SYMBOL          | NAME AND FUNCTION                                |

|--------------------------------------|-----------------|--------------------------------------------------|

| 1                                    | CLOCK AB        | A to B Clock Input (LOW to HIGH, Edge-Triggered) |

| 2                                    | SELECT AB       | Select A to B Source Input                       |

| 3                                    | GAB             | Direction Control Input                          |

| 4, 5, 6, 7, 8,<br>9, 10, 11          | A1 to A8        | A Data Inputs/Outputs                            |

| 20, 19, 18,<br>17, 16, 15,<br>14, 13 | B1 to B8        | B Data Inputs/Outputs                            |

| 21                                   | G               | Output Enable Input<br>(Active LOW)              |

| 22                                   | SELECT BA       | Select B to A Source Input                       |

| 23                                   | CLOCK BA        | B to A Clock Input (LOW to HIGH, Edge Triggered) |

| 12                                   | GND             | Ground (0V)                                      |

| 24                                   | V <sub>CC</sub> | Positive Supply Voltage                          |

#### **TRUTH TABLE**

| G       | DIR | CAB | СВА | SAB | SBA | Α       | В       | FUNCTION                                                                                                                                           |

|---------|-----|-----|-----|-----|-----|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|         |     |     |     |     |     | INPUTS  | INPUTS  | Both the A bus and the B bus are inputs                                                                                                            |

|         |     | Х   | Х   | Х   | Х   | Z       | Z       | The Output functions of the A and B bus are disabled                                                                                               |

| Н       | Х   |     | Ц   | х   | х   | INPUTS  | INPUTS  | Both the A and B bus are used for inputs to the internal flip-flops. Data at the bus will be stored on low to high transition of the clock inputs. |

|         |     |     |     |     |     | INPUTS  | OUTPUTS | The A bus are inputs and the B bus are outputs                                                                                                     |

|         |     | х   | Х*  | L   | х   | L       | L       | The data at the A bus are displayed at the B bus                                                                                                   |

|         |     | ^   | ^   | L   | ^   | Н       | Н       | The data at the A bus are displayed at the B bus                                                                                                   |

|         |     |     |     |     |     | L       | L       | The data at the A bus are displayed at the B bus. The                                                                                              |

| L       | н   |     | Х*  | L   | Х   | Н       | Н       | data of the A bus are stored to internal flip-flop on low to high transition of the clock pulse                                                    |

|         |     | х   | Х*  | н   | х   | Х       | Qn      | The data stored to the internal flip-flop are displayed at the B bus.                                                                              |

|         |     |     |     |     |     | L       | L       | The data at the A bus are stored to the internal flip-flop                                                                                         |

|         |     |     | Х*  | Н   | Х   | Н       | Н       | on low to high transition of the clock pulse. The states of the internal flip-flops output directly to the B bus.                                  |

|         |     |     |     |     |     | OUTPUTS | INPUTS  | The B bus are inputs and the A bus are outputs.                                                                                                    |

|         |     | Х*  | х   | х   | L   | L       | L       | The data at the B bus are displayed at the A bus                                                                                                   |

|         |     | ^   | ^   | ^   | L   | Н       | Н       | The data at the B bus are displayed at the A bus                                                                                                   |

|         |     |     |     |     |     | L       | L       | The data at the B bus are displayed at the A bus. The                                                                                              |

| L       | L   | Х*  |     | Х   | L   | Н       | Н       | data of the B bus are stored to the internal flip-flop on low to high transition of the clock pulse.                                               |

|         |     | Х*  | х   | х   | Н   | Qn      | Х       | The data stored to the internal flip-flops are displayed at the A bus                                                                              |

|         |     |     |     |     |     | L       | L       | The data at the B bus are stored to the internal flip-flop                                                                                         |

| X · Don |     | Х*  |     | Х   | Н   | Н       | Н       | on low to high transition of the clock pulse. The states of the internal flip-flops output directly to the A bus.                                  |

X : Don't Care Z : High Impedance Qn : The data stored to the internal flip-flops by most recent low to high transition of the clock inputs \* : The data at the A and B bus will be stored to the internal flip-flops on every low to high transition of the clock inputs.

#### LOGIC DIAGRAM

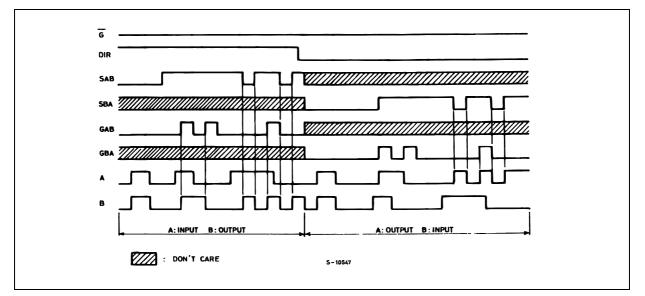

#### **TIMING CHART**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                              | Parameter                            | Value                         | Unit |

|-------------------------------------|--------------------------------------|-------------------------------|------|

| V <sub>CC</sub>                     | Supply Voltage                       | -0.5 to +7                    | V    |

| VI                                  | DC Input Voltage                     | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| Vo                                  | DC Output Voltage                    | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| Ι <sub>ΙΚ</sub>                     | DC Input Diode Current               | ± 20                          | mA   |

| I <sub>OK</sub>                     | DC Output Diode Current              | ± 20                          | mA   |

| Ι <sub>Ο</sub>                      | DC Output Current                    | ± 35                          | mA   |

| I <sub>CC</sub> or I <sub>GND</sub> | DC V <sub>CC</sub> or Ground Current | ± 70                          | mA   |

| PD                                  | Power Dissipation                    | 500(*)                        | mW   |

| T <sub>stg</sub>                    | Storage Temperature                  | -65 to +150                   | °C   |

| ΤL                                  | Lead Temperature (10 sec)            | 300                           | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied (\*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°C

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                          | Parameter                                          | Value                | Unit |

|---------------------------------|----------------------------------------------------|----------------------|------|

| V <sub>CC</sub>                 | Supply Voltage                                     | 4.5 to 5.5           | V    |

| VI                              | Input Voltage                                      | 0 to V <sub>CC</sub> | V    |

| Vo                              | Output Voltage                                     | 0 to V <sub>CC</sub> | V    |

| T <sub>op</sub>                 | Operating Temperature                              | -55 to 125           | °C   |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise and Fall Time ( $V_{CC}$ = 4.5 to 5.5V) | 0 to 500             | ns   |

#### DC SPECIFICATIONS

**~7**

|                  |                                             | ٦                | Test Condition                                                                                      | Value       |                       |             |             |             |             |              |    |

|------------------|---------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|-------------|-----------------------|-------------|-------------|-------------|-------------|--------------|----|

| Symbol           | Parameter                                   | v <sub>cc</sub>  |                                                                                                     | т           | T <sub>A</sub> = 25°C |             |             | -40 to 85°C |             | -55 to 125°C |    |

|                  |                                             | (V)              |                                                                                                     | Min.        | Тур.                  | Max.        | Min.        | Max.        | Min.        | Max.         |    |

| V <sub>IH</sub>  | High Level Input<br>Voltage                 | 4.5<br>to<br>5.5 |                                                                                                     | 2.0         |                       |             | 2.0         |             | 2.0         |              | V  |

| V <sub>IL</sub>  | Low Level Input<br>Voltage                  | 4.5<br>to<br>5.5 |                                                                                                     |             |                       | 0.8         |             | 0.8         |             | 0.8          | V  |

| V <sub>OH</sub>  | High Level Output<br>Voltage                | 4.5              | I <sub>O</sub> =-20 μA<br>I <sub>O</sub> =-6.0 mA                                                   | 4.4<br>4.18 | 4.5<br>4.31           |             | 4.4<br>4.13 |             | 4.4<br>4.10 |              | V  |

| V <sub>OL</sub>  | Low Level Output<br>Voltage                 | 4.5              | I <sub>O</sub> =20 μA<br>I <sub>O</sub> =6.0 mA                                                     |             | 0.0<br>0.17           | 0.1<br>0.26 |             | 0.1<br>0.33 |             | 0.1<br>0.40  | V  |

| I                | Input Leakage<br>Current                    | 5.5              | $V_{I} = V_{CC} \text{ or } GND$                                                                    |             |                       | ± 0.1       |             | ± 1         |             | ± 1          | μΑ |

| I <sub>OZ</sub>  | High Impedance<br>Output Leakage<br>Current | 5.5              | $V_{I} = V_{IH} \text{ or } V_{IL}$<br>$V_{O} = V_{CC} \text{ or } GND$                             |             |                       | ± 0.5       |             | ± 5         |             | ±10          | μΑ |

| Icc              | Quiescent Supply<br>Current                 | 5.5              | $V_{I} = V_{CC} \text{ or } GND$                                                                    |             |                       | 4           |             | 40          |             | 80           | μΑ |

| ΔI <sub>CC</sub> | Additional Worst<br>Case Supply<br>Current  | 5.5              | Per Input pin<br>$V_I = 0.5V$ or<br>$V_I = 2.4V$<br>Other Inputs at<br>$V_{CC}$ or GND<br>$I_O = 0$ |             |                       | 2.0         |             | 2.9         |             | 3.0          | mA |

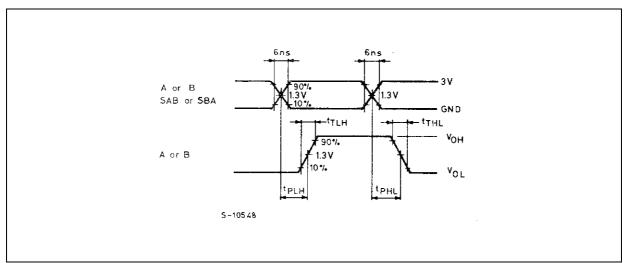

### **AC ELECTRICAL CHARACTERISTICS** ( $C_L = 50 \text{ pF}$ , Input $t_r = t_f = 6 \text{ns}$ )

|                                        |                                                            | ٦               | Test Co   | ondition                               |      |                       |          | Value |             |      |              |     |

|----------------------------------------|------------------------------------------------------------|-----------------|-----------|----------------------------------------|------|-----------------------|----------|-------|-------------|------|--------------|-----|

| Symbol                                 | Parameter                                                  | v <sub>cc</sub> | CL        |                                        | т    | T <sub>A</sub> = 25°C |          |       | -40 to 85°C |      | -55 to 125°C |     |

|                                        |                                                            | (V)             | (pF)      |                                        | Min. | Тур.                  | Max.     | Min.  | Max.        | Min. | Max.         |     |

| t <sub>TLH</sub> t <sub>THL</sub>      | Output Transition<br>Time                                  | 4.5             | 50        |                                        |      | 7                     | 12       |       | 15          |      | 19           | ns  |

| t <sub>PLH</sub> t <sub>PHL</sub>      | Propagation Delay<br>Time                                  | 4.5             | 50<br>150 |                                        |      | 20<br>25              | 30<br>38 |       | 38<br>48    |      | 48<br>60     | ns  |

| t <sub>PLH</sub> t <sub>PHL</sub>      | Propagation Delay<br>Time(CLOCK-A,B)                       | 4.5             | 50<br>150 |                                        |      | 29<br>34              | 44<br>52 |       | 55<br>65    |      | 65<br>75     | ns  |

| t <sub>PLH</sub> t <sub>PHL</sub>      | Propagation Delay<br>Time (SELECT -<br>A,B)                | 4.5             | 50<br>150 |                                        |      | 24<br>29              | 34<br>42 |       | 43<br>53    |      | 53<br>65     | ns  |

| t <sub>PZL</sub> t <sub>PZH</sub>      | High Impedance<br>Outpu <u>t E</u> nable<br>Time (G, DIR)  | 4.5             | 50<br>150 | $R_L = 1 K\Omega$<br>$R_L = 1 K\Omega$ |      | 26<br>31              | 38<br>46 |       | 48<br>58    |      | 60<br>70     | ns  |

| t <sub>PLZ</sub> t <sub>PHZ</sub>      | High Impedance<br>Outpu <u>t D</u> isable<br>Time (G, DIR) | 4.5             | 50        | $R_L = 1 \ K\Omega$                    |      | 26                    | 35       |       | 44          |      | 55           | ns  |

| f <sub>MAX</sub>                       | Maximum Clock<br>Frequency                                 | 4.5             | 50        |                                        | 31   | 55                    |          | 25    |             | 20   |              | MHz |

| t <sub>W(H)</sub><br>t <sub>W(L)</sub> | Minimum Pulse<br>Width                                     | 4.5             | 50        |                                        |      | 8                     |          | 15    |             | 19   |              | ns  |

| t <sub>s</sub>                         | Minimum Set-Up<br>Time                                     | 4.5             | 50        |                                        |      | 3                     | 10       |       | 13          |      | 13           | ns  |

| t <sub>h</sub>                         | Minimum Hold<br>Time                                       | 4.5             | 50        |                                        |      |                       | 5        |       | 5           |      | 5            | ns  |

#### **CAPACITIVE CHARACTERISTICS**

|                  |                                              | ٦                      | Test Condition Value  |      |      |             |      |              |      |      |    |

|------------------|----------------------------------------------|------------------------|-----------------------|------|------|-------------|------|--------------|------|------|----|

| Symbol           | Parameter                                    | V <sub>CC</sub><br>(V) | T <sub>A</sub> = 25°C |      |      | -40 to 85°C |      | -55 to 125°C |      | Unit |    |

|                  |                                              |                        |                       | Min. | Тур. | Max.        | Min. | Max.         | Min. | Max. |    |

| C <sub>IN</sub>  | Input Capacitance                            |                        |                       |      | 5    | 10          |      | 10           |      | 10   | pF |

| C <sub>I/O</sub> | Bus Terminal<br>Capacitance                  |                        |                       |      | 13   |             |      |              |      |      | pF |

| C <sub>PD</sub>  | Power Dissipation<br>Capacitance (note<br>1) |                        |                       |      | 40   |             |      |              |      |      | pF |

1)  $C_{PD}$  is defined as the value of the IC's internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation.  $I_{CC(opr)} = C_{PD} \times V_{CC} \times f_{IN} + I_{CC}/8$  (per bit)

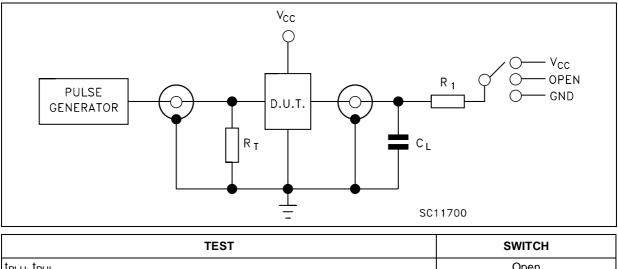

#### **TEST CIRCUIT**

| t <sub>PLH</sub> , t <sub>PHL</sub> | Open            |

|-------------------------------------|-----------------|

| t <sub>PZL</sub> , t <sub>PLZ</sub> | V <sub>CC</sub> |

| t <sub>PZH</sub> , t <sub>PHZ</sub> | GND             |

$C_L = 50 \text{pF}/150 \text{pF}$  or equivalent (includes jig and probe capacitance)  $R_1 = 1K\Omega$  or equivalent  $R_T = Z_{OUT}$  of pulse generator (typically 50 $\Omega$ )

#### WAVEFORM 1: PROPAGATION DELAY TIME (f=1MHz; 50% duty cycle)

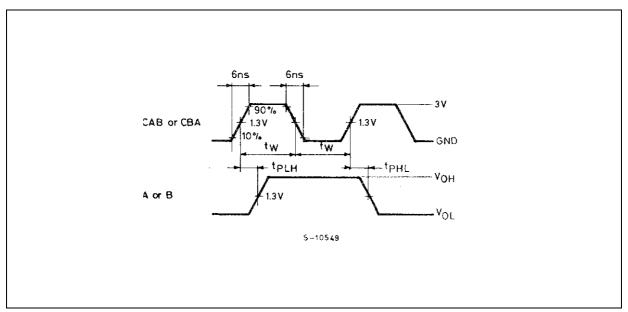

**WAVEFORM 2 : CLOCK AB, BA MINIMUM PULSE WIDTH, PROPAGATION DELAY TIME** (f=1MHz; 50% duty cycle)

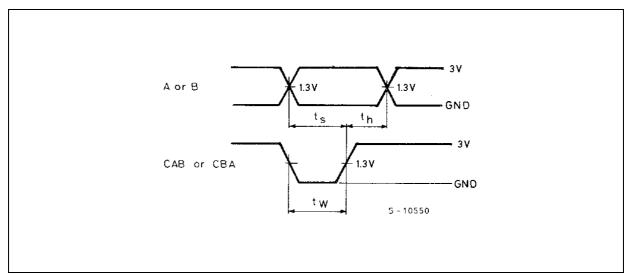

#### WAVEFORM 3: A, B TO CLOCK MINIMUM SETUP AND HOLD TIME (f=1MHz; 50% duty cycle)

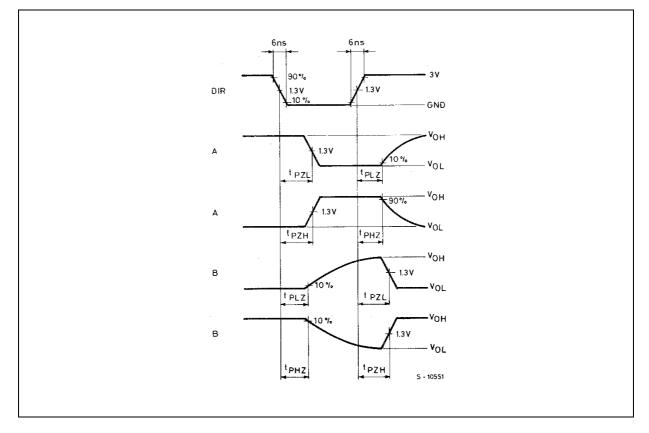

#### WAVEFORM 4 : OUTPUT ENABLE AND DISABLE TIME (f=1MHz; 50% duty cycle)

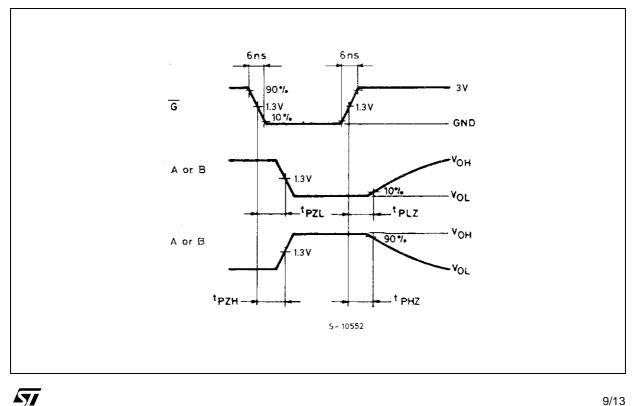

WAVEFORM 5: OUTPUT ENABLE AND DISABLE TIME (f=1MHz; 50% duty cycle)

Γ

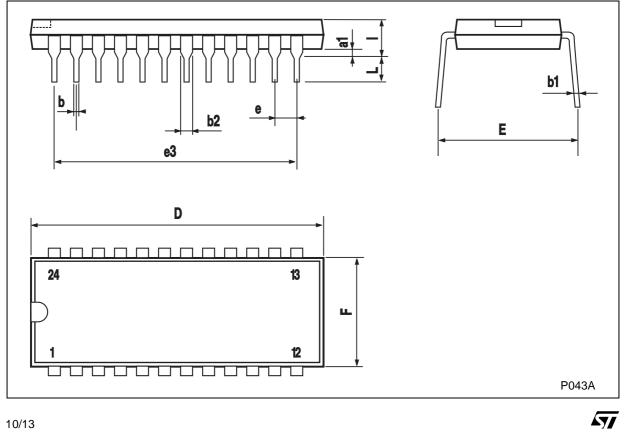

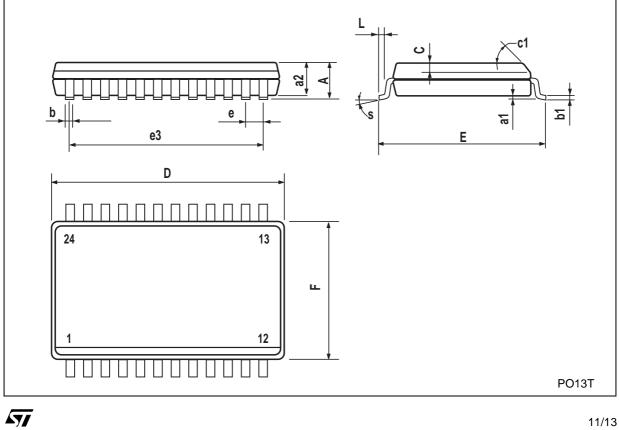

| DIM.  |      | mm.   |       |       | inch  |       |

|-------|------|-------|-------|-------|-------|-------|

| Diwi. | MIN. | ТҮР   | MAX.  | MIN.  | TYP.  | MAX.  |

| a1    |      | 0.63  |       |       | 0.025 |       |

| b     |      | 0.45  |       |       | 0.018 |       |

| b1    | 0.23 |       | 0.31  | 0.009 |       | 0.012 |

| b2    |      | 1.27  |       |       | 0.500 |       |

| D     |      |       | 32.2  |       |       | 1.268 |

| E     | 15.2 |       | 16.68 | 0.598 |       | 0.657 |

| е     |      | 2.54  |       |       | 0.100 |       |

| e3    |      | 27.94 |       |       | 1.100 |       |

| F     |      |       | 14.1  |       |       | 0.555 |

| I     |      | 4.445 |       |       | 0.175 |       |

| DIM.  |       | mm.   |       | inch   |       |       |  |  |

|-------|-------|-------|-------|--------|-------|-------|--|--|

| DINI. | MIN.  | ТҮР   | MAX.  | MIN.   | TYP.  | MAX.  |  |  |

| А     |       |       | 2.65  |        |       | 0.104 |  |  |

| a1    | 0.1   |       | 0.2   | 0.004  |       | 0.008 |  |  |

| a2    |       |       | 2.45  |        |       | 0.096 |  |  |

| b     | 0.35  |       | 0.49  | 0.014  |       | 0.019 |  |  |

| b1    | 0.23  |       | 0.32  | 0.009  |       | 0.012 |  |  |

| С     |       | 0.5   |       |        | 0.020 |       |  |  |

| c1    |       |       | 45°   | (typ.) |       |       |  |  |

| D     | 15.20 |       | 15.60 | 0.598  |       | 0.614 |  |  |

| E     | 10.00 |       | 10.65 | 0.393  |       | 0.419 |  |  |

| е     |       | 1.27  |       |        | 0.050 |       |  |  |

| e3    |       | 13.97 |       |        | 0.550 |       |  |  |

| F     | 7.40  |       | 7.60  | 0.291  |       | 0.300 |  |  |

| L     | 0.50  |       | 1.27  | 0.020  |       | 0.050 |  |  |

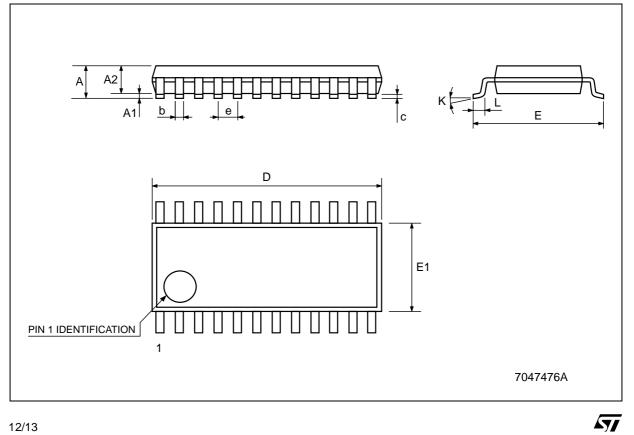

### **SO-24 MECHANICAL DATA**

|      |      | mm.      |      |        | inch       |        |  |  |  |  |

|------|------|----------|------|--------|------------|--------|--|--|--|--|

| DIM. | MIN. | ТҮР      | MAX. | MIN.   | TYP.       | MAX.   |  |  |  |  |

| А    |      |          | 1.1  |        |            | 0.043  |  |  |  |  |

| A1   | 0.05 |          | 0.15 | 0.002  |            | 0.006  |  |  |  |  |

| A2   |      | 0.9      |      |        | 0.035      |        |  |  |  |  |

| b    | 0.19 |          | 0.30 | 0.0075 |            | 0.0118 |  |  |  |  |

| С    | 0.09 |          | 0.20 | 0.0035 |            | 0.0079 |  |  |  |  |

| D    | 7.7  |          | 7.9  | 0.303  |            | 0.311  |  |  |  |  |

| Е    | 6.25 |          | 6.5  | 0.246  |            | 0.256  |  |  |  |  |

| E1   | 4.3  |          | 4.5  | 0.169  |            | 0.177  |  |  |  |  |

| е    |      | 0.65 BSC |      |        | 0.0256 BSC |        |  |  |  |  |

| К    | 0°   |          | 8°   | 0°     |            | 8°     |  |  |  |  |

| L    | 0.50 |          | 0.70 | 0.020  |            | 0.028  |  |  |  |  |

٦

Γ

12/13

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

© The ST logo is a registered trademark of STMicroelectronics

© 2001 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom

© http://www.st.com