## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### **General Description**

The MAX11329-MAX11332 are 12-/10-bit with external reference and 500kHz, full-linear-bandwidth, high-speed, low-power, serial-output successive approximation register (SAR) analog-to-digital converters (ADCs). The MAX11329-MAX11332 provide external access to the output of the integrated mux and ADC input, to simplify the signal conditional circuitry. The MAX11329-MAX11332 include both internal and external clock modes. These devices feature scan mode in both internal and external clock modes. The internal clock mode features internal averaging to increase SNR. The external clock mode features the SampleSet™ technology, a user-programmable analog input channel sequencer. The SampleSet approach provides greater sequencing flexibility for multichannel applications while alleviating significant microcontroller or DSP (controlling unit) communication overhead.

External pins provide access to the output of the multiplexer and ADC inputs to simplify multichannel signal conditioning. The internal clock mode features an integrated FIFO allowing data to be sampled at high speeds and then held for readout at any time or at a lower clock rate. Internal averaging is also supported in internal clock mode improving SNR for noisy input signals. The devices feature analog input channels that can be configured to be single-ended inputs, fully differential pairs, or pseudo-differential inputs with respect to one common input. The MAX11329–MAX11332 operate from a 2.35V to 3.6V supply and consume only 15.2mW at 3Msps.

The MAX11329–MAX11332 include AutoShutdown™, fast wake-up, and a high-speed 3-wire serial interface. The devices feature full power-down mode for optimal power management. The 48MHz, 3-wire serial interface directly connects to SPI, QSPI™, and MICROWIRE® devices without external logic.

Excellent dynamic performance, low voltage, low power, ease of use, and small package size make these converters ideal for portable battery-powered data-acquisition applications, and for other applications that demand low power consumption and small space.

The MAX11329–MAX11332 are available in 32-pin, 5mm x 5mm, TQFN packages and operate over the -40°C to +125°C temperature range.

μΜΑΧ is a registered trademark of Maxim Integrated Products, Inc.

### **Benefits and Features**

- ♦ Scan Modes, Internal Averaging, and Internal Clock

- ♦ 16-Entry First-In/First-Out (FIFO)

- ♦ SampleSet: User-Defined Channel Sequence with Maximum Length of 256

- Input Pins

- ♦ Any Combination of Single-Ended, Differential and Pseudo-Differential Pairs Allowed

- ♦ Analog Multiplexer with True Differential Track/Hold

- ♦ 16-/8-Channel Single-Ended

- ♦ 8-/4-Channel Fully-Differential Pairs

- 15-/8-Channel Pseudo-Differential Relative to a Common Input

- ♦ Externally Accessible Multiplex Output and ADC Input

- ♦ Flexible Input Configuration Across All Channels

- ♦ High Accuracy

- $\Rightarrow$  ±1 LSB INL, ±1 LSB DNL, No Missing Codes

- ♦ 70dB SINAD Guaranteed at 100kHz Input Frequency

- ♦ 1.5V to 3.6V Digital I/O Supply Voltage

- ♦ 2.35V to 3.6V Supply Voltage

- **♦ Extended Battery Life for Portable Applications**

- ♦ 15.2mW at 3Msps with 3V Supplies

- → 2µA Full-Shutdown Current

- **♦** External Differential Reference (1V to V<sub>DD</sub>)

- ♦ 48MHz, 3-Wire SPI-/QSPI-/MICROWIRE-/DSP-Compatible Serial Interface

- ♦ Wide -40°C to +125°C Operation

- ♦ Space-Saving, 32-Pin, 5mm x 5mm TQFN Packages

- ♦ 3Msps Conversion Rate, No Pipeline Delay

## **Applications**

High-Speed Data Acquisition Systems

High-Speed Closed-Loop Systems

Industrial Control Systems

Medical Instrumentation

Battery-Powered Instruments

Portable Systems

For related parts and recommended products to use with this part, refer to www.maxim-ic.com/MAX11329-MAX11332.related.

Ordering Information appears at end of data sheet.

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND0.3V to +4V                   | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|-----------------------------------------------------|-------------------------------------------------------|

| OVDD, AIN0-AIN13, CNVST/AIN14, REF+, REF-/AIN15     | TQFN (derate 34.4mW/°C above +70°C)2758mW             |

| to GND0.3V to the lower of (VDD + 0.3V) and +4V     | Operating Temperature Range40°C to +125°C             |

| CS, SCLK, DIN, DOUT, EOC TO GND0.3V to the lower of | Junction Temperature+150°C                            |

| $(V_{OVDD} + 0.3V)$ and +4V                         | Storage Temperature Range65°C to +150°C               |

| DGND to GND0.3V to +0.3V                            | Lead Temperature (soldering, 10s)+300°C               |

| Input/Output Current (all pins)50mA                 | Soldering Temperature (reflow)+260°C                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

**TOFN**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )........29°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )...........2°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

### **ELECTRICAL CHARACTERISTICS (MAX11331/MAX11332)**

$(V_{DD} = 2.35V \text{ to } 3.6V, V_{OVDD} = 1.5V \text{ to } 3.6V, f_{SAMPLE} = 3Msps, f_{SCLK} = 48MHz, 50\% \text{ duty cycle, } V_{REF+} = V_{DD}, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, unless otherwise noted. Typical values are at <math>T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                                          | SYMBOL           | CONDITIONS                               | MIN | TYP  | MAX      | UNITS   |

|----------------------------------------------------|------------------|------------------------------------------|-----|------|----------|---------|

| DC ACCURACY (Notes 3 and 4)                        |                  |                                          |     |      |          |         |

| Resolution                                         | RES              | 12 bit                                   | 12  |      |          | Bits    |

| Integral Nonlinearity                              | INL              |                                          |     |      | ±1.0     | LSB     |

| Differential Nonlinearity                          | DNL              | No missing codes                         |     |      | ±1.0     | LSB     |

| Offset Error                                       |                  |                                          |     | 1.2  | ±3.0     | LSB     |

| Gain Error                                         |                  | (Note 5)                                 |     | 0    | ±5.5     | LSB     |

| Offset Error Temperature Coefficient               | OE <sub>TC</sub> |                                          |     | ±2   |          | ppm/°C  |

| Gain Temperature Coefficient                       | GE <sub>TC</sub> |                                          |     | ±0.8 |          | ppm/°C  |

| Channel-to-Channel Offset Matching                 |                  |                                          |     | ±0.5 |          | LSB     |

| Line Rejection                                     | PSR              | (Note 6)                                 |     | ±0.3 | ±2       | LSB/V   |

| DYNAMIC PERFORMANCE (100kHz                        | , input sine v   | vave) (Notes 3 and 7)                    |     |      |          |         |

| Signal-to-Noise Plus Distortion                    | SINAD            |                                          | 70  | 71.9 |          | dB      |

| Signal-to-Noise Ratio                              | SNR              |                                          | 70  | 72.3 |          | dB      |

| Total Harmonic Distortion (Up to the 5th Harmonic) | THD              |                                          |     | -88  | -76      | dB      |

| Spurious-Free Dynamic Range                        | SFDR             |                                          | 77  | 84   |          | dB      |

| Intermodulation Distortion                         | IMD              | $f_1 = 99.2432$ kHz, $f_2 = 69.2139$ kHz |     | -85  |          | dB      |

| Full-Power Bandwidth                               |                  | -3dB                                     |     | 30   |          | - MHz   |

| Full-Fower Danuwidth                               |                  | -0.1dB                                   |     | 5    |          | ] IVI□∠ |

| Full-Linear Bandwidth                              |                  | SINAD ≥ 70dB                             |     | 0.5  | <u> </u> | MHz     |

# 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### **ELECTRICAL CHARACTERISTICS (MAX11331/MAX11332) (continued)**

$(V_{DD}=2.35 V\ to\ 3.6 V,\ V_{OVDD}=1.5 V\ to\ 3.6 V,\ f_{SAMPLE}=3 Msps,\ f_{SCLK}=48 MHz,\ 50\%\ duty\ cycle,\ V_{REF+}=V_{DD},\ T_{A}=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_{A}=+25^{\circ}C.$ ) (Note 2)

| PARAMETER                      | SYMBOL                               | CON                                                                                                  | NDITIONS                      | MIN                         | TYP                         | MAX                         | UNITS    |

|--------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------|-----------------------------|-----------------------------|----------|

| Crosstalk                      |                                      | -0.5dB below full-<br>sine wave input to<br>sampled, apply fu<br>sine wave signal<br>input channels. |                               | -88                         |                             | dB                          |          |

| CONVERSION RATE                |                                      |                                                                                                      |                               |                             |                             |                             |          |

| Power-Up Time                  | t <sub>PU</sub>                      | Conversion cycle                                                                                     | , external clock              |                             |                             | 2                           | Cycles   |

| Acquisition Time               | t <sub>ACQ</sub>                     |                                                                                                      |                               |                             | 52                          |                             | ns       |

| Conversion Time                | <sup>t</sup> CONV                    | Externally clocked 16 cycles (Note 8                                                                 | d, f <sub>SCLK</sub> = 48MHz, | 333                         | 2.1                         | -                           | μs<br>ns |

| External Clock Frequency       | f <sub>SCLK</sub>                    |                                                                                                      | ,                             | 0.48                        |                             | 48                          | MHz      |

| Aperture Delay                 | OOLIK                                |                                                                                                      |                               |                             | 8                           |                             | ns       |

| Aperture Jitter                |                                      | RMS                                                                                                  |                               |                             | 30                          |                             | ps       |

| ANALOG INPUT                   |                                      |                                                                                                      |                               |                             |                             |                             |          |

|                                | V <sub>INA</sub>                     | Unipolar, (single differential)                                                                      | ended and pseudo-             | 0                           |                             | V <sub>REF+</sub>           |          |

| Input Voltage Range            | TINA                                 | Bipolar                                                                                              | Range bit set to 0            | -V <sub>REF+</sub> /2       |                             | V <sub>REF+</sub> /2        | V        |

|                                |                                      | (Note 9)                                                                                             | Range bit set to 1            | -V <sub>REF+</sub>          |                             | V <sub>REF+</sub>           |          |

| Absolute Input Voltage Range   |                                      | AIN+, AIN- relativ                                                                                   | ve to GND                     | -0.1                        | V <sub>R</sub>              | EF+ + 0.1                   | V        |

| Static Input Leakage Current   | I <sub>ILA</sub>                     | V <sub>AIN</sub> = V <sub>DD</sub> , GNE                                                             | )                             |                             | -0.01                       | ±1.5                        | μΑ       |

| Input Capacitance              |                                      | During acquisition RANGE bit = 0 (N                                                                  | n time;                       |                             | 15                          |                             | pF       |

| піри Сараснансе                | C <sub>AIN</sub>                     | During acquisition time; RANGE bit = 1 (Note 10) 7.5                                                 |                               |                             | рі                          |                             |          |

| EXTERNAL REFERENCE INPUT       |                                      |                                                                                                      |                               |                             |                             |                             |          |

| REF- Input Voltage Range       | V <sub>REF-</sub>                    |                                                                                                      |                               | -0.3                        |                             | +1                          | V        |

| REF+ Input Voltage Range       | V <sub>REF+</sub>                    |                                                                                                      |                               | 1                           | $V_{DE}$                    | ) + 50mV                    | V        |

| DEE 1 10 1                     |                                      | $V_{REF+} = 2.5V, f_{SA}$                                                                            | AMPLE = 3Msps                 |                             | 110                         |                             | ^        |

| REF+ Input Current<br>         | REF+ Input Current I <sub>REF+</sub> |                                                                                                      | AMPLE = 0Msps                 |                             | 0.1                         |                             | μΑ       |

| DIGITAL INPUTS (SCLK, DIN, CS, | CNVST)                               |                                                                                                      |                               |                             |                             |                             |          |

| Input Voltage Low              | V <sub>IL</sub>                      |                                                                                                      |                               |                             |                             | V <sub>OVDD</sub><br>x 0.25 | V        |

| Input Voltage High             | V <sub>IH</sub>                      |                                                                                                      |                               | V <sub>OVDD</sub><br>x 0.75 |                             |                             | V        |

| Input Hysteresis               | V <sub>HYST</sub>                    |                                                                                                      |                               |                             | V <sub>OVDD</sub><br>x 0.15 |                             | mV       |

# 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### **ELECTRICAL CHARACTERISTICS (MAX11331/MAX11332) (continued)**

$(V_{DD}=2.35 \text{V to } 3.6 \text{V}, V_{OVDD}=1.5 \text{V to } 3.6 \text{V}, f_{SAMPLE}=3 \text{Msps}, f_{SCLK}=48 \text{MHz}, 50\% \text{ duty cycle}, V_{REF+}=V_{DD}, T_{A}=-40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{unless otherwise noted}.$

| PARAMETER                      | SYMBOL            |                                                  | CONDI                     | TIONS                                                | MIN                         | TYP          | MAX                         | UNITS |

|--------------------------------|-------------------|--------------------------------------------------|---------------------------|------------------------------------------------------|-----------------------------|--------------|-----------------------------|-------|

| Input Leakage Current          | I <sub>IN</sub>   | V <sub>AIN</sub> = 0V                            | or V <sub>DD</sub>        |                                                      |                             | ±0.09        | ±1.0                        | μΑ    |

| Input Capacitance              | C <sub>IN</sub>   |                                                  |                           |                                                      |                             | 3            |                             | рF    |

| DIGITAL OUTPUTS (DOUT, EOC)    |                   |                                                  |                           |                                                      |                             |              |                             |       |

| Output Voltage Low             | V <sub>OL</sub>   | I <sub>SINK</sub> = 20                           | I <sub>SINK</sub> = 200μA |                                                      |                             |              | V <sub>OVDD</sub><br>x 0.15 | V     |

| Output Voltage High            | V <sub>OH</sub>   | I <sub>SOURCE</sub> =                            | : 200µA                   |                                                      | V <sub>OVDD</sub><br>x 0.85 |              |                             | V     |

| Three-State Leakage Current    | IL                | $\overline{\text{CS}} = V_{\text{DD}}$           |                           |                                                      |                             | -0.3         | ±1.5                        | μΑ    |

| Three-State Output Capacitance | C <sub>OUT</sub>  | $\overline{\text{CS}} = V_{\text{DD}}$           |                           |                                                      |                             | 4            |                             | рF    |

| POWER REQUIREMENTS             | •                 |                                                  |                           |                                                      |                             |              |                             |       |

| Positive Supply Voltage        | V <sub>DD</sub>   |                                                  |                           |                                                      | 2.35                        | 3.0          | 3.6                         | V     |

| Digital I/O Supply Voltage     | V <sub>OVDD</sub> |                                                  |                           |                                                      | 1.5                         | 3.0          | 3.6                         | V     |

|                                |                   | f <sub>SAMPLE</sub> =                            | 3Msps                     |                                                      |                             | 5.1          | 6.5                         |       |

| Positive Supply Current        | I <sub>DD</sub>   | f <sub>SAMPLE</sub> = 0Msps (3Msps devices)      |                           |                                                      |                             | 2.5          |                             | mA    |

|                                |                   | Full shutdown                                    |                           |                                                      |                             | 0.0013 0.006 |                             |       |

|                                |                   | Normal mode $V_{DD} = 3V$ , $f_{SAMPLE} = 3Msps$ |                           |                                                      |                             | 15.2         |                             |       |

|                                |                   | (External<br>Reference                           | )                         | $V_{DD} = 2.35V$ ,<br>$f_{SAMPLE} = 3Msps$           |                             | 10.3         |                             |       |

| Power Dissipation              |                   | $V_{DD} = 3V$ ,                                  |                           | V <sub>DD</sub> = 3V,<br>f <sub>SAMPLE</sub> = 3Msps |                             | 7.3          | mW                          |       |

|                                |                   |                                                  |                           |                                                      | 4.35                        |              |                             |       |

|                                |                   | Full/                                            |                           | $V_{DD} = 3V$                                        |                             | 3.9          |                             | \A/   |

|                                |                   | AutoShutd                                        | own                       | $V_{DD} = 2.35V$                                     |                             | 1.7          |                             | μW    |

| TIMING CHARACTERISTICS (Figur  | e 1) (Note 11)    |                                                  |                           |                                                      |                             |              |                             |       |

| SCLK Clock Period              | t <sub>CP</sub>   | Externally                                       | clocked c                 | onversion                                            | 20.8                        |              |                             | ns    |

| SCLK Duty Cycle                | t <sub>CH</sub>   |                                                  |                           |                                                      | 40                          |              | 60                          | %     |

| SCLK Fall to DOUT Transition   | tpor              | C <sub>LOAD</sub> =                              | V <sub>OVDD</sub> =       | = 1.5V to 2.35V                                      | 4                           |              | 16.5                        | ns    |

| OOLINT AII TO DOOT TTATISHIOT  | t <sub>DOT</sub>  | 10pF                                             | V <sub>OVDD</sub> =       | = 2.35V to 3.6V                                      | 4                           |              | 15                          | 110   |

| 16th SCLK Fall to DOUT Disable | t <sub>DOD</sub>  | C <sub>LOAD</sub> = 10pF, channel ID on          |                           |                                                      |                             | 15           | ns                          |       |

| 14th SCLK Fall to DOUT Disable |                   | C <sub>LOAD</sub> = 10pF, channel ID off         |                           | nnel ID off                                          |                             |              | 16                          | ns    |

| SCLK Fall to DOUT Enable       | t <sub>DOE</sub>  | $C_{LOAD} = 1$                                   | 0pF                       |                                                      |                             |              | 14                          | ns    |

| DIN to SCLK Rise Setup         | t <sub>DS</sub>   |                                                  |                           |                                                      | 4                           |              |                             | ns    |

| SCLK Rise to DIN Hold          | t <sub>DH</sub>   |                                                  |                           |                                                      | 1                           |              |                             | ns    |

|                                |                   |                                                  |                           |                                                      |                             |              |                             |       |

# 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### **ELECTRICAL CHARACTERISTICS (MAX11331/MAX11332) (continued)**

$(V_{DD} = 2.35V \text{ to } 3.6V, V_{OVDD} = 1.5V \text{ to } 3.6V, f_{SAMPLE} = 3Msps, f_{SCLK} = 48MHz, 50\% duty cycle, V_{REF+} = V_{DD}, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, unless otherwise noted. Typical values are at <math>T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                                     | SYMBOL           | CONDITIONS                                | MIN | TYP | MAX | UNITS |

|-----------------------------------------------|------------------|-------------------------------------------|-----|-----|-----|-------|

| CS Fall to SCLK Fall Setup                    | t <sub>CSS</sub> |                                           | 4   |     |     | ns    |

| SCLK Fall to $\overline{\text{CS}}$ Fall Hold | tcsh             |                                           | 1   |     |     | ns    |

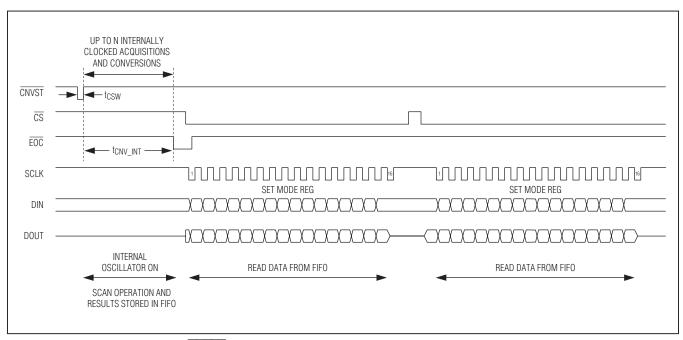

| CNVST Pulse Width                             | t <sub>CSW</sub> | See Figure 6                              | 5   |     |     | ns    |

| CS or CNVST Rise to EOC Low (Note 6)          | tCNV_INT         | See Figure 7, f <sub>SAMPLE</sub> = 3Msps |     | 1.7 | 2.4 | μs    |

| CS Pulse Width                                | tcsbw            |                                           | 5   |     |     | ns    |

### **ELECTRICAL CHARACTERISTICS (MAX11329/MAX11330)**

$(V_{DD} = 2.35V \text{ to } 3.6V, V_{OVDD} = 1.5V \text{ to } 3.6V, f_{SAMPLE} = 3Msps, f_{SCLK} = 48MHz, 50\% \text{ duty cycle}, V_{REF+} = V_{DD}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, unless otherwise noted. Typical values are at <math>T_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                          | SYMBOL           | CONDITIONS                                           | MIN | TYP   | MAX  | UNITS  |

|----------------------------------------------------|------------------|------------------------------------------------------|-----|-------|------|--------|

| DC ACCURACY (Notes 3 and 4)                        |                  |                                                      |     |       |      |        |

| Resolution                                         | RES              | 10 bit                                               | 10  |       |      | Bits   |

| Integral Nonlinearity                              | INL              |                                                      |     |       | ±0.4 | LSB    |

| Differential Nonlinearity                          | DNL              | No missing codes                                     |     |       | ±0.4 | LSB    |

| Offset Error                                       |                  |                                                      |     | 0.7   | ±1.2 | LSB    |

| Gain Error                                         |                  | (Note 5)                                             |     | 0     | ±1.5 | LSB    |

| Offset Error Temperature<br>Coefficient            | OE <sub>TC</sub> |                                                      |     | ±2    |      | ppm/°C |

| Gain Temperature Coefficient                       | GE <sub>TC</sub> |                                                      |     | ±0.8  |      | ppm/°C |

| Channel-to-Channel Offset Matching                 |                  |                                                      |     | ±0.5  |      | LSB    |

| Line Rejection                                     | PSR              | (Note 6)                                             |     | 0.2   | ±1.0 | LSB/V  |

| DYNAMIC PERFORMANCE (100                           | kHz, input si    | ne wave) (Notes 3 and 7)                             |     |       |      |        |

| Signal-to-Noise Plus Distortion                    | SINAD            |                                                      | 61  | 61.5  |      | dB     |

| Signal-to-Noise Ratio                              | SNR              |                                                      | 61  | 61.5  |      | dB     |

| Total Harmonic Distortion (Up to the 5th Harmonic) | THD              |                                                      |     | -82.5 | -75  | dB     |

| Spurious-Free Dynamic Range                        | SFDR             |                                                      | 76  | 83.4  |      | dB     |

| Intermodulation Distortion                         | IMD              | $f_1 = 99.2432 \text{kHz}, f_2 = 69.2139 \text{kHz}$ |     | -83   |      | dB     |

| Full Dawer Dandwidth                               |                  | -3dB                                                 |     | 30    |      | MHz    |

| Full-Power Bandwidth                               |                  | -0.1dB                                               |     | 5     |      | MHz    |

| Full-Linear Bandwidth                              |                  | SINAD ≥ 61dB                                         |     | 0.5   |      | MHz    |

# 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### **ELECTRICAL CHARACTERISTICS (MAX11329/MAX11330) (continued)**

$(V_{DD}=2.35V\ to\ 3.6V,\ V_{OVDD}=1.5V\ to\ 3.6V,\ f_{SAMPLE}=3Msps,\ f_{SCLK}=48MHz,\ 50\%\ duty\ cycle,\ V_{REF+}=V_{DD},\ T_{A}=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_{A}=+25^{\circ}C.)$  (Note 2)

| PARAMETER                     | SYMBOL            | C                                                                                                                                                                     | CONDITIONS                     | MIN                         | TYP  | MAX                         | UNITS    |

|-------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------|------|-----------------------------|----------|

| Crosstalk                     |                   | -0.5dB below full-scale of 99.2432kHz sine-wave input to the channel being sampled; apply full-scale 69.2139kHz sine wave signal to all 15 nonselected input channels |                                |                             | -88  |                             | dB       |

| CONVERSION RATE               |                   |                                                                                                                                                                       |                                |                             |      |                             |          |

| Power-Up Time                 | t <sub>PU</sub>   | Conversion cycle                                                                                                                                                      | e, external clock              |                             |      | 2                           | Cycles   |

| Acquisition Time              | t <sub>ACQ</sub>  |                                                                                                                                                                       |                                |                             | 52   |                             | ns       |

| Conversion Time               | t <sub>CONV</sub> | Externally clocked 16 cycles (Note)                                                                                                                                   | ed, f <sub>SCLK</sub> = 48MHz, | 333                         | 2.1  |                             | μs<br>ns |

| External Clock Frequency      | fsclk             |                                                                                                                                                                       |                                | 0.48                        |      | 48                          | MHz      |

| Aperture Delay                |                   |                                                                                                                                                                       |                                |                             | 8    |                             | ns       |

| Aperture Jitter               |                   | RMS                                                                                                                                                                   |                                |                             | 30   |                             | ps       |

| ANALOG INPUT                  |                   |                                                                                                                                                                       |                                |                             |      |                             |          |

|                               |                   | Unipolar (single-differential)                                                                                                                                        | ended and pseudo               | 0                           |      | V <sub>REF+</sub>           |          |

| Input Voltage Range           | V <sub>INA</sub>  | Bipolar (Note 9)                                                                                                                                                      | RANGE bit set to 0             | -V <sub>REF+</sub>          |      | +V <sub>REF+</sub> V        |          |

|                               |                   |                                                                                                                                                                       | RANGE bit set to 1             | -V <sub>REF+</sub>          |      | +V <sub>REF+</sub>          |          |

| Absolute Input Voltage Range  |                   | AIN+, AIN- relati                                                                                                                                                     | ve to GND                      | -0.1                        |      | V <sub>REF+</sub><br>+ 0.1  | V        |

| Static Input Leakage Current  | I <sub>ILA</sub>  | V <sub>AIN</sub> _ = V <sub>DD</sub> , GN                                                                                                                             | ND                             |                             | -0.1 | ±1.5                        | μΑ       |

| Input Capacitanes             | C                 | During acquisition RANGE bit = 0 (I                                                                                                                                   |                                |                             | 15   |                             | nΕ       |

| Input Capacitance             | C <sub>AIN</sub>  | During acquisition RANGE bit = 1 (I                                                                                                                                   |                                |                             | 7.5  |                             | pF       |

| EXTERNAL REFERENCE INPUT      | 1                 |                                                                                                                                                                       |                                |                             |      |                             |          |

| REF- Input Voltage Range      | V <sub>REF-</sub> |                                                                                                                                                                       |                                | -0.3                        |      | +1                          | V        |

| REF+ Input Voltage Range      | V <sub>REF+</sub> |                                                                                                                                                                       |                                | 1                           |      | V <sub>DD</sub><br>+50mV    | V        |

| REF+ Input Current            | 1                 | $V_{REF+} = 2.5V, f_{S}$                                                                                                                                              | AMPLE = 3Msps                  |                             | 110  |                             | μΑ       |

| nici + iriput Gurrent         | I <sub>REF+</sub> | $V_{REF+} = 2.5V, f_{S}$                                                                                                                                              | AMPLE = 0Msps                  |                             | 0.1  |                             | μΑ       |

| DIGITAL INPUTS (SCLK, DIN, CS | S, CNVST)         |                                                                                                                                                                       |                                |                             |      |                             |          |

| Input Voltage Low             | V <sub>IL</sub>   |                                                                                                                                                                       |                                |                             |      | V <sub>OVDD</sub><br>x 0.25 | V        |

| Input Voltage High            | V <sub>IH</sub>   |                                                                                                                                                                       |                                | V <sub>OVDD</sub><br>x 0.75 |      |                             | V        |

# 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### **ELECTRICAL CHARACTERISTICS (MAX11329/MAX11330) (continued)**

$(V_{DD}=2.35V\ to\ 3.6V,\ V_{OVDD}=1.5V\ to\ 3.6V,\ f_{SAMPLE}=3Msps,\ f_{SCLK}=48MHz,\ 50\%\ duty\ cycle,\ V_{REF+}=V_{DD},\ T_{A}=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_{A}=+25^{\circ}C$ .) (Note 2)

| PARAMETER                      | SYMBOL            |                                             | C                          | CONDITIONS                                           | MIN                         | TYP                         | MAX                         | UNITS |  |

|--------------------------------|-------------------|---------------------------------------------|----------------------------|------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-------|--|

| Input Hysteresis               | V <sub>HYST</sub> |                                             |                            |                                                      |                             | V <sub>OVDD</sub><br>x 0.15 |                             | mV    |  |

| Input Leakage Current          | I <sub>IN</sub>   | V <sub>AIN</sub> _ = 0V c                   | $V_{AIN} = 0V$ or $V_{DD}$ |                                                      |                             |                             | ±1.0                        | μΑ    |  |

| Input Capacitance              | C <sub>IN</sub>   |                                             |                            |                                                      |                             | 3                           |                             | рF    |  |

| DIGITAL OUTPUTS (DOUT, EOC)    | )                 |                                             |                            |                                                      |                             |                             |                             |       |  |

| Output Voltage Low             | V <sub>OL</sub>   | I <sub>SINK</sub> = 200µ                    | ıΑ                         |                                                      |                             |                             | V <sub>OVDD</sub><br>x 0.15 | V     |  |

| Output Voltage High            | V <sub>OH</sub>   | I <sub>SOURCE</sub> = 2                     | 200μ                       | A                                                    | V <sub>OVDD</sub><br>x 0.85 |                             |                             | V     |  |

| Three-State Leakage Current    | IL                | $\overline{\text{CS}} = V_{\text{DD}}$      |                            |                                                      |                             | -0.3                        | ±1.5                        | μΑ    |  |

| Three-State Output Capacitance | C <sub>OUT</sub>  | $\overline{\text{CS}} = V_{\text{DD}}$      |                            |                                                      |                             | 4                           |                             | рF    |  |

| POWER REQUIREMENTS             |                   |                                             |                            |                                                      |                             |                             |                             |       |  |

| Positive Supply Voltage        | V <sub>DD</sub>   |                                             |                            |                                                      | 2.35                        | 3.0                         | 3.6                         | V     |  |

| Digital I/O Supply Voltage     | V <sub>OVDD</sub> |                                             |                            |                                                      | 1.5                         | 3.0                         | 3.6                         | V     |  |

|                                |                   | f <sub>SAMPLE</sub> = 3                     | Msp                        | S                                                    |                             | 5.1                         | 6.5                         |       |  |

| Positive Supply Current        | I <sub>DD</sub>   | f <sub>SAMPLE</sub> = 0Msps (3Msps devices) |                            |                                                      |                             | 2.5                         |                             | mA    |  |

|                                |                   | Full shutdown                               |                            |                                                      |                             | 0.0013                      | 0.006                       | 006   |  |

|                                |                   | Normal mode<br>(external<br>reference)      |                            | V <sub>DD</sub> = 3V,<br>f <sub>SAMPLE</sub> = 3Msps |                             | 15.2                        | mW                          |       |  |

|                                |                   |                                             |                            | $V_{DD} = 2.35V$ ,<br>$f_{SAMPLE} = 3Msps$           |                             | 10.3                        |                             |       |  |

| Power Dissipation              |                   |                                             |                            | V <sub>DD</sub> = 3V,<br>f <sub>SAMPLE</sub> = 3Msps |                             | 7.3                         |                             |       |  |

|                                |                   |                                             |                            | $V_{DD} = 2.35V$ ,<br>$f_{SAMPLE} = 3Msps$           |                             | 4.35                        |                             |       |  |

|                                |                   | Full/                                       |                            | $V_{DD} = 3V$                                        |                             | 3.9                         |                             | 14/   |  |

|                                |                   | AutoShutdow                                 | 'n                         | $V_{DD} = 2.35V$                                     |                             | 1.7                         |                             | μW    |  |

| TIMING CHARACTERISTICS (Fig    | ure 1) (Note      | 11)                                         |                            |                                                      |                             |                             |                             |       |  |

| SCLK Clock Period              | t <sub>CP</sub>   | Externally clo                              | ocke                       | ed conversion                                        | 20.8                        |                             |                             | ns    |  |

| SCLK Duty Cycle                | tCH               |                                             |                            |                                                      | 40                          |                             | 60                          | %     |  |

| COLV. Fall to DOUT Trans '''   |                   | C <sub>LOAD</sub> =                         | VO                         | <sub>VDD</sub> = 1.5V to 2.35V                       | 4                           |                             | 16.5                        |       |  |

| SCLK Fall to DOUT Transition   | t <sub>DOT</sub>  |                                             |                            | <sub>VDD</sub> = 2.35V to 3.6V                       | 4                           |                             | 15                          | ns    |  |

| 16th SCLK Fall to DOUT Disable | t <sub>DOD</sub>  | C <sub>LOAD</sub> = 10pF, channel ID on     |                            |                                                      |                             | 15                          | ns                          |       |  |

| 14th SCLK Fall to DOUT Disable |                   | $C_{LOAD} = 10$                             | pF, o                      | channel ID off                                       |                             |                             | 16                          | ns    |  |

| SCLK Fall to DOUT Enable       | t <sub>DOE</sub>  | $C_{LOAD} = 10$                             |                            |                                                      |                             |                             | 14                          | ns    |  |

| DIN to SCLK Rise Setup         | t <sub>DS</sub>   |                                             |                            |                                                      | 4                           |                             |                             | ns    |  |

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### ELECTRICAL CHARACTERISTICS (MAX11329/MAX11330) (continued)

$(V_{DD} = 2.35V \text{ to } 3.6V, V_{OVDD} = 1.5V \text{ to } 3.6V, f_{SAMPLE} = 3Msps, f_{SCLK} = 48MHz, 50\% \text{ duty cycle, } V_{REF+} = V_{DD}, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, unless otherwise noted. Typical values are at <math>T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                            | SYMBOL            | CONDITIONS                                | MIN | TYP | MAX | UNITS |

|--------------------------------------|-------------------|-------------------------------------------|-----|-----|-----|-------|

| SCLK Rise to DIN Hold                | t <sub>DH</sub>   |                                           | 1   |     |     | ns    |

| CS Fall to SCLK Fall Setup           | t <sub>CSS</sub>  |                                           | 4   |     |     | ns    |

| SCLK Fall to CS Fall Hold            | tCSH              |                                           | 1   |     |     | ns    |

| CNVST Pulse Width                    | t <sub>CSW</sub>  | See Figure 6                              | 5   |     |     | ns    |

| CS or CNVST Rise to EOC Low (Note 7) | tCNV_INT          | See Figure 7, f <sub>SAMPLE</sub> = 3Msps |     | 1.7 | 2.4 | μs    |

| CS Pulse Width                       | t <sub>CSBW</sub> |                                           | 5   |     |     | ns    |

- **Note 2:** Limits are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design. Parts are tested with MUX externally connected to the ADC input.

- Note 3: Channel ID disabled.

- Note 4: Tested in single-ended mode.

- Note 5: Offset nulled.

- **Note 6:** Line rejection  $\Delta(D_{OUT})$  with  $V_{DD} = 2.35V$  to 3.6V and  $V_{REF+} = 2.35V$ .

- Note 7: Tested and guaranteed with fully differential input.

- Note 8: Conversion time is defined as the number of clock cycles multiplied by the clock period with a 50% duty cycle.

Maximum conversion time: 1.91µs + N x 16 x t<sub>OSC\_MAX</sub>

t<sub>OSC\_MAX</sub> = 29.4ns, t<sub>OSC\_TYP</sub> = 25ns.

- **Note 9:** The operational input voltage range for each individual input of a differentially configured pair is from V<sub>DD</sub> to GND. The operational input voltage difference is from -V<sub>REF+</sub>/2 to +V<sub>REF+</sub>/2 or -V<sub>REF+</sub> to +V<sub>REF+</sub>.

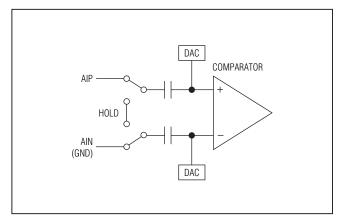

- Note 10: See Figure 3 (Equivalent Input Circuit).

- Note 11: Guaranteed by characterization.

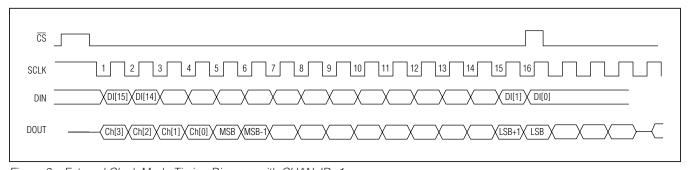

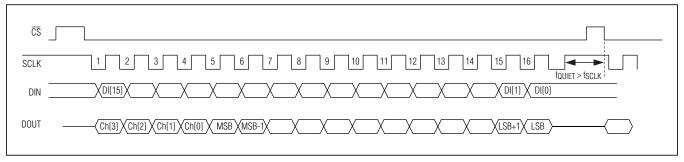

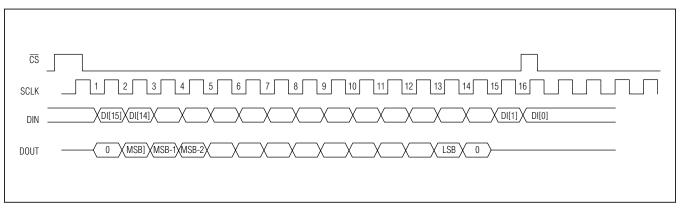

Figure 1. Detailed Serial-Interface Timing Diagram

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

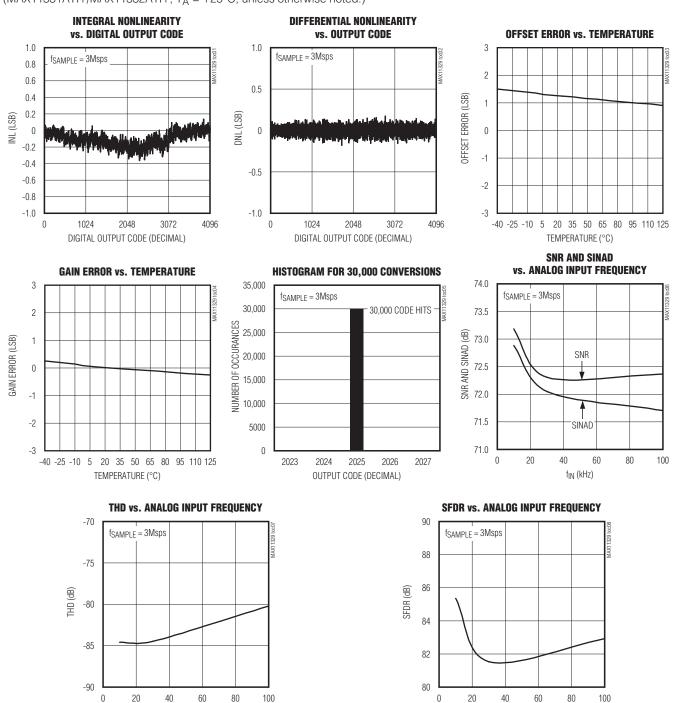

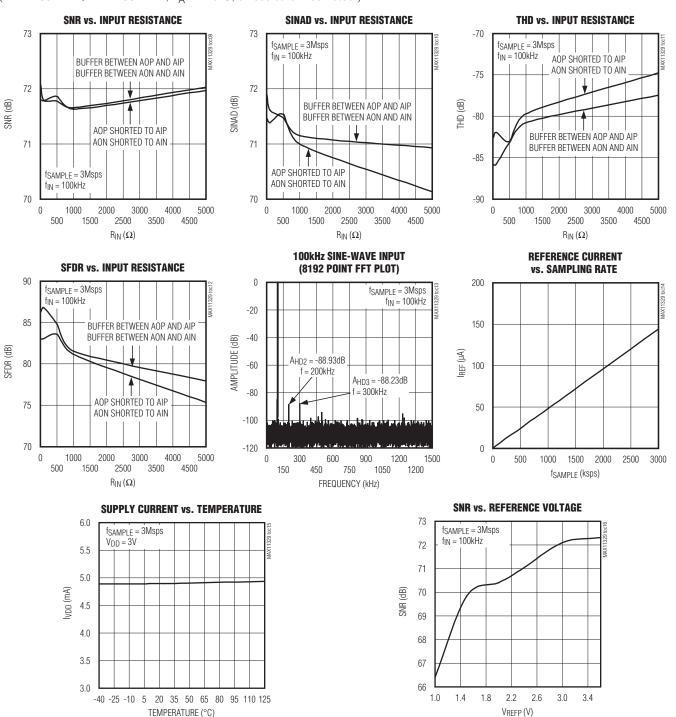

### **Typical Operating Characteristics**

f<sub>IN</sub> (kHz)

(MAX11331ATI+/MAX11332ATI+,  $T_A = +25$ °C, unless otherwise noted.)

f<sub>IN</sub> (kHz)

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### Typical Operating Characteristics (continued)

(MAX11331ATI+/MAX11332ATI+,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

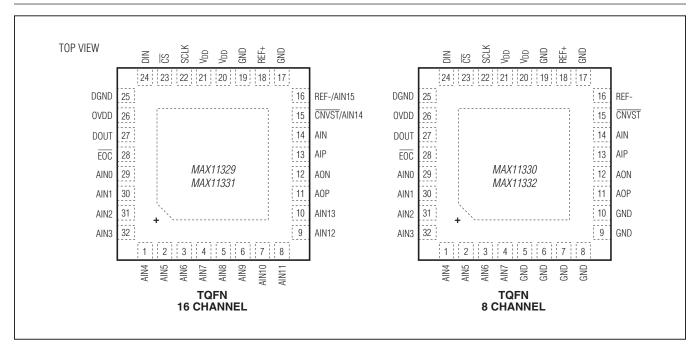

## **Pin Configurations**

## **Pin Description**

| MAX11329<br>MAX11331<br>(16 CHANNEL) | MAX11330<br>MAX11332<br>(8 CHANNEL) | NAME            | FUNCTION                                                                                                     |

|--------------------------------------|-------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------|

| 29–32 , 1–10                         | _                                   | AIN0-AIN13      | Analog Inputs                                                                                                |

| _                                    | 29–32, 1–4                          | AIN0-AIN7       | Analog Inputs                                                                                                |

| 11                                   | 11                                  | AOP             | Positive Output from the Multiplexer                                                                         |

| 12                                   | 12                                  | AON             | Negative Output from the Multiplexer                                                                         |

| 13                                   | 13                                  | AIP             | Positive Input to the ADC                                                                                    |

| 14                                   | 14                                  | AIN             | Negative Input to the ADC                                                                                    |

| 15                                   | _                                   | CNVST/<br>AIN14 | Active-Low Conversion Start Input/Analog Input 14                                                            |

| _                                    | 15                                  | CNVST           | Active-Low Conversion Start Input                                                                            |

| 16                                   | _                                   | REF-/AIN15      | External Differential Reference Negative Input /Analog Input 15                                              |

| _                                    | 16                                  | REF-            | External Differential Reference Negative Input                                                               |

| 17, 19                               | 5–10, 17, 19                        | GND             | Ground                                                                                                       |

| 18                                   | 18                                  | REF+            | External Positive Reference Input. Apply a reference voltage at REF+. Bypass to GND with a 0.47µF capacitor. |

# 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

## **Pin Description (continued)**

| MAX11329<br>MAX11331<br>(16 CHANNEL) | MAX11330<br>MAX11332<br>(8 CHANNEL) | NAME          | FUNCTION                                                                                                                                                                       |

|--------------------------------------|-------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20, 21                               | 20, 21                              | $V_{DD}$      | Power-Supply Input. Bypass to GND with a 10μF in parallel with a 0.1μF capacitors.                                                                                             |

| 22                                   | 22                                  | SCLK          | Serial Clock Input. Clocks data in and out of the serial interface.                                                                                                            |

| 23                                   | 23                                  | <del>CS</del> | Active-Low Chip Select Input. When $\overline{\text{CS}}$ is low, the serial interface is enabled. When $\overline{\text{CS}}$ is high, DOUT is high impedance or three-state. |

| 24                                   | 24                                  | DIN           | Serial Data Input. DIN data is latched into the serial interface on the rising edge of SCLK.                                                                                   |

| 25                                   | 25                                  | DGND          | Digital I/O Ground                                                                                                                                                             |

| 26                                   | 26                                  | OVDD          | Digital Power-Supply Input. Bypass to GND with a 10μF in parallel with a 0.1μF capacitors.                                                                                     |

| 27                                   | 27                                  | DOUT          | Serial Data Output. Data is clocked out on the falling edge of SCLK. When $\overline{\text{CS}}$ is high, DOUT is high impedance or three-state.                               |

| 28                                   | 28                                  | EOC           | End of Conversion Output. Data is valid after EOC is driven low (internal clock mode only).                                                                                    |

| _                                    | _                                   | EP            | Exposed Pad. Connect EP directly to GND plane for guaranteed performance.                                                                                                      |

# 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

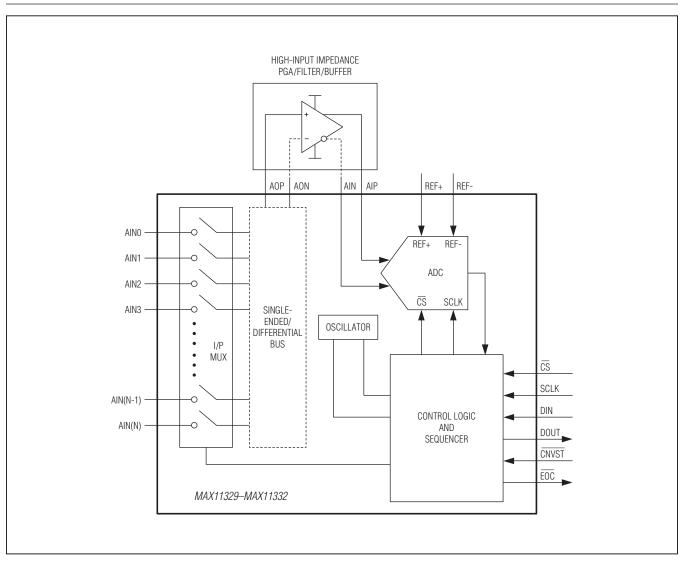

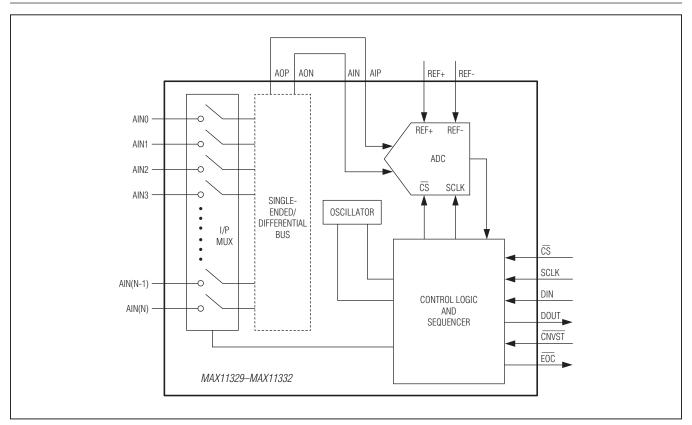

## **Functional Diagrams**

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

### Functional Diagrams (continued)

### **Detailed Description**

The MAX11329–MAX11332 are 12-/10-bit with external reference and industry-leading 500kHz, full linear bandwidth, high-speed, low-power, serial output successive approximation register (SAR) analog-to-digital converters (ADC). These devices feature scan mode, internal averaging to increase SNR, and AutoShutdown.

The external clock mode features the SampleSet technology, a user-programmable analog input channel sequencer. The user may define and load a unique sequencing pattern into the ADC allowing both high- and low-frequency inputs to be converted without interface activity. This feature frees the controlling unit for other tasks while lowering overall system noise and power consumption.

The MAX11329–MAX11332 include internal clock. The internal clock mode features an integrated FIFO, allowing data to be sampled at high speed and then held for readout at any time or at a lower clock rate. Internal averaging

is also supported in this mode improving SNR for noisy input signals. All input channels are configurable for single-ended, fully differential or pseudo-differential inputs in unipolar or bipolar mode. The MAX11329–MAX11332 operate from a 2.35V to 3.6V supply and consume only 15.2mW at 3Msps.

The MAX11329–MAX11332 include AutoShutdown, fast wake-up, and a high-speed 3-wire serial interface. The devices feature full power-down mode for optimal power management.

Data is converted from analog voltage sources in a variety of channel and data-acquisition configurations. Microprocessor ( $\mu$ P) control is made easy through a 3-wire SPI-/QSPI-/MICROWIRE-compatible serial interface.

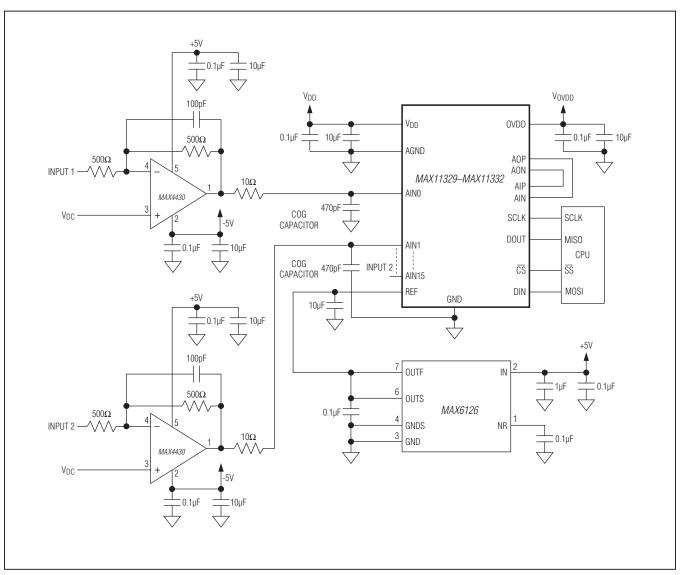

AOP and AON are the output pins of the internal multiplexer while AIP and AIN are the ADC inputs which are all accessible externally through pins. This allows flexibility to the system designer to process all signals through one PGA (programmable gain amplifier), filter or gain stage

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

in single-ended or differential configuration. The external buffering stage should be designed to properly drive the input sampling network of the ADC.

The external buffer should also have very high input impedance (low-leakage current) to ensure best linearity. If additional signal processing is not required, connect AOP to AIP and AON to AIN. It is recommended to limit the source impedance to not affect the sampling accuracy of the ADC causing degradation in linearity and total harmonic distortion. See the SINAD vs. Input Resistance graph in the *Typical Operating Characteristics*.

### **Input Bandwidth**

The ADC's input-tracking circuitry features a 500MHz small-signal full-linear bandwidth to digitize high-speed transient events and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques. Anti-alias filtering of the input signals is necessary to avoid high-frequency signals aliasing into the frequency band of interest.

### 3-Wire Serial Interface

The MAX11329–MAX11332 feature a serial interface compatible with SPI/QSPI and MICROWIRE devices. For SPI/QSPI, ensure the CPU serial interface runs in master

mode to generate the serial clock signal. Select the SCLK frequency of 48MHz or less, and set clock polarity (CPOL) and phase (CPHA) in the control registers to the same value. The MAX11329–MAX11332 operate with SCLK idling high, and thus operate with CPOL = CPHA = 1.

Set  $\overline{\text{CS}}$  low to latch input data at DIN on the rising edge of SCLK. Output data at DOUT is updated on the falling edge of SCLK. A high-to-low transition on  $\overline{\text{CS}}$  samples the analog inputs and initiates a new frame. A frame is defined as the time between two falling edges of  $\overline{CS}$ . There is a minimum of 16 bits per frame. The serial data input, DIN, carries data into the control registers clocked in by the rising edge of SCLK. The serial data output. DOUT, delivers the conversion results and is clocked out by the falling edge of SCLK. DOUT is a 16-bit data word containing a 4-bit channel address, followed by a 12-bit conversion result led by the MSB when CHAN\_ID is set to 1 in the ADC Mode Control register (Figure 2a). When CHAN\_ID is set to 1 keep the SCLK high for at least 25ns before the CS falling edge (Figure 2b). When CHAN\_ID is set to 0 (external clock mode only), the 16-bit data word includes a leading zero and the 12-bit conversion result is followed by 3 trailing zeros (Figure 2c). In the 10-bit conversion result is followed by 5 trailing zeros.

Figure 2a. External Clock Mode Timing Diagram with CHAN\_ID=1

Figure 2b. External Clock Mode Timing Diagram with CHAN\_ID=1 for Best Performance

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

Figure 2c. External Clock Mode Timing Diagram with CHAN\_ID=0

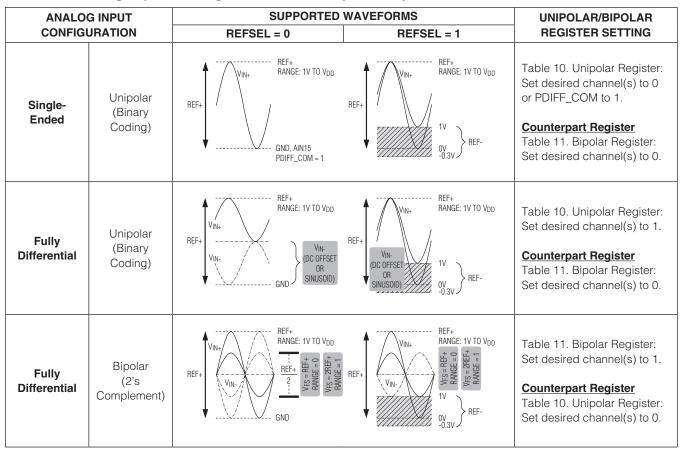

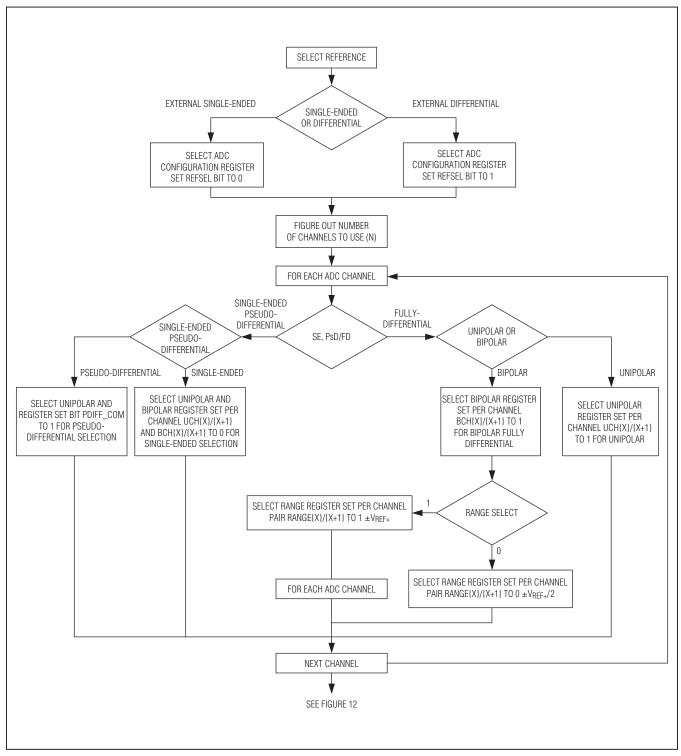

## Single-Ended, Differential, and Pseudo-Differential Input

The MAX11329–MAX11332 include up to 16 analog input channels that can be configured on a pin-by-pin basis to 16 single-ended inputs, 8 fully differential pairs, or 15 pseudo-differential inputs with respect to one common input (REF-/AIN15 is the common input).

The analog input range is 0V to  $V_{REF+}$  in single-ended and pseudo-differential mode (unipolar) and  $\pm V_{REF+}/2$  or  $\pm V_{REF+}$  in fully differential mode (bipolar) depending on the RANGE register settings. See <u>Table 7</u> for the RANGE register settings.

Unipolar mode sets the differential input range from 0 to  $V_{REF+}$ . If the positive analog input swings below the negative analog input in unipolar mode, the digital output code is zero. Selecting bipolar mode sets the differential input range to  $\pm V_{REF+}/2$  or  $\pm V_{REF+}$  depending on the RANGE register settings (Table 7).

In single-ended mode, the ADC always operates in unipolar mode. The analog inputs are internally referenced to GND with a full-scale input range from 0V to  $V_{REF+}$ . Single-ended conversions are internally referenced to GND (Figure 3).

The MAX11329–MAX11332 feature up to 15 pseudo differential inputs by setting the PDIFF\_COM bits in the Unipolar register to 1 (<u>Table 10</u>). The 15 analog input signals inputs are referenced to a DC signal applied to the REF-/AIN15.

### Fully Differential Reference (REF+, REF-)

When the reference is used in fully differential mode (REFSEL = 1), the full-scale range is set by the difference between REF+ and REF-. The output code reaches its

Figure 3. Equivalent Input Circuit

maximum value if the input signal exceeds this reference range.

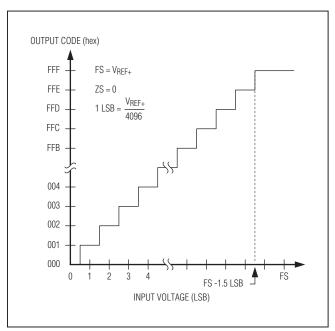

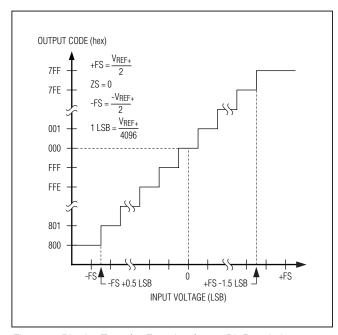

#### **ADC Transfer Function**

The output format of the MAX11329–MAX11332 is straight binary in unipolar mode and two's complement in bipolar mode. The code transitions midway between successive integer LSB values, such as 0.5 LSB, 1.5 LSB. Figure  $\underline{4}$  and Figure  $\underline{5}$  show the unipolar and bipolar transfer function, respectively. Output coding is binary, with for example, 1 LSB =  $V_{REF+}/4096$  in the 12-bit devices such as the MAX11331/MAX11332.

#### Internal FIFO

The MAX11329–MAX11332 contain a FIFO buffer that can hold up to 16 ADC results. This allows the ADC to handle multiple internally clocked conversions without tying up the serial bus. If the FIFO is filled and further conversions are requested without reading from the FIFO, the oldest ADC results are overwritten by the new ADC results. Each

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

Figure 4. Unipolar Transfer Function for 12-Bit Resolution

result contains 2 bytes, with the MSB preceded by four leading channel address bits. After each falling edge of  $\overline{\text{CS}}$ , the oldest available byte of data is available at DOUT. When the FIFO is empty, DOUT is zero.

### **External Clock**

Apply a soft reset when changing from internal to external clock mode: RESET [1:0] = 10. The detailed operation of external clock mode is dependent on the mode of operation selected for the device using SCAN[3:0] bit settings (see <u>Table 3</u>). In external clock mode the analog inputs are sampled at the falling edge of  $\overline{\text{CS}}$ . Serial clock (SCLK) is used to perform the conversion.

Depending on the mode selected, the sequencer reads in the channel to be converted from the serial data input (DIN) at each frame (e.g. manual mode). The conversion results are sent to the serial output (DOUT) at the next frame.

In other external clocked modes the sequence of channel to be converted is determined by the mode (SCAN[3:0]) selected in <u>Table 3</u>. See the <u>Applications Information</u> for more detail on programming modes.

Figure 5. Bipolar Transfer Function for 12-Bit Resolution

#### **Internal Clock**

Apply a soft reset when changing from internal to external clock mode: RESET [1:0] = 10. The MAX11329– MAX11332 operate from an internal oscillator, which is accurate within  $\pm 15\%$  of the 40MHz nominal clock rate. Request internally timed conversions by writing the appropriate sequence to the ADC Mode Control register (Table 2).

The wake-up, acquisition, conversion, and shutdown sequences are initiated through  $\overline{\text{CNVST}}$  and are performed automatically using the internal oscillator. Results are added to the internal FIFO.

With  $\overline{\text{CS}}$  high, initiate a scan by setting  $\overline{\text{CNVST}}$  low for at least 5ns before pulling it high (Figure 6). Then, the MAX11329–MAX11332 wake up, scan all requested channels, store the results in the FIFO, and shut down. After the scan is complete,  $\overline{\text{EOC}}$  is pulled low and the results are available in the FIFO. Wait until  $\overline{\text{EOC}}$  goes low before pulling  $\overline{\text{CS}}$  low to communicate with the serial interface.  $\overline{\text{EOC}}$  stays low until  $\overline{\text{CS}}$  or  $\overline{\text{CNVST}}$  is pulled low again. Do not initiate a second  $\overline{\text{CNVST}}$  before  $\overline{\text{EOC}}$  goes low; otherwise, the FIFO may become corrupted.

Figure 6. Internal Conversions with CNVST

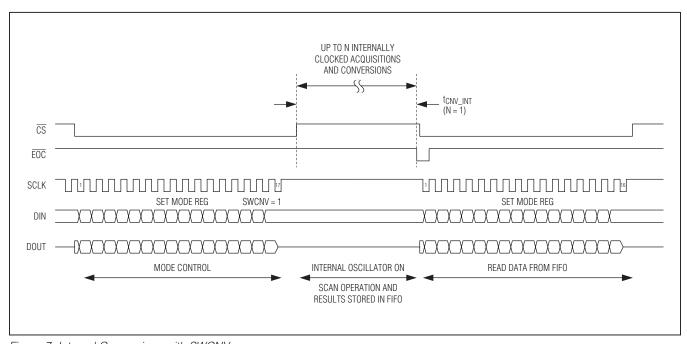

Figure 7. Internal Conversions with SWCNV

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

Alternatively, set SWCNV to 1 in the ADC Mode Control register (Figure 4) to initiate conversions with  $\overline{CS}$  rising edge instead of cycling  $\overline{CNVST}$  (Table 2). For proper operation,  $\overline{CS}$  must be held low for 17 clock cycles to guarantee that the device interprets the SWCNV setting. Wait until EOC goes low before pulling  $\overline{CS}$  low to communicate with the serial interface. Upon completing the conversion, SWCNV is reset to 0 (Figure 7).

### **Analog Input**

The MAX11329–MAX11332 produce a digital output that corresponds to the analog input voltage as long as the analog inputs are within the specified operating range. Internal protection diodes confine the analog input voltage within the region of the analog power input rails (V<sub>DD</sub>, GND) and allow the analog input voltage to swing from GND - 0.3V to V<sub>DD</sub> + 0.3V without damaging the device. Input voltages beyond GND - 0.3V and V<sub>DD</sub> + 0.3V forward bias the internal protection diodes. Limit the forward diode current to less than 50mA to avoid damage to the MAX11329–MAX11332.

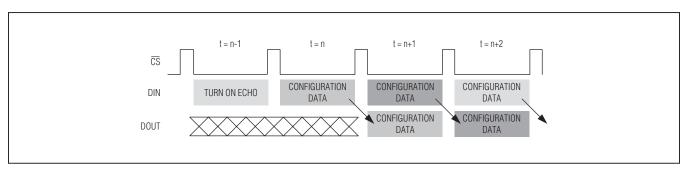

#### **ECHO**

When writing to the ADC Configuration register, set ECHO to 1 in ADC Configuration register to echo back the configuration data onto DOUT at time n+1 (Figure 8, Table 6).

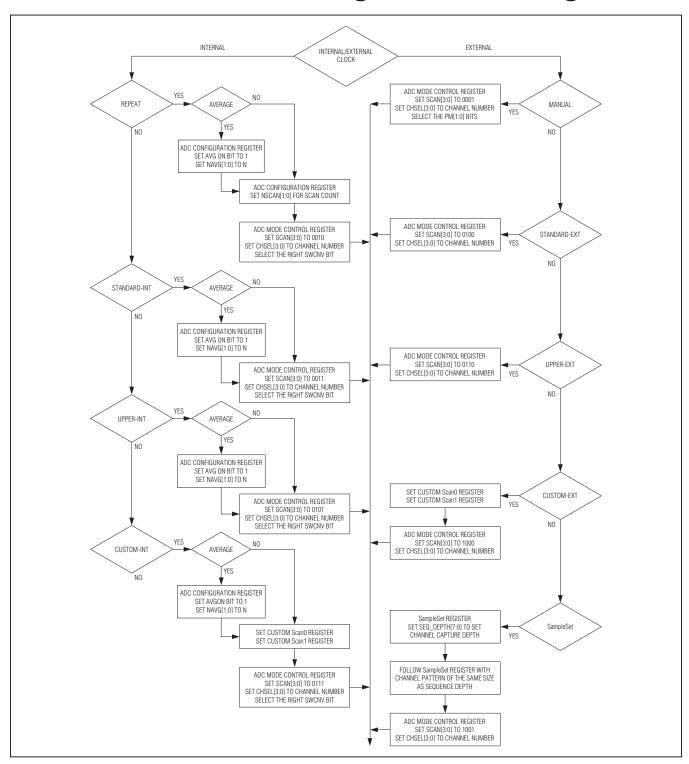

#### **Scan Modes**

The MAX11329-MAX11332 feature nine scan modes (Table 3).

### Manual Mode

The next channel to be selected is identified in each SPI frame. The conversion results are sent out in the next frame. The manual mode works with the external clock only. The FIFO is unused.

### Repeat Mode

Repeat scanning channel N for number of times and store all the conversion results in the FIFO. The number of scans is programmed in the ADC Configuration register. The repeat mode works with the internal clock only.

### Custom\_Int and Custom\_Ext

In Custom\_Int and Custom\_Ext modes, the device scans preprogrammed channels in ascending order. The channels to be scanned in sequence are programmed in the Custom Scan0 or Custom Scan1 registers (see <a href="Table 12">Table 13</a>). A new I/P MUX is selected every frame on the thirteenth falling edge of SCLK. Custom\_Int works with the internal clock. Custom\_Ext works with the external clock.

#### Standard Int and Standard Ext

In Standard\_Int and Standard\_Ext modes, the device scans channels 0 through N in ascending order where N is the last channel specified in the ADC Mode Control register. A new I/P MUX is selected every frame on the thirteenth falling edge of SCLK. Standard\_Int works with the internal clock. Standard\_Ext works with the external clock.

### Upper\_Int and Upper\_Ext

In Upper\_Int and Upper\_Ext modes, the device scans channels N through 15/11/7/3 in ascending order where N is the first channel specified in the ADC Mode Control register. A new I/P MUX is selected every frame on the thirteenth falling edge of SCLK. Upper\_Int works with the internal clock. Upper\_Ext works with the external clock.

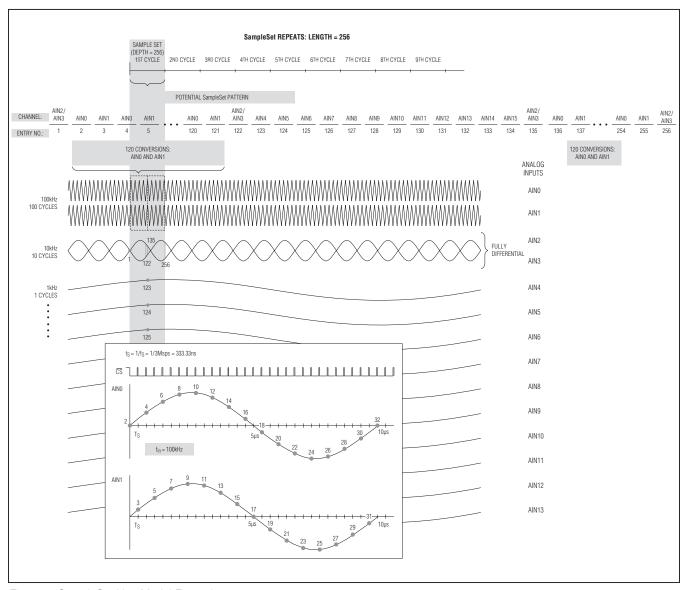

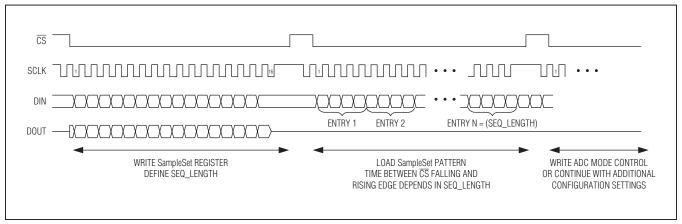

#### SampleSet

The SampleSet mode of operation allows the definition of a unique channel sequence combination with maximum length of 256. SampleSet is supported only in the external clock mode. SampleSet is ideally suited for multichannel measurement applications where some analog inputs must be converted more often than others.

Figure 8. Echo Back the Configuration Data

# 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

The SampleSet approach provides greater sequencing flexibility for multichannel applications while alleviating significant microcontroller communication overhead. SampleSet technology allows the user to exploit available ADC input bandwidth without need for constant communication between the ADC and controlling unit. The user may define and load a unique sequencing pattern into

the ADC allowing both high- and low-frequency inputs to be converted appropriately without interface activity. With the unique sequence loaded into ADC memory, the pattern may be repeated indefinitely or changed at any time

For example, the maximum throughput of MAX11329–MAX11332 is 3Msps. Traditional ADC scan modes allow

Figure 9. SampleSet Use-Model Example

## 3Msps, 12-/10-Bit, 8-/16-Channel ADCs with Post-Mux External Signal Conditioning Access

up to 16-channel conversions in ascending order. In this case, the effective throughput per channel is 3Msps/16 channel or 187.5ksps. The maximum input frequency that the ADC can resolve (Nyquist Theorem) is 93.75kHz. If all 16 channels must be measured, with some channels having greater than 93.75kHz input frequency, the user must revert back to manual mode requiring constant communication on the serial interface. SampleSet technology solves this problem. Figure 9 provides a SampleSet use-model example.

### Averaging Mode

In averaging mode, the device performs the specified number of conversions and returns the average for each requested result in the FIFO. The averaging mode works with internal clock only.

### Scan Modes and Unipolar/Bipolar Setting

When the Unipolar or Bipolar registers are configured as pseudo-differential or fully differential, the analog input pairs are repeated in this automated mode. For example, if N is set to 15 to scan all 16 channels and all analog input pairs are configured for fully-differential conversion, the ADC converts the channels twice. In this case, the user may avoid dual conversions on input pairs by implementing Manual mode or using Custom\_Int or Custom\_Ext scan modes and only scan even (or odd) channels (e.g. 0, 2, 4).

**Table 1. Register Access and Control**

| REGISTER NAME         |        | REGISTER |        | DIN = DATA INPUTS |        |            |

|-----------------------|--------|----------|--------|-------------------|--------|------------|

| REGISTER NAME         | BIT 15 | BIT 14   | BIT 13 | BIT 12            | BIT 11 | BIT [10:0] |

| ADC Mode Control      | 0      | DIN      | DIN    | DIN               | DIN    | DIN        |

| ADC Configuration     | 1      | 0        | 0      | 0                 | 0      | DIN        |

| Unipolar              | 1      | 0        | 0      | 0                 | 1      | DIN        |

| Bipolar               | 1      | 0        | 0      | 1                 | 0      | DIN        |

| RANGE                 | 1      | 0        | 0      | 1                 | 1      | DIN        |

| Custom Scan0          | 1      | 0        | 1      | 0                 | 0      | DIN        |

| Custom Scan1          | 1      | 0        | 1      | 0                 | 1      | DIN        |

| SampleSet             | 1      | 0        | 1      | 1                 | 0      | DIN        |

| Reserved. Do not use. | 1      | 1        | 1      | 1                 | 1      | DIN        |

**Table 2. ADC Mode Control Register**

| BIT NAME   | BIT            | DEFAULT<br>STATE | FUNCTION                                                                                                                              |                    |                                                         |  |