# Integrated 10/100 Ethernet MAC + PHY

## Features

- Single chip 10/100BASE, half or full duplex Ethernet Media Access Controller

- IEEE 802.3 compliant 100BASE-TX/100BASE-FX/10BASE-T

- PCI Bus master scatter/gather DMA on any byte boundary

- Full operation with PCI Clock from 25 MHz to 33 MHz

- PCI Revision 2.2 compliant

- On-chip transmit and receive FIFO buffers

- On-chip LED drivers

- Power management capabilities for ACPI 1.0 compliant systems

- WakeOnLAN support

- Management statistics gathering

- IP multicast receive and filter support using 64 bit hash table

- Transmit polling

- Auto pad insertion for short packets

- Programmable minimum Inter Packet Gap

- Supports auto MDI-MDIX function

- Smart Cable Analyzer (SCA) Support

- Capable of using 93C46 EEPROM

- On-chip crystal oscillator

- On-chip voltage regulator

- 2.5/3.3V CMOS with 5V tolerant I/O

- 0.25µm technology

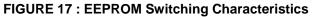

- 128-pin PQFP

- Support Lead Free package (Please refer to the Order Information)

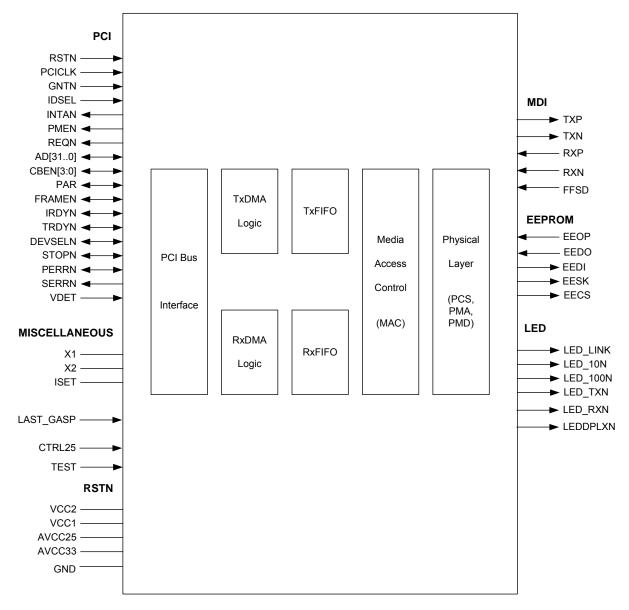

## **General Description**

The IP100A LF is a single-chip, full duplex, 10/100Mbps Ethernet MAC + PHY incorporating a 32-bit PCI with bus master support. The IP100A LF is designed for use in a variety of applications including workstation NICs, PC motherboards, and other systems utilizing a PCI bus that require network connectivity to an Ethernet or Fast Ethernet LAN.

The IP100A LF includes a PCI bus interface unit, IEEE 802.3 compliant MAC, transmit and receive FIFO buffers, IEEE 802.3 compliant 100BASE-TX, 10BASE-T, and 100BASE-FX PHY, serial EEPROM interface and LED drivers.

The IP100A LF implements a rich set of control and status registers. Accessible via the PCI interface, these registers provide a host system visibility into the features and operating state of the IP100A LF. Network management statistics are also recorded, and host access to registers of the PHY device are facilitated through the IP100A LF's PCI interface.

The IP100A LF supports features for use in "Green PCs" or systems where control over system power consumption is desired. The IP100A LF supports several power down states, and the ability to issue a system "wake event" via reception of unique, user defined Ethernet frames. In addition, the IP100A LF can assert a wake event in response to changes in the Ethernet link status

## **Block Diagram**

## Contents

| Cor | ntents                  |                                       | 3   |  |  |  |

|-----|-------------------------|---------------------------------------|-----|--|--|--|

| Re۱ | ision History           |                                       | 6   |  |  |  |

| 1   | <b>PIN Designations</b> | 5                                     | . 7 |  |  |  |

| 2   | PIN Diagram8            |                                       |     |  |  |  |

| 3   |                         |                                       |     |  |  |  |

| PIN |                         | ntinued)                              |     |  |  |  |

|     |                         | ntinued)                              |     |  |  |  |

| 4   |                         | lossary                               |     |  |  |  |

| 5   |                         | liance                                |     |  |  |  |

| 6   |                         |                                       |     |  |  |  |

| 0   |                         | iption                                | 10  |  |  |  |

|     | 6.1<br>6.2              | Media Access Control                  |     |  |  |  |

|     |                         | Physical Layer                        |     |  |  |  |

|     | 6.3                     | On-Chip Voltage Regulator             |     |  |  |  |

|     | 6.4                     | PCI Bus Interface                     |     |  |  |  |

|     | 6.5                     | TxDMA Logic                           |     |  |  |  |

|     | 6.6                     | TxFIFO                                |     |  |  |  |

|     | 6.7                     | RxDMA Logic                           |     |  |  |  |

|     | 6.8                     | RxFIFO                                |     |  |  |  |

|     | 6.9                     | EEPROM Interface                      |     |  |  |  |

| 7   | Operation               |                                       |     |  |  |  |

|     | 7.1                     | Initialization                        | 16  |  |  |  |

|     | 7.2                     | Register Programming                  |     |  |  |  |

|     | 7.3                     | TxDMA and Frame Transmission          | 17  |  |  |  |

|     | 7.4                     | Frame Reception and RxDMA             | 19  |  |  |  |

|     | 7.5                     | Interrupts                            | 22  |  |  |  |

| 8   | Statistics              | · · ·                                 | 22  |  |  |  |

|     | 8.1                     | Transmit Statistics                   | 22  |  |  |  |

|     | 8.2                     | Receive Statistics                    | 23  |  |  |  |

| 9   | PCI Bus Master (        | Operation                             |     |  |  |  |

| 10  |                         | ent                                   |     |  |  |  |

|     | 10.1                    | Wake Event                            |     |  |  |  |

|     | 10.2                    | Power Down                            |     |  |  |  |

| 11  |                         | ata Structures                        |     |  |  |  |

|     | 11.1                    | PHY Registers                         |     |  |  |  |

|     | 11.1.1                  | Control Register                      |     |  |  |  |

|     | 11.1.2                  | Status Register                       |     |  |  |  |

|     | 11.1.3                  | PHY Identifier 1                      |     |  |  |  |

|     | 11.1.4                  | PHY Identifier 2.                     |     |  |  |  |

|     | 11.1.5                  | Auto-Negotiation Advertisement        |     |  |  |  |

|     | 11.1.6                  | Auto-Negotiation Link Partner Ability |     |  |  |  |

|     | 11.1.7                  | Phy Specification Control Register    |     |  |  |  |

|     | 11.1.8                  | Phy Debug Control Register            |     |  |  |  |

|     | 11.1.8                  |                                       |     |  |  |  |

|     | 11.1.9                  | Phy Status Monitor Register           |     |  |  |  |

|     | 11.2                    | SCA Settings                          |     |  |  |  |

|     |                         | DMA Data Structures                   |     |  |  |  |

|     | 11.2.1                  | RxDMAFragAddr                         |     |  |  |  |

|     | 11.2.2                  | RxDMAFragLen                          |     |  |  |  |

|     | 11.2.3                  | RxDMANextPtr                          |     |  |  |  |

|     | 11.2.4                  | RxFrameStatus                         | 36  |  |  |  |

| 11.2.5  | TxDMAFragAddr                |    |

|---------|------------------------------|----|

| 11.2.6  | TxDMAFragLen                 |    |

| 11.2.7  | TxDMANextPtr                 |    |

| 11.2.8  | TxFrameControl               |    |

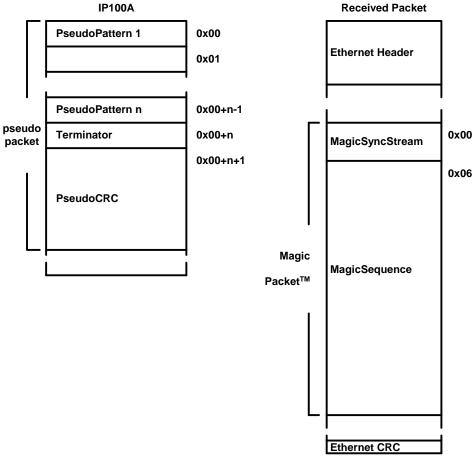

| 11.3    | Wake Event Data Structures   |    |

| 11.3.1  | MagicSequence                | 41 |

| 11.3.2  | MagicSyncStream              | 41 |

| 11.3.3  | PseudoCRC                    | 41 |

| 11.3.4  | PseudoPattern                | 42 |

| 11.3.5  | Terminator                   | 42 |

| 11.4    | LAN I/O Registers            | 43 |

| 11.4.1  | AsicCtrl                     | 44 |

| 11.4.2  | DMACtrl                      | 48 |

| 11.4.3  | EepromCtrl                   | 50 |

| 11.4.4  | EepromData                   | 51 |

| 11.4.5  | FIFOCtrl                     | 51 |

| 11.4.6  | HashTable                    | 52 |

| 11.4.7  | IntEnable                    | 52 |

| 11.4.8  | IntStatus                    | 53 |

| 11.4.9  | IntStatusAck                 |    |

| 11.4.10 | MACCtrl0                     |    |

| 11.4.11 | MACCtrl1                     | 56 |

| 11.4.12 | MaxFrameSize                 |    |

| 11.4.13 | PhyCtrl                      |    |

| 11.4.14 | ReceiveMode                  | 59 |

| 11.4.15 | RxDMABurstThresh             |    |

| 11.4.16 | RxDMAListPtr                 |    |

| 11.4.17 | RxDMAPollPeriod              |    |

| 11.4.18 | RxDMAStatus                  |    |

| 11.4.19 | RxDMAUrgentThresh            |    |

| 11.4.20 | StationAddress               |    |

| 11.4.21 | TxDMABurstThresh             |    |

| 11.4.22 | TxDMAListPtr                 |    |

| 11.4.23 | TxDMAPollPeriod              |    |

| 11.4.24 | TxDMAUrgentThresh            |    |

| 11.4.25 | TxReleaseThresh              |    |

| 11.4.26 | TxStatus                     |    |

| 11.4.27 | WakeEvent                    |    |

| 11.5    | Statistic Registers          |    |

| 11.5.1  | BroadcastFramesReceivedOk    |    |

| 11.5.2  | BroadcastFramesTransmittedOk |    |

| 11.5.3  | CarrierSenseErrors           |    |

| 11.5.4  | FramesAbortedDueToXSColls    |    |

| 11.5.5  | FramesLostRxErrors           |    |

| 11.5.6  | FramesReceivedOk             |    |

| 11.5.7  | FramesTransmittedOk          |    |

| 11.5.8  | FramesWithDeferredXmission   |    |

| 11.5.9  | FramesWithExcessiveDeferal   |    |

| 11.5.10 | LateCollisions               |    |

| 11.5.11 | MulticastFramesReceivedOk    |    |

| 11.5.12 | MulticastFramesTransmittedOk |    |

| 11.5.13 | MultipleCollisionFrames      |    |

| 11.5.14 | OctetsReceivedOk             |    |

| 11.5.15 | OctetsTransmittedOk          |    |

| 11.5.16 | SingleCollisionFrames        |    |

|         |                              |    |

IP100A LF Preliminary Data Sheet

| 11.0              |                                 |    |

|-------------------|---------------------------------|----|

| 11.6              | LAN PCI Configuration Registers |    |

| 11.6.1            | CacheLineSize                   |    |

| 11.6.2            | CapId                           |    |

| 11.6.3            | CapPtr                          |    |

| 11.6.4            | CISPointer                      |    |

| 11.6.5            | ClassCode                       |    |

| 11.6.6            | ConfigCommand                   |    |

| 11.6.7            | ConfigStatus                    |    |

| 11.6.8            | Data                            |    |

| 11.6.9            | DeviceId                        |    |

| 11.6.10           | ExpRomBaseAddress               |    |

| 11.6.11           | HeaderType                      |    |

| 11.6.12           | InterruptLine                   |    |

| 11.6.13           | InterruptPin                    |    |

| 11.6.14           | IoBaseAddress                   |    |

| 11.6.15           | LatencyTimer                    |    |

| 11.6.16           | MaxLat                          | 83 |

| 11.6.17           | MemBaseAddress                  | 83 |

| 11.6.18           | MinGnt                          | 84 |

| 11.6.19           | NextItemPtr                     | 84 |

| 11.6.20           | PowerMgmtCap                    | 85 |

| 11.6.21           | PowerMgmtCtrl                   | 86 |

| 11.6.22           | RevisionId                      | 86 |

| 11.6.23           | SubsystemId                     | 87 |

| 11.6.24           | SubsystemVendorld               | 87 |

| 11.6.25           | Vendorld                        | 87 |

| 11.7              | EEPROM Data Format              | 88 |

| 11.7.1            | AsicCtrl                        | 88 |

| 11.7.2            | ConfigParm                      | 89 |

| 11.7.3            | FunctionsCtrl                   |    |

| 11.7.4            | StationAddress                  |    |

| 11.7.5            | SubsystemId                     |    |

| 11.7.6            | SubsystemVendorld               |    |

| 12 Signal Require | ements                          |    |

| 12.1              | Absolute Maximum Ratings        |    |

| 12.2              | Operating Ranges                |    |

| 12.3              | AC Characteristics              |    |

| 12.4              | Thermal Data                    |    |

| 13 Order Informat | tion                            |    |

|                   | nsions                          |    |

| ,                 |                                 |    |

## **Revision History**

| Revision<br>Number | Date       | Revision                                                                                            |

|--------------------|------------|-----------------------------------------------------------------------------------------------------|

| Version 1.0        | 2003-06-25 | First Release                                                                                       |

| Version 10         | 2005-01-25 | 1. Add the order information for lead free package.                                                 |

| Version 11         | 2005-03-14 | 1. Modify pin name of Pin 17,18,20,21,22,24,35,43,48,49                                             |

| Version 12         | 2005-04-22 | 1. Describe EepromCtrl register bit 12 and bit 13 in detail                                         |

| Version 13         | 2005-05-19 | 1. Add IP100A thermal data                                                                          |

| Version 14         | 2005-10-20 | <ol> <li>Remove 93C56 and EEOP support.</li> <li>Modify FFSD pin definition, in page 11.</li> </ol> |

| Version 15         | 2006-04-27 | 1. Add "Support Auto MDI-MDIX function" description                                                 |

| Version 16         | 2006-10-18 | 1. Modify RxDMALastFrag pin description, in page 36.                                                |

| Version 17         | 2007-03-30 | <ol> <li>Modify Pin Diagram in page 8.</li> <li>Modify LED_LINK Pin Type in page 11</li> </ol>      |

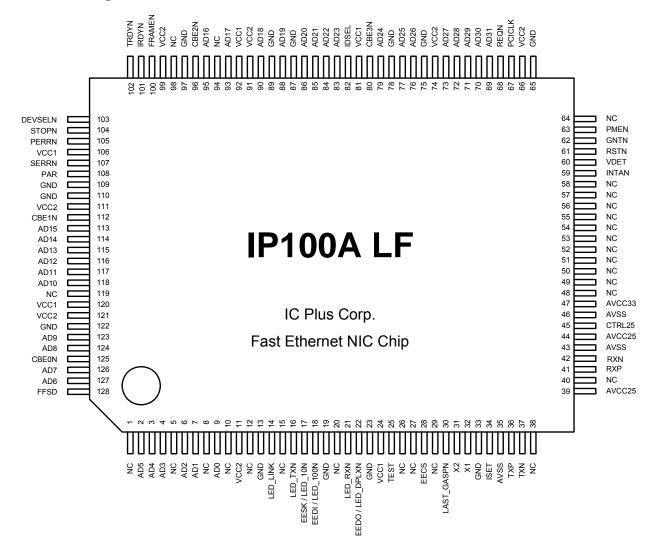

## **1 PIN Designations**

| PIN NO. | PIN NAME           | PIN NO. | PIN NAME | PIN NO. | PIN NAME | PIN NO. | PIN NAME |

|---------|--------------------|---------|----------|---------|----------|---------|----------|

| 1       | NC                 | 33      | GND      | 65      | GND      | 97      | GND      |

| 2       | AD5                | 34      | ISET     | 66      | VCC2     | 98      | NC       |

| 3       | AD4                | 35      | AVSS     | 67      | PCICLK   | 99      | VCC2     |

| 4       | AD3                | 36      | TXP      | 68      | REQN     | 100     | FRAMEN   |

| 5       | NC                 | 37      | TXN      | 69      | AD31     | 101     | IRDYN    |

| 6       | AD2                | 38      | NC       | 70      | AD30     | 102     | TRDYN    |

| 7       | AD1                | 39      | AVCC25   | 71      | AD29     | 103     | DEVSELN  |

| 8       | NC                 | 40      | NC       | 72      | AD28     | 104     | STOPN    |

| 9       | AD0                | 41      | RXP      | 73      | AD27     | 105     | PERRN    |

| 10      | NC                 | 42      | RXN      | 74      | VCC2     | 106     | VCC1     |

| 11      | VCC2               | 43      | AVSS     | 75      | GND      | 107     | SERRN    |

| 12      | NC                 | 44      | AVCC25   | 76      | AD26     | 108     | PAR      |

| 13      | GND                | 45      | CTRL25   | 77      | AD25     | 109     | GND      |

| 14      | LED_LINK           | 46      | AVSS     | 78      | GND      | 110     | GND      |

| 15      | NC                 | 47      | AVCC33   | 79      | AD24     | 111     | VCC2     |

| 16      | LED_TXN            | 48      | NC       | 80      | CBEN3    | 112     | CBEN1    |

| 17      | EESK /<br>LED_10N  | 49      | NC       | 81      | VCC1     | 113     | AD15     |

| 18      | EEDI /<br>LED_100N | 50      | NC       | 82      | IDSEL    | 114     | AD14     |

| 19      | GND                | 51      | NC       | 83      | AD23     | 115     | AD13     |

| 20      | NC                 | 52      | NC       | 84      | AD22     | 116     | AD12     |

| 21      | LED_RXN            | 53      | NC       | 85      | AD21     | 117     | AD11     |

| 22      | EEDO<br>/LED_DPLXN | 54      | NC       | 86      | AD20     | 118     | AD10     |

| 23      | GND                | 55      | NC       | 87      | GND      | 119     | NC       |

| 24      | VCC1               | 56      | NC       | 88      | AD19     | 120     | VCC1     |

| 25      | TEST               | 57      | NC       | 89      | GND      | 121     | VCC2     |

| 26      | NC                 | 58      | NC       | 90      | AD18     | 122     | GND      |

| 27      | NC                 | 59      | INTAN    | 91      | VCC2     | 123     | AD9      |

| 28      | EECS               | 60      | VDET     | 92      | VCC1     | 124     | AD8      |

| 29      | NC                 | 61      | RSTN     | 93      | AD17     | 125     | CBEN0    |

| 30      | LAST_GASPN         | 62      | GNTN     | 94      | NC       | 126     | AD7      |

| 31      | X2                 | 63      | PMEN     | 95      | AD16     | 127     | AD6      |

| 32      | X1                 | 64      | NC       | 96      | CBEN2    | 128     | FFSD     |

TABLE 1 : IP100A LF Pin Designations

## 2 PIN Diagram

## **3 PIN Descriptions**

| PIN NAME     | PIN TYPE | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                            |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI INTERFA  | CE       |                                                                                                                                                                                                                                                                                                                                            |

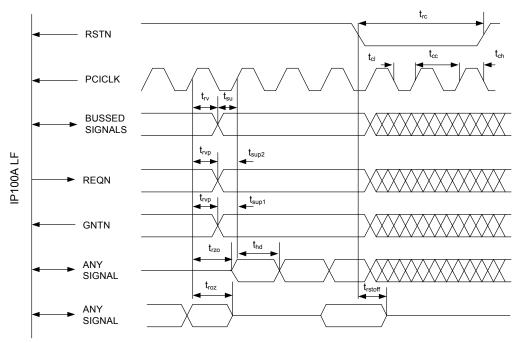

| RSTN         | INPUT    | Reset, asserted LOW. RSTN will cause the IP100A LF to reset all of its functional blocks. RSTN must be asserted for a minimum duration of 10 PCICLK cycles.                                                                                                                                                                                |

| PCICLK       | INPUT    | PCI Bus Clock. This clock is used to drive the PCI bus interfaces and the internal DMA logic. All bus signals are sampled on the rising edges of PCICLK. PCICLK can operate from 25MHz to 33MHz.                                                                                                                                           |

| GNTN         | INPUT    | PCI Bus Grant, asserted LOW. GNTN signals access to the PCI bus has been granted to IP100A LF.                                                                                                                                                                                                                                             |

| IDSEL        | INPUT    | Initialization Device Select. The IDSEL is used to select the IP100A LF during configuration read and write transactions.                                                                                                                                                                                                                  |

| INTAN        | OUTPUT   | Interrupt Request, asserted LOW. The IP100A LF asserts INTAN to request an interrupt, when any one of the programmed interrupt event occurs.                                                                                                                                                                                               |

| PMEN         | OUTPUT   | Wake Event, assertion level is programmable (see the WakePolarity bit of the WakeEvent register). The IP100A LF asserts PMEN to signal the detection of a wake event.                                                                                                                                                                      |

| REQN         | OUTPUT   | Request, asserted LOW. The IP100A LF asserts REQN to request PCI bus master operation.                                                                                                                                                                                                                                                     |

| AD<br>[310]  | IN/OUT   | PCI Bus Address/Data. Address and data are multiplexed on the AD pins.<br>The AD pins carry the physical address during the first clock cycle of a<br>transaction, and carry data during the subsequent clock cycles.                                                                                                                      |

| CBEN<br>[30] | IN/OUT   | PCI Bus Command/Byte Enable, asserted LOW. Bus command and byte<br>enables are multiplexed on the CBEN pins. CBEN specify the bus<br>command during the address phase transaction, and carry byte enables<br>during the data phase.                                                                                                        |

| PAR          | IN/OUT   | Parity. PCI Bus parity is even across AD[310] and CBEN[30]. The IP100A LF generates PAR during address and write data phases as a bus master, and during read data phase as a target. It checks for correct PAR during read data phase as bus master, during every address phase as a bus slave, and during write data phases as a target. |

| FRAMEN       | IN/OUT   | PCI Bus Cycle Frame, asserted LOW. FRAMEN is an indication of a transaction. It is asserted at the beginning of the address phase of the bus transaction and de-asserted before the final transfer of the data phase of the transaction.                                                                                                   |

| IRDYN        | IN/OUT   | Initiator Ready, asserted LOW. A bus master asserts IRDYN to indicate valid data phases on AD[310] during write data phases, indicates it is ready to accept data during read data phases. A target will monitor IRDYN.                                                                                                                    |

| TRDYN        | IN/OUT   | Target Ready, asserted LOW. A bus target asserts TRDYN to indicate valid read data phases, and to indicate it is ready to accept data during write data phases. A bus master will monitor TRDYN.                                                                                                                                           |

| STOPN        | IN/OUT   | Stop, asserted LOW. STOPN is driven by the slave target to inform the bus master to terminate the current transaction.                                                                                                                                                                                                                     |

## TABLE 2 : IP100A LF Pin Descriptions

## **PIN Descriptions (continued)**

| PIN NAME    | PIN TYPE                  | PIN DESCRIPTION                                                                                                                                                                                                                                                                      |  |  |  |

|-------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PCI INTERFA | PCI INTERFACE (continued) |                                                                                                                                                                                                                                                                                      |  |  |  |

| PERRN       | IN/OUT                    | Parity Error, asserted LOW. The IP100A LF asserts PERRN when it checks and detects a bus parity errors. When it is generating PAR output, the IP100A LF monitors for any reported parity error on PERRN.                                                                             |  |  |  |

| SERRN       | OUTPUT                    | System Error, asserted LOW.                                                                                                                                                                                                                                                          |  |  |  |

| VDET        | INPUT                     | Power Detect. The IP100A LF detects PCI bus power supply loss when VDET is LOW.                                                                                                                                                                                                      |  |  |  |

| EEPROM INT  | ERFACE                    |                                                                                                                                                                                                                                                                                      |  |  |  |

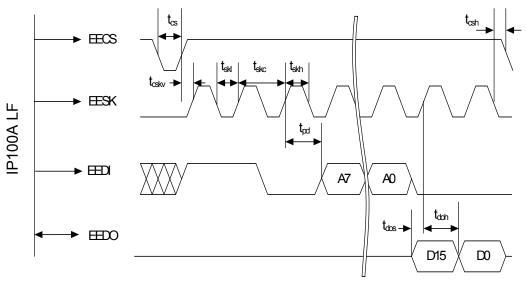

| EECS        | OUTPUT                    | EEPROM Chip Select. EECS is asserted by the IP100A LF to access the EEPROM. EECS is connected directly to the chip select input of the EEPROM device.                                                                                                                                |  |  |  |

| EESK        | OUTPUT                    | EEPROM Serial Clock. EESK is an output connected directly to the clock input of the EEPROM device.                                                                                                                                                                                   |  |  |  |

| EEDI        | OUTPUT                    | EEPROM Data Input. EEDI is an output connected directly to the data input of the EEPROM device. This pin is shared with LED100N pin.                                                                                                                                                 |  |  |  |

| EEDO        | INPUT                     | EEPROM Data Output. EEDO is an input connected directly to the data output of the EEPROM device. This pin is shared with Duplex LED pin.                                                                                                                                             |  |  |  |

| LED DRIVERS | 5                         |                                                                                                                                                                                                                                                                                      |  |  |  |

| LED_TXN     | OUTPUT                    | Transmit Status LED. This pin will stay LOW during transmission period and HIGH if no data or pulse is beening sent from IP100A LF.                                                                                                                                                  |  |  |  |

| LED_RXN     | OUTPUT                    | Receiving Status LED. This pin will stay LOW during receiving period and if no data has been received, the LED_RXN status will be HIGH.                                                                                                                                              |  |  |  |

| LED_DPLXN   | OUTPUT                    | Duplex Status LED. LED_DPLXN is the duplex status LED driver. The duplex status LED driver is LOW when the link is full duplex, and HIGH when the link is half duplex. Additional functionality of the speed status LED signal is based on the LEDMode bit of the AsicCtrl register. |  |  |  |

TABLE 2 : IP100A LF Pin Descriptions

## **PIN Descriptions (continued)**

| PIN NAME    | <b>PIN TYPE</b> | PIN DESCRIPTION                                                                                                                                                                                                                                                                     |

|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED DRIVERS | (continued)     |                                                                                                                                                                                                                                                                                     |

| LED_10N     | OUTPUT          | 10Mb/sec Connection Status LED. This pin will output LOW to indicate 10Mb/sec Transmission if the connection between 2 devices have negoatiated to link at 10Mb/sec.                                                                                                                |

| LED_100N    | OUTPUT          | 100Mb/sec Connection Status LED. This pin will output LOW to indicate 100Mb/sec Transmission if the connection between 2 devices have negoatiated to link at 100Mb/sec.                                                                                                             |

| LED_LINK    | OUTPUT          | Link Status LED. LED_LINK is the link status LED driver. The functionality of the link status LED signal is based on the LEDMode bit of the AsicCtrl register. A 4.7K pull-down resistor is placed between this pin and GND regardless of whether the LED is connected to this pin. |

| MDI         |                 |                                                                                                                                                                                                                                                                                     |

| RXP         | INPUT           | Receive input. When in 100BASE-TX mode, this receives MLT3 data from the isolation transformer. When in 100BASE-FX mode, this is a PECL input.                                                                                                                                      |

| RXN         | INPUT           | Receive input. When in 100BASE-TX mode, this receives MLT3 data from the isolation transformer. When in 100BASE-FX mode, this is a PECL input.                                                                                                                                      |

| ТХР         | OUTPUT          | Transmit output. When in 100BASE-TX mode, this is an MLT-3 driver. When in 100BASE-FX mode, this is a PECL driver.                                                                                                                                                                  |

| TXN         | OUTPUT          | Transmit output. When in 100BASE-TX mode, this is an MLT-3 driver. When in 100BASE-FX mode, this is a PECL driver.                                                                                                                                                                  |

| FFSD        | INPUT           | This pin is used to select TP or Fiber mode. For 100BASE-FX applications, FFSD is connected to the signal detect output pin of a fiber optic module at PECL level. Connecting this pin to GND will force the IP100A into TP mode.                                                   |

| MISCELLANE  | OUS             |                                                                                                                                                                                                                                                                                     |

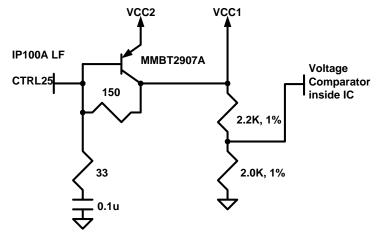

| CTRL25      | OUTPUT          | This is a controller pin to monitor correct 2.5V supply to IC.                                                                                                                                                                                                                      |

| LAST_GASPN  | INPUT           | This pin monitors the PCI voltage. If the voltage is dropped to certain value, LAST_GASPN will indicate IP100A LF to transmit LAST GASP frame to inform the other end that IP100A LF is not functioning till SYSTEM POWER ON or RESET.                                              |

| X1          | OSCIN           | 25MHz Crystal Oscillator Input. The external 25MHz crystal and capacitor is connected to the on-chip crystal oscillator circuit through X1 input. Alternately, X1 can be driven by an external clock source.                                                                        |

| X2          | OSCOUT          | 25MHz Crystal Oscillator Output. The external crystal and capacitor is also connected to the output of the on-chip crystal oscillator circuit through X2. When X1 is driven by an external clock source, X2 should be left unconnected.                                             |

| ISET        | ANALOG          | Band Gap Resistor. Connect a 6.2kohm, 1% resister between ISET and GND.                                                                                                                                                                                                             |

| TEST        | INPUT           | Test. Enables the IP100A LF test modes.                                                                                                                                                                                                                                             |

| NC          |                 | Reserved. These Pins must keep floating at application circuit.                                                                                                                                                                                                                     |

| POWER AND   | GROUND          |                                                                                                                                                                                                                                                                                     |

| VCC2        | POWER           | +3.3 volt I/O power supply.                                                                                                                                                                                                                                                         |

| VCC1        | POWER           | +2.5 volt digital logic power supply.                                                                                                                                                                                                                                               |

| AVCC25      | POWER           | +2.5 volt analog power supply.                                                                                                                                                                                                                                                      |

| AVCC33      | POWER           | +3.3 volt analog power supply.                                                                                                                                                                                                                                                      |

| AVSS        | GROUND          | Analog Ground                                                                                                                                                                                                                                                                       |

| PIN NAME | PIN TYPE | PIN DESCRIPTION |

|----------|----------|-----------------|

| GND      | GROUND   | Power return.   |

TABLE 2 : IP100A LF Pin Descriptions

## 4 Acronyms and Glossary

| LAN     | Local Area Network                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------|

| MAC     | Media Access Control Layer, or a device implementing the functions of this layer (a Media Access Controller) |

| PCI     | Peripheral Component Interface                                                                               |

| NIC     | Network Interface Cards                                                                                      |

| FIFO    | First In First Out                                                                                           |

| EPROM   | Erasable Programmable Read Only Memory                                                                       |

| EEPROM  | Electrically Erasable Programmable Read Only Memory                                                          |

| LED     | Light Emitting Diode                                                                                         |

| PHY     | Physical Layer, or device implementing functions of the Physical Layer                                       |

| CSMA/CD | Carrier Sense Multiple Access with Collision Detect                                                          |

| FCS     | Frame Check Sequence                                                                                         |

| SFD     | Start of Frame Delimiter                                                                                     |

| CRC     | Cyclic Redundancy Check                                                                                      |

| IP      | Internet Protocol                                                                                            |

| TFD     | Transmit Frame Descriptor                                                                                    |

| RFD     | Receive Frame Descriptor                                                                                     |

| DMA     | Direct Memory Access                                                                                         |

| ACPI    | Advanced Configuration and Power Management                                                                  |

|         |                                                                                                              |

## 5 Standards Compliance

The IP100A LF implements functionality compliant with the following standards:

- IEEE 802.3 Fast Ethernet

- IEEE 802.3 Full Duplex Flow Control

- PCI Local Bus Revision 2.2

- PCI Bus Power Management Interface Revision 1.1

- ACPI Revision 1.0

## 6 Functional Description

The IP100A LF is composed of various functional blocks as shown in Figure 1 on page 2. An overview of the functions performed by each block are as follows:

### 6.1 Media Access Control

The MAC block implements the IEEE Ethernet 802.3 Media Access Control functions with 802.3 Full Duplex and Flow Control enhancements. In half duplex mode, the MAC implements the CSMA/CD algorithm. Full duplex mode by definition does not utilize CSMA/CD, allowing data to be transmitted on demand. An optional flow control mechanism in full duplex mode is provided via the MAC Control PAUSE function. Additionally, the MAC also performs the following functions in either half or full duplex mode:

- Optional transmit FCS generation

- Padding to the minimum legal frame size

- Preamble and SFD generation

- Preamble and SFD removal

- Receive frame FCS checking and optional FCS stripping

- Receive frame destination address matching

- Support for multicast and broadcast frame reception or rejection (via filtering)

- Selective InterFrame Gap to avoid capture effect

- MAC Loopback

The MAC is responsible for generation of hardware signals to update the internal statistics counters.

### 6.2 Physical Layer

The IP100A LF supports both IEEE 802.3 100BASE-TX and 100BASE-FX signaling. The 100BASE-X transmit logic performs 4B5B encoding/decoding, parallel to serial, and serial to parallel conversion, and NRZ-NRZI signaling. In the case of 100BASE-TX, scrambling and MLT-3 encoding are also done before the data is transmitted on to the media. The receive 100BASE-X circuitry, recovering data from either an MLT-3 signal (100BASE-TX) or a PECL input (100BASE-FX), generates four bit nibbles to send to the MAC.

The Media Dependent Interface selection is done by the FFSD pin. If the FFSD pin is connected directly to GND, the IP100A LF PHY layer is operating in TX mode. If FFSD is connected to the signal detect, then the PHY layer is in 100BASE-FX mode.

The IP100A LF PHY also includes a full set of registers for controlling the PHY as outlined in the IEEE 802.3 specification.

### 6.3 On-Chip Voltage Regulator

The IP100A LF has an integrated voltage regulator for reduced system cost. The voltage regulator is used to provide the 2.5 V power to the PCB. When used with a 2N2905 PNP transistor based circuit as shown in Figure 2, the CTRL25 pin will regulate the current through the transistor, providing a stable 2.5 V reference.

FIGURE 2: External PNP Transistor Based Regulator Circuit

### 6.4 PCI Bus Interface

The PCI Bus Interface implements the protocols and signals needed to operate the IP100A LF in a PCI bus. The IP100A LF can be either a PCI bus master or slave. The PCI Bus Interface is also responsible for managing the DMA interfaces and the host processors access to the IP100A LF registers. Arbitration logic within the PCI Bus Interface block accepts bus requests from the TxDMA Logic and RxDMA Logic.

The PBI also manages interrupt generation for a host processor.

### 6.5 TxDMA Logic

The IP100A LF supports a multi-frame, multi-fragment DMA gather process. Descriptors representing frames are built and linked in system memory by a host processor. The TxDMA Logic is responsible for transferring the multi-fragment frame data from the host memory into the TxFIFO.

The TxDMA Logic monitors the amount of free space in the TxFIFO, and uses this value to decide when to request a TxDMA. A TxDMABurstThresh register is used to delay the bus request until there is enough free space in the TxFIFO for a long burst.

To prevent a TxFIFO under run condition the TxDMA logic forwards an urgent request to the arbiter, regardless of the TxDMABurstThresh constraint, when the number of occupied bytes in the TxFIFO drops below the value in TxDMAUrgentThresh register.

#### 6.6 TxFIFO

The IP100A LF uses 2K bytes of transmit data buffer between the TxDMA Logic and Transmit MAC. When the TxDMA logic determines there is enough space available in the TxFIFO, the TxDMA Logic will move any pending frame data into the TxFIFO. The TxReleaseThresh register value determines the amount of data which must be transmitted out of the TxFIFO before the FIFO memory space occupied by that data can be released for use by another frame.

A TxReleaseError occurs when a frame experiences a collision after the TxFIFO release threshold has been crossed. The IP100A LF will not be able to retransmit this frame from the TxFIFO and the complete frame must be transferred from the host system memory to the TxFIFO again by TxDMA Logic.

#### 6.7 RxDMA Logic

The IP100A LF supports a multi-frame, multi-fragment DMA scatter process. Descriptors representing frames are built and linked in system memory by the host processor. The RxDMA Logic is responsible for transferring the frame data from the RxFIFO to the host memory.

The RxDMA Logic monitors the number of bytes in the RxFIFO. After a number of bytes have been received, the frame is "visible". A frame is visible if:

- The frame being received is determined not to be a runt, OR

- The entire frame has been received

After a frame becomes visible, the RxDMA Logic will issue a request to the arbiter when the number of bytes in the RxFIFO is greater than the value in the RxDMABurstThresh. To prevent receive overruns, a RxDMA Urgent Request is made when the amount of free space in the RxFIFO falls below the value in RxDMAUrgentThresh.

#### 6.8 RxFIFO

The IP100A LF uses 2K bytes of receive data buffer between the Receive MAC and RxDMA Logic. The values in RxDMABurstThresh determine how many bytes of a frame must be received into RxFIFO before RxDMA Logic is allowed to begin data transfer.

#### 6.9 EEPROM Interface

The external serial EEPROM is used for non-volatile storage of such information as the node address, system ID, and default configuration settings. As part of initialization after system reset, the IP100A LF reads from the EEPROM and places the data into certain host-accessible registers. IP100A LF is able to read and write to 93LC46 series EEPROM. The correct connection is shown in section 17.2.

## 7 Operation

### 7.1 Initialization

The IP100A LF provides several resets. The assertion of the hardware reset signal on the PCI bus causes a complete reset of the IP100A LF. A similar reset is available via software using the GlobalReset bit of the AsicCtrl register. The AsicCtrl register also allows for selective reset of particular functional blocks of the IP100A LF. See the Registers and Data Structures section for details on using the AsicCtrl register for resetting the IP100A LF.

Shortly after reset, the IP100A LF will read the contents of an external EEPROM, placing the data read into the following registers:

- ConfigParm

- AsicCtrl (least significant 16 bits)

- SubsystemVendorld

- SubsystemId

- StationAddress

- Data

There are several other registers which must be configured by the host during initialization. These registers include the IP100A LF PCI configuration registers which are set during a Power On Self Test (POST) routine performed by the host system. Specifically, the registers set during this stage of initialization are:

- ConfigCommand enables adapter operation by allowing it to respond to and generate PCI bus cycles. ConfigCommand is also used to enable parity error generation.

- IoBaseAddress sets the I/O base address for the IP100A LF registers.

- MemBaseAddress sets the memory base address for the IP100A LF registers.

- ExpRomBaseAddress sets the base address and size for an installed expansion ROM, if any.

- CacheLineSize indicates the system's cache line size. This value is used by the IP100A LF to optimize bus master data transfers.

- LatencyTimer sets the length of time the IP100A LF can hold the PCI bus as a bus master.

- InterruptLine maps IP100A LF's interrupt request to a specific interrupt line (level) on the system board.

- AsicCtrl is used to setup internal operations and parameters.

The IP100A LF can be accessed across the PCI bus without setting the PCI registers or loading data from an external EEPROM. In this Forced Configuration mode (useful for embedded applications without an EEPROM), the IP100A LF is configured as follows:

- I/O base address 0x200

- I/O target cycles enabled

- Memory target cycles disabled

- Bus master cycles enabled

### 7.2 Register Programming

After initialization, an additional set of registers specific to operation of the Ethernet network must be programmed.

The first setting relates to the Auto-Negotiation function. The IP100A LF PHY layer performs the Auto-Negotiation process, and the host system must communicate with the PHY to determine the link status. Once the result of Auto-Negotiation is determined, if a full duplex mode has been chosen, the host system must set the FullDuplexEnable bit in the MACCtrl0 register. Other modes chosen during Auto-Negotiation do not require any IP100A LF register settings.

The ReceiveMode register determines which types of frames, based on address matching mechanism, the IP100A LF will receive. The end station address is loaded from the EEPROM, or the host system can

set the address directly. Then, by setting the ReceiveUnicast bit in the ReceiveMode register, the IP100A LF will receive unicast frames whose destination address matches the value in the StationAddress register.

The ReceiveMulticastHash bit in ReceiveMode enables a filtering mechanism for Ethernet multicast frames. This filtering mechanism uses a 64-bit hash table (HashTable register) for selective reception of Ethernet multicast frames.

Additionally, Ethernet frames containing IP multicast destination addresses can also be received by setting the ReceiveIPMulticast bit in the ReceiveMode register. IP multicast, or Host Extension for IP Multicasting, datagrams map to frames with Ethernet destination addresses of 0x01005e\*\*\*\*\*\* (where \* represents any hexadecimal value).

The MACCtrl0 and MACCtrl1 registers are used to configure parameters including full duplex, flow control, and statistics gathering.

In half duplex mode, the IP100A LF implements the CSMA/CD algorithm. If multiple nodes on the same network attempt to transmit simultaneously, a collision will occur resulting in re-transmission. In full duplex mode, the IP100A LF can transmit and receive frames simultaneously without incurring collisions. To configure the IP100A LF for full duplex mode operation, the host system must detect a full duplex physical link via the PHY Status Register, and must set the FullDuplexEnable bit in the MACCtrl0 register.

The IEEE 802.3x Full Duplex standard defines a special frame known as the PAUSE MAC Control frame. The PAUSE frame is used to implement flow control in full duplex networks allowing stations on opposite ends of a full duplex link the ability to inhibit transmission of data frames for a specified period of time. The PAUSE frame format is defined as shown in Figure 3.

| DA            | FIELD<br>0x01800 | C2000001 | LENGTH<br>(BYTES)<br>6 |

|---------------|------------------|----------|------------------------|

| SA            |                  |          | 6                      |

| TYPE          |                  | 0x8808   | 2                      |

| OPCODE 0x0001 |                  |          | 2                      |

| PAUSE TIME    |                  |          | 2                      |

| PAD           |                  |          | 42                     |

|               |                  |          |                        |

FIGURE 3: PAUSE Frame

Whenever the FlowControlEnable bit in the MACCtrl0 register is set, the IP100A LF looks for any incoming PAUSE frame. If found, the IP100A LF inhibits transmission of all data frames for the time specified in the two-byte pause\_time field. The pause\_time field is specified in slot times relative to the current data rate; one slot time is 51.2 us at 10 Mbps, and 5.12 us at 100 Mbps. The transmission of PAUSE frames is the responsibility of the host. The MAC Control frame must be constructed by the host and placed into the TxFIFO. For end station applications, host system should only accept PAUSE frames, and not generate them. Flow control is designed to originate from network devices such as switches.

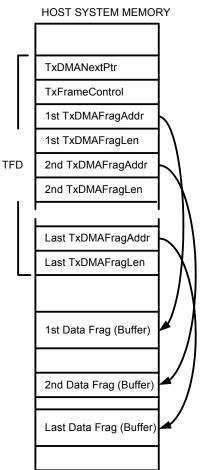

### 7.3 TxDMA and Frame Transmission

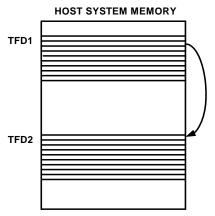

The TxDMA Logic transfers frame data from the host system memory to the IP100A LF based on a

linked list of frame descriptors called TFDs. The host system creates a list of TFDs in system memory, where each TFD contains the memory locations of one or more fragments of a frame as shown in Figure 4.

FIGURE 4: TxDMA Data Structure

The TFD format is covered in the Registers and Data Structures section.

The resulting linked list of TFDs is referred to as the TxDMAList, as shown in Figure 5.

In the simple case of a single frame, the host system must create a TFD within the host system memory containing the addresses and lengths of the fragments of data to be transmitted. The host system must write zero into TxDMANextPtr since this is the only frame. The host starts the TxDMA Logic by writing the memory location (a non-zero address) of the TFD into TxDMAListPtr register. The TxDMA Logic begins transferring data into the IP100A LF.

The IP100A LF first fetches the fragment addresses and fragment lengths from the TFD and writes them one at a time into registers, which are used to control the data transfer operations. If the TxDMA Logic transfers more data than can fit into the TxFIFO, an overrun will occur.

The TxDMAListPtr I/O register within the IP100A LF contains the physical address that points to the head of the TxDMAList. TxDMAListPtr must point to addresses which are on 8-byte boundaries. A value of zero in the TxDMAListPtr register implies there are no pending TFD's for the IP100A LF to process.

Generally, it is desirable for the host system to queue multiple frames. Multiple TFD's are linked together in a list by pointing the TxDMANextPtr of each TFD at the next TFD. The last TFD in the linked list should have a value of zero for it's TxDMANextPtr.

The TxDMA process returns to the idle state upon detection of a zero value for TxDMANextPtr. When a new frame is available to transfer, the host system must write the address of the new TFD into the TxDMANextPtr memory location of the last TFD, and either set the TxEnable bit, or utilize the IP100A LF's automatic polling capability. Using automatic polling, the IP100A LF will monitor the TxDMANextPtr memory location until a non-zero value is found at that location in system memory. The TxDMAPollPeriod register controls this polling function, which is enabled when TxDMAPollPeriod contains a non-zero value. The value written to TxDMAPollPeriod determines the TxDMANextPtr polling interval.

In response to a TxDMAComplete interrupt, when data transfer by TxDMA is finished, the host acknowledges the interrupt and returns the frame data buffers to the system. In the case of a multi-frame TxDMAList, multiple frames may have been transferred by TxDMA when the host system enters its interrupt service routine. The host system can traverse the list of TFD's, examining the TxDMAComplete bit in each TFD to determine which frames have been transferred by TxDMA.

The IP100A LF fetches the TFC before frame data transfer, and again at the end of TxDMA operation to examine the TxDMAIndicate bit. This allows the host system to change TxDMAIndicate while data transfer of the frame is in progress. For instance, a frame's TFD might be at the end of the TxDMAList when it starts TxDMA, so the host system would probably set TxDMAIndicate to generate an interrupt. However, if during the TxDMA process of this frame, the host system added a new TFD to the end of the list, it might clear TxDMAIndicate in the currently active TFD so that the interrupt is delayed until the next TFD.

The IP100A LF has the ability to automatically round up the length of a transmit frame. This is useful in some NOS environments in which frame lengths need to be an even number of words. The frame length is rounded up to either a word or dword boundary, depending upon the value of WordAlign. Host systems may disable frame length word-alignment by setting the WordAlign bits in the TransmitFrameControl to x1.

The MAC will initiate frame transmission (if transmission is enabled) as soon as either the entire frame is resident in the TxFIFO register.

As a frame transmits out of the TxFIFO, it is desirable to be able to release the FIFO space so that it may be used for another frame. The value programmed into TxReleaseThresh determines how much of a frame must be transmitted before its FIFO space can be released.

### 7.4 Frame Reception and RxDMA

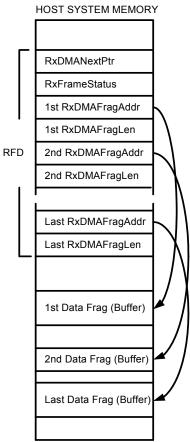

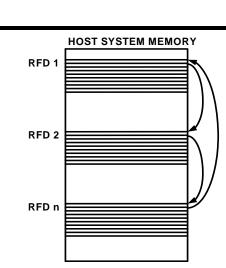

The frame RxDMA mechanism is similar to the TxDMA mechanism. RxDMA is structured around a

linked list of frame descriptors, called RFDs. RFDs contain pointers to the fragment buffers into which the IP100A LF is to place receive data, as shown in Figure 6.

FIGURE 6: RxDMA Data Structure

The RFD format is covered in the Registers and Data Structures section.

Similar to TFDs, the resulting linked list of RFDs is referred to as the RxDMAList. One option available to RxDMA that differs from TxDMA is that the RxDMAList can be formed into a ring as shown in Figure 7. A host system can allocate a number of full size frame buffers, create a RFD for each one, and link the RFDs into a circular list. As frames are received and transferred by RxDMA, a RxDMAComplete interrupt will be generated for each frame.

FIGURE 7: RxDMA List Shown in Ring

The host system must create a RxDMAList and the associated buffers prior to reception of a frame. One approach calls for the host system to allocate a block of full size (i.e. large enough to hold a maximum size Ethernet frame of 1518 bytes) frame buffers in system data space and create RFDs that point to them. Another approach is for the host system to request the buffers from the protocol ahead of time.

After reset, the IP100A LF receive function is disabled. Once the RxEnable bit is set, frames will be received according to the matching mode programmed in ReceiveMode register. Reception can be disabled by setting the RxDisable bit. If set while a frame is being received, RxDisable only takes effect after the active frame reception is finished. The receive function begins with the RxDMA Logic in the idle state. The RxDMA Logic will begin processing a RxDMAList as soon as a non-zero address is written into the RxDMAListPtr register. The host system creates a RFD with the addresses and lengths of the buffers to be used and programs the RxDMAListPtr register to point to the head of the list. The host system must program a zero into the RxDMANextPtr of the last RFD to indicate the end of the RxDMAList. When a frame is received in the RxFIFO, the IP100A LF fetches the fragment address and fragment length values one by one from the current RFD, and writes these values into internal registers which controli¥Á 9  $\emptyset R_{\dot{c}}$  -!

Textiling Od/a Lif Rad bit Point guided to generate host system has finished from P100Aster has haspone to determine which the point of the RFD from which the host system has finished from P100Aster has haspone to determine which the point of the point

In some host systems, it may be desirable to copy received frame data out of the scatter buffer to the protocol buffer while the frame is still being transferred by RxDMA. The RxDMAStatus register is provided for this purpose. If the host system sets the RxDMAHalt bit in the DMACtrl register, reads the RxDMAListPtr register and the RxDMAStatus register, then sets the RxDMAResume bit in the DMACtrl register, the host system can determine how much of the frame has been transferred by RxDMA. The RxDMAStatus register indicates the number of bytes transferred by RxDMA for the current RFD pointed to by the RxDMAListPtr register. The host system can then perform memory copies out of the RFD buffer concurrently with the RxDMA operation.

## 7.5 Interrupts

The term "interrupt" is used loosely to refer to interrupts and indications. An interrupt is the actual assertion of the hardware interrupt signal on the PCI bus. An indication, or a set bit in the IntStatus register, is the reporting of any event enabled by the host. The host system will configure the IP100A LF to generate an interrupt for any indication that is of interest to it. There are 10 different types of interrupt indications that can be generated by the IP100A LF. The IntEnable register controls which of the 10 indication bits can assert a hardware interrupt. In order for an indication bit to be allowed to generate an interrupt, its corresponding bit-position in IntEnable must be set. When responding to an interrupt, the host reads the IntStatus register to determine the cause of the interrupt. The least significant bit of IntStatus, InterruptStatus, is always set whenever any of the interrupts are asserted. InterruptStatus must be explicitly acknowledged (cleared) by writing a 1 into the bit in order to prevent spurious interrupts on the host bus.

Interrupts are acknowledged by the host carrying out various actions specific to each interrupt.

## 8 Statistics

The IP100A LF implements 16 statistics counters of various widths. Each statistic implemented complies to the corresponding definition given in the IEEE 802.3 standard. Setting the StatisticsEnable bit in the MACCtrl1 register enables the gathering of statistics. Reading a statistics register will clear the read register. Statistic registers may be read without disabling statistics gathering. For diagnostics and testing purposes, the host system may write a value to a statistic register, in which case the value written is added to the current value of the register. Whenever one or more of the statistics registers reaches 75% of its maximum value, an UpdateStats interrupt is generated. Reading that statistics register will acknowledge the UpdateStats interrupt. A summary of the transmit and receive statistics follows. Detailed descriptions of the statistic registers related to data transmission and reception can be found in the Registers and Data Structures section.

### 8.1 Transmit Statistics

- FramesTransmittedOk: The number frames of all types transmitted without errors. Loss of carrier is not considered to be an error by this statistic.

- BroadcastFramesTransmittedOk: The number of frames with broadcast destination address that are transmitted without errors.

- MulticastFramesTransmittedOk: The number of frames with multicast destination address that are transmitted without errors.

- OctetsTransmittedOk: The number of total octets for all frames transmitted without error.

- FramesWithDeferredXmission: A count of frames whose transmission was delayed on it's first attempt because network traffic.

- FramesWithExcessiveDeferral: If the transmission of a frame has been deferred for an excessive period of time due to network traffic, the event is recorded in this statistic.

- SingleCollisionFrames: Frames that are transmitted without errors after one and only one collision (including late collisions) are counted by this register.

- MultipleCollisionFrames: All frames transmitted without error after experiencing from 2 through 15 collisions (including late collisions) are counted here.

- LateCollisions: Every occurrence of a late collision (there could be more than one per frame transmitted) is counted by this statistic.

- FramesAbortedDueToXSColls: If the transmission of a frame had to be aborted due to excessive collisions, the event is recorded in this statistic.

- CarrierSenseErrors: Frames that were transmitted without error but experienced a loss of carrier are counted by this statistic.

#### 8.2 Receive Statistics

- FramesReceivedOk: Frames of all types that are received without error are counted here.

- BroadcastFramesReceivedOk: Frames of broadcast destination address that are received without error are counted here.

- MulticastFramesReceivedOk: Frames of multicast destination address that are received without error are counted here.

- OctetsReceivedOk: A total octet count for all frames received without error.

- FramesLostRxErrors: This is a count of frames that would otherwise be received by the IP100A LF, but could not be accepted due to an overrun condition in the RxFifo.

## 9 PCI Bus Master Operation

The IP100A LF supports all of the PCI memory commands and decides on a burst-by-burst basis which command to use in order to maximize bus efficiency. The list of PCI memory commands is shown below. For all commands, "read" and "write" are with respect to the IP100A LF (i.e. read implies the IP100A LF obtains information from an off-chip location, write implies the IP100A LF sends information to an off-chip location).

- Memory Read (MR)

- Memory Read Multiple (MRM).

- Memory Write (MW)

- Memory Write Invalidate (MWI)

MR is used for all fetches of descriptor information. For reads of transmit frame data, MR, or MRM is used, depending upon the remaining number of bytes in the fragment, the amount of free space in the TxFIFO, and whether the RxDMA Logic is requesting a bus master operation.

MW is used for all descriptor writes. Writes of receive frame data use either MW or MWI, depending upon the remaining number of bytes in the fragment, the amount of frame data in the RxFIFO, and whether the TxDMA Logic is requesting a bus master operation.

The IP100A LF provides three configuration bits to control the use of advanced memory commands. The MWIEnable bit in the ConfigCommand configuration register allows the host to enable or disable the use of MWI. The MWIDisable bit in DMACtrl allows the host system the ability to disable the use of MWI. MWIDisable is cleared by default, enabling MWI.

The IP100A LF provides a set of registers that control the PCI burst behavior. These registers allow a trade-off to be made between PCI bus efficiency and under run/overrun frequency. Arbitration logic within the PCI Bus Interface block accepts bus requests from the TxDMA Logic and RxDMA Logic. The TxDMA Logic uses the TxDMABurstThresh register, as described in the TxDMA Logic section, to delay the bus request until there is enough free space in the TxFIFO for a long, efficient burst. The TxDMA Logic can also make an urgent bus request as described in the TxDMA Logic section, where burst efficiency is sacrificed in favor of avoiding a TxFIFO under run condition.

The RxDMA process is described in the RxDMA Logic section. Typically, RxDMA requests will be forwarded to the Arbiter, however RxDMA Urgent Requests are also possible in order to prevent RxFIFO overruns.

## **10** Power Management

The IP100A LF supports operating system directed power management according to the ACPI specification. Power management registers in the PCI configuration space, as defined by the PCI Bus Power Management Interface specification, Revision 1.0 are described in 10.0.

The IP100A LF supports several power management states. The PowerState field in the PowerMgmtCtrl register determines IP100A LF's current power state. The power states are defined as follows:

- D0 Uninitialized (power state 0) is entered as a result of hardware reset, or after a transition from D3 Hot to D0. This state is the same as D0 Active except that the PCI configuration registers are uninitialized. In this state, the IP100A LF is unable to respond to PCI I/O, memory and configuration cycles and can not operate as a PCI master The IP100A LF cannot signal wake (PMEN) from the D0 state.

- D0 Active (power state 0) is the normal operational power state for the IP100A LF. In this state, the PCI configuration registers have been initialized by the system, including the IoSpace, MemorySpace, and Bus-Master bits in ConfigCommand, so the IP100A LF is able to respond to PCI I/O, memory and configuration cycles and can operate as a PCI master. The IP100A LF cannot signal wake (PMEN) from the D0 state.

- D1 (power state 1) is a "light-sleep" state. The IP100A LF optionally supports this state determined by the D1Support bit in the ConfigParm word in EEPROM. The D1 state allows transition back to D0 with no delay. In this state, the IP100A LF responds to PCI configuration accesses, to allow the system to change the power state. In D1 the IP100A LF does not respond to any PCI I/O or memory accesses. The IP100A LF's function in the D1 state is to recognize wake events and link state events and pass them on to the system by asserting the PMEN signal on the PCI bus.

- D2 (power state 2) is a partial power-down state. The IP100A LF optionally supports this state determined by the D2Support bit in the ConfigParm word in EEPROM. D2 allows a faster transition back to D0 than is possible from the D3 state. In this state, the IP100A LF responds to PCI configuration accesses, to allow the system to change the power state. In D2 the IP100A LF does not respond to any PCI I/O or memory accesses. The IP100A LF's function in the D2 state is to recognize wake events and link state events and pass them on to the system by asserting the PMEN signal on the PCI bus.

- D3 Hot (power state 3) is the full power-down state for the IP100A LF. In D3 Hot, the IP100A LF loses all PCI configuration information except for the value in PowerState. In this state, the IP100A LF responds to PCI configuration accesses, to allow the system to change the power state back to D0 Uninitialized. In D3 hot, the IP100A LF does not respond to any PCI I/O or memory accesses. The IP100A LF's main responsibility in the D3 Hot state is to recognize wake events and link state events and signal those to the system by asserting the PMEN signal on the PCI bus.

- D3 Cold (power state undefined) is the power-off state for the IP100A LF. The IP100A LF does not function in this state. When power is restored, the system guarantees the assertion of hardware reset, which puts the IP100A LF into the D0 Uninitialized state.

The IP100A LF can generate wake events to the system as a result of Wake Packet reception, Magic Packet reception, or due to a change in the link status. The WakeEvent register gives the host system control over which of these events are passed to the system. Wake events are signaled over the PCI bus using the PMEN pin.

A Wake Packet event is controlled by the WakePktEnable bit in WakeEvent register. WakePktEnable has no effect when IP100A LF is in the D0 power state, as the wake process can only take place in states D1, D2, or D3. When the IP100A LF detects a Wake Packet, it signals a wake event on PMEN (if PMEN assertion is enabled), and sets the WakePktEvent bit in the WakeEvent register. The IP100A LF can signal that a wake event has occurred when it receives a pre-defined frame from another station. The host system transfers a set of frame data patterns into the transmit FIFO using the transmit DMA function before placing the IP100A LF in a power-down state. Once powered down, the IP100A LF compares receive frames with the frame patterns in the transmit FIFO. When a matching frame is received (and also passes the filtering mode set in the ReceiveMode register), a wake event is signaled.

The frame patterns in the transmit FIFO specify which bytes in received frames are to be examined. Each byte in the transmit FIFO specifies a four bit relative offset (from the start of the received frame) in the most significant nibble and a four bit length indicator in the least significant nibble. Relative offsets describe the number of bytes of the received frame to skip from the last relevant byte, beginning with byte 0x00. Relative offsets with a value of 0xF indicate the actual relative offset is larger than 15, and is specified by the next 8 bit value in the transmit FIFO. Length indicators with a value of 0xF indicate the actual length indicator is larger than 15, and is specified by the next 8 bit value in the transmit FIFO. If both the relative offset, and the length indicator are 0xF, the first byte following the relative offset/length indicator pair is the actual relative offset, and the second following byte is the actual length indicator. A byte value of 0x00 indicates the end of the pattern for that wake frame. Immediately following the end-of-pattern is a 4-byte CRC. The calculation used to for the CRC is the same polynomial as the Ethernet MAC FCS.

An example pseudo-packet (based on the ARP packet example from Appendix A of the "OnNow Network Device Class Power Management Specification") which would be loaded into the transmit FIFO of the IP100A LF is shown in Figure 8.

| _                | TxFIFO |  |

|------------------|--------|--|

| Г                | 0xc2   |  |

|                  | 0x71   |  |

|                  | 0xf4   |  |

|                  | 0x10   |  |

| pseudo<br>packet | 0x00   |  |

|                  | 0xf3   |  |

|                  | 0x19   |  |

|                  | 0x08   |  |

|                  | 0xd7   |  |

| _                |        |  |

|                  |        |  |

FIGURE 8: Example Pseudo Packet

Using the pseudo packet in Figure 8, the IP100A LF will assert a wake event if a packet of the form shown in Figure 9 is received whereby a 32-bit CRC over the indicated bytes of the received packet yields the value 0xf31908d7.

| Received Packet | Byte Offset<br>Within Packet |

|-----------------|------------------------------|

|                 | 1                            |

| byte 12         | 0x0c                         |

| byte 13         | 0x0d                         |

|                 | 1                            |

| byte 21         | 0x15                         |

|                 | 1                            |

| byte 38         | 0x26                         |

| byte 39         | 0x27                         |

| byte 40         | 0x28                         |

| byte 41         | 0x29                         |

|                 | 1                            |

FIGURE 9: Example Wake Packet

The IP100A LF also supports Magic Packet<sup>™</sup> technology developed by Advanced Micro Devices to allow remote wake-up of a sleeping station on a network via transmission of a special frame. Once the IP100A LF has been placed in Magic Packet mode and put to sleep, it scans all incoming frames addressed to it for a data sequence consisting of 16 consecutive repetitions of its own 48-bit Ethernet MAC StationAddress. This sequence can be located anywhere within the frame, but must be preceded by a synchronization stream.

The synchronization stream is defined as 6 bytes of 0xFF. For example, if the MAC address programmed into the StationAddress register is 0x11:22:33:44:55:66, then the IP100A LF would be scanning for the frame data shown in Figure 10.

**Received Packet**

| 0xFFFFFFFFFFF  |

|----------------|

| 0x112233445566 |

| UX112233445566 |

### FIGURE 10: Example Magic Packet

Magic Packet wake up is controlled by the MagicPktEnable bit in the WakeEvent register. A wake event

can only take place in the D1, D2, or D3 states, and MagicPktEnable has no effect when the IP100A LF is in the D0 power state. The Magic Packet must also pass the address matching criteria set in ReceiveMode. A Magic Packet may also be a broadcast frame. When the IP100A LF detects a Magic Packet, it signals a wake event on PMEN (if PMEN assertion is enabled), and sets the MagicPktEvent bit in WakeEvent.

The IP100A LF can also signal a wake event when it senses a change in the network link state, either from LINK\_OK to LINK\_FAIL, or vice versa. Link state wake is controlled by the LinkEventEnable bit in the WakeEvent register. At the time LinkEventEnable is set by the host system, the IP100A LF samples the current link state. It then waits for the link state to change. If the link state changes before the IP100A LF returns to state D0 or LinkEventEnable is cleared, LinkEvent is set in WakeEvent, and (if it is enabled) the PMEN signal is asserted.

#### 10.1 Wake Event

When a desired wake event occurs, the IP100A LF sets the appropriate event bit in the WakeEvent register, sets the PmeStatus bit in the PowerMgmtCtrl register, and asserts the PMEN signal.

The host system responds to PMEN by scanning the power management configuration registers of all devices, looking for the device which asserted PMEN. If the device with the IP100A LF signaled wake, the system will find PmeStatus set in IP100A LF's PowerMgmtCtrl register. The operating system then clears the PmeEn bit in the PowerMgmtCtrl register causing PMEN to be de-asserted.

The operating system raises the power state (probably to D0) by writing to the PowerState bits in the PowerMgmtCtrl register. If the IP100A LF was previously in the D3 state, PCI configuration is lost and must be restored by the operating system.

The host system must set TxReset to clear any wake patterns out of the transmit FIFO (if this is not done, the patterns will be treated as frames and transmitted once the transmitter is enabled).