# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

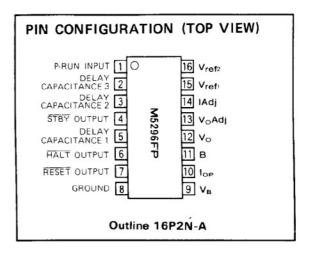

### M5296FP

## +5V CONSTANT-VOLTAGE POWER SUPPLY INCORPORATED WATCHDOG TIMER IC

#### DESCRIPTION

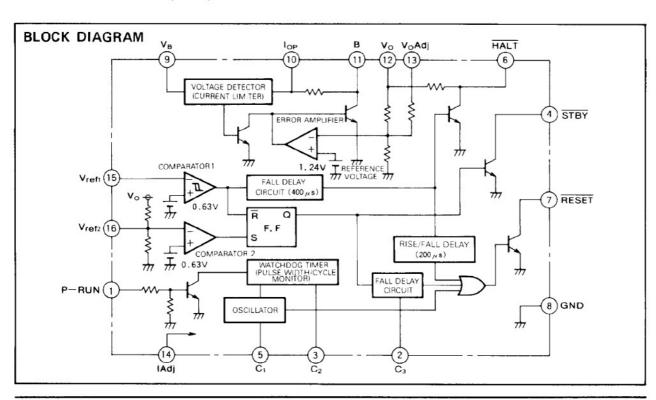

The M5296FP is a watchdog timer semiconductor integrated circuits which incorporates a 5V constant-voltage power supply.

To check for system failure and assure safe system operations, the M5296FP has three sequential outputs ( $\overline{HALT}$ ,  $\overline{STBY}$ , and  $\overline{RESET}$ ) and a watchdog timer output which intermittently generates a reset pulse when pulse width or cycle abnormalities are found in the clock signal from the microcomputer. (The watchdog output terminal is shared by the watchdog timer output and sequential output  $\overline{RESET}$ .)

Further, each output retains the Low reset feature at supply voltages down to 0.8V, thereby preventing system malfunctioning upon power ON.

#### **FEATURES**

- Watchdog timer (clock pulse width and cycle are monitored at the same time).

- Power ON reset timer.

- Three outputs (HALT output for holding, RESET output for reset, and STBY output for return).

- Wide supply voltage range . . . . . . . . . . . 6V-40V

- The delay time can be set using an external capacitor (the setting can be varied from about 1msec to 1sec).

- Built-in overcurrent protection circuit (which can be set up with an external resistor).

#### APPLICATION

Home and industrial microcomputer systems.

#### ABSOLUTE MAXIMUM RATINGS (Ta=25℃ unless otherwise noted)

| Symbol | Parameter                      | Test conditions | Rating          | Unit |  |  |

|--------|--------------------------------|-----------------|-----------------|------|--|--|

| VB     | Supply voltage                 |                 | 40              | V    |  |  |

| VHALT  | HALT output breakdown voltage  |                 | Vo              | ٧    |  |  |

| VSTBY  | STBY output breakdown voltage  |                 | 16              | V    |  |  |

| VRESET | RESET output breakdown voltage |                 | 16              | V    |  |  |

| HALT   | HALT output current            |                 | 10              | mA   |  |  |

| ISTBY  | STBY output current            |                 | 10              | mA   |  |  |

| IRESET | RESET output current           |                 | 10              | mA   |  |  |

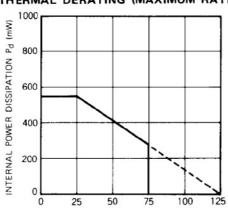

| Pd     | Internal power consumption     |                 | 550             | mW   |  |  |

| Kθ     | Thermal derating               | Ta ≥ 25 °C      | -5.5            | mW/℃ |  |  |

| Topr   | Operating ambient temperature  |                 | 20 + 75         | ℃    |  |  |

| Tstg   | Storage temperature            |                 | <b>−55~+125</b> | r    |  |  |

#### ELECTRICAL CHARACTERISTICS (VB = 12V, IO = 50mA, Ci = 22 \mu F, CO = 100 \mu F, Ta = 25 \tau unless otherwise noted)

| Symbol             | Parameter                                    | Test conditions                                |          | Rating |        |      | Unit |

|--------------------|----------------------------------------------|------------------------------------------------|----------|--------|--------|------|------|

|                    | Parameter                                    |                                                | Terminal | Min    | Тур    | Max  | Unit |

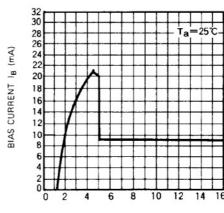

| l <sub>B</sub>     | Bias current                                 |                                                | 9        |        | 9      | 20   | mA   |

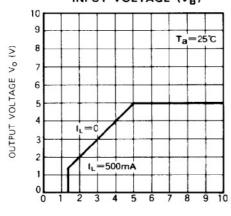

| Vo                 | 0                                            |                                                | 12       | 4.75   | 5.0    | 5.25 | ٧    |

| Vом                | Output voltage                               | V <sub>OAdj</sub> =0V, V <sub>B</sub> =6~40V   | 13       |        |        | 6.0  | ٧    |

| Reg-IN             | Input stability                              | V <sub>B</sub> =6~40V                          | 12       |        | 0.1    | 0.2  | %/V  |

| Reg-L              | Load stability                               | I <sub>O</sub> = 1 ~ 500mA                     | 12       |        | 40     | 200  | mV   |

| Vref1              | Reference voltage 1                          |                                                | 15       | 0.56   | 0.63   | 0.68 | V    |

| Vref2              | Reference voltage 2                          |                                                | 16       | 0.56   | 0.63   | 0.68 | ٧    |

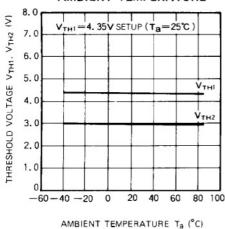

| △V <sub>TH1</sub>  | Threshold voltage hysteresis width           | *1 V <sub>TH1</sub> = 4.35V                    | 12       | 20     | 50     | 100  | mV   |

| V <sub>TH2</sub>   | Threshold voltage 2                          |                                                | 12       | 2.6    | 3.0    | 3.4  | V    |

| Vsath              | HALT output saturation voltage               | I <sub>HALT</sub> = 2mA                        | 6        |        | 0.2    | 0.4  | V    |

| Vsats              | STBY output saturation voltage               | I <sub>SIBY</sub> = 5mA                        | 4        |        | 0.2    | 0.4  | V    |

| Vsate              | RESET output saturation voltage              | IRESET = 5mA                                   | 1        |        | 0.2    | 0.4  | V    |

| VHALT              | HALT output H voltage                        |                                                | <b>6</b> | Vo-0.2 | Vo-0.1 | Vo   | V    |

| ILS                | STBY output leak current                     | V <sub>STBY</sub> = 5V                         | 4        |        |        | 1    | μΑ   |

| LH                 | RESET output leak current                    | V <sub>RESET</sub> = 5V                        | 1        |        |        | 1    | μΑ   |

| HALT               | HALT output source current *2                |                                                | 6        | 0.5    | 1.0    | 2.0  | mA   |

| I <sub>IN-P</sub>  | P-RUN input current                          | V <sub>IN-P</sub> = 5V                         | 1        | 130    | 200    | 300  | μА   |

| V <sub>IN-PH</sub> | P-RUN H input voltage                        |                                                | 1        | 2.0    |        |      | V    |

| VIN-PL             | P-RUN L input voltage                        |                                                | 1        |        |        | 0.3  | V    |

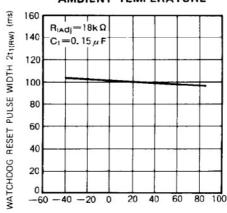

| t <sub>1(RW)</sub> | Watchdog reset pulse width                   | C <sub>1</sub> =0.15µF                         | 7        | 35     | 50     | 70   | ms   |

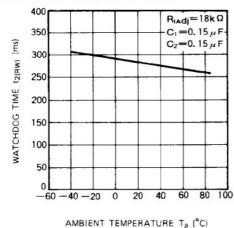

| t <sub>z(HW)</sub> | Watchdog time                                | C <sub>1</sub> =0.15µF, C <sub>2</sub> =0.15µF | 1        | 200    | 280    | 390  | ms   |

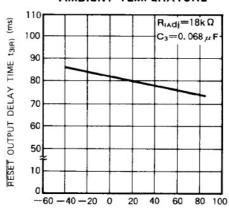

| t <sub>3(R)</sub>  | RESET output delay time                      | C <sub>3</sub> =0.068µF                        | 7        | 55     | 80     | 115  | ms   |

| t <sub>4(H)</sub>  | RESET output delay time                      |                                                | 1        | 110    | 200    | 340  | μs   |

| t <sub>5(H)</sub>  | HALT output delay time *3                    |                                                | 6        | 230    | 400    | 680  | μS   |

| t <sub>6(PW)</sub> | P-RUN input minimum pulse width              |                                                | 1        | 230    | 400    | 680  | μs   |

| VBMIN              | V <sub>B</sub> minimum operating voltage # 4 |                                                | 9)       |        |        | 2.0  | V    |

| VOMIN              | Vo minimum operating voltage #5              |                                                | 13       |        | 0.8    | 1.0  | V    |

| VIP                | Current limiter detection voltage +6         |                                                | 9 10     | 85     | 130    | 200  | mV   |

Note \*1:  $V_{TH1}$  is the threshold voltage for  $V_{TH1} > V_{TH2}$ . It is to be set up by an external resistor. The setup must be such that  $V_{TH1} > V_{TH2}$ .

\*2: A current that source when the HALT terminal is grounded in the HIGH HALT output mode (when Vo is normal).

\*3: When Ta = -20 to +75°C,  $t_5(H) > t_{4(H)}$ .

★4: The V<sub>B</sub> minimum operating voltage at which each function works

+5: The V<sub>O</sub> minimum operating voltage at which the HALT output, RESET output, and STBY output stay Low.

+6: In the overcurrent operation state, the current limiter works when the external resistor (Rs) voltage (voltage developed between terminals (9) and (9)) drops 130 mV (TYP) or more.

Output peak current  $I_{OP} = \frac{O.13}{Rs}$  [A]

#### **DEFINITION OF TERMS**

t<sub>1(RW)</sub>: Watchdog reset pulse width.

The width of an about 50% duty intermittent pulse that is generated from the RESET terminal when the clock signal input to the P-RUN terminal has a low input level, an insufficient pulse width, an excessively long period, or other problem.

Cycle t= 2 • t1(RW)

t<sub>2(RW)</sub>: Watchdog time.

The time for clock signal monitoring or the maximum clock cycle during which clock signal normality is detected

t<sub>3(R)</sub> : RESET output delay time.

The delay time from the instant the STBY output is remove to the moment the RESET output is remove.

t<sub>4(R)</sub> : RESET output delay time.

The time interval between  $\overline{HALT}$  output fall/rise and  $\overline{RESET}$  output fall/rise in cases where the  $\overline{STBY}$  output is not generated (when  $V_O$  does not drop below  $V_{TH2}$ ).

t<sub>5(H)</sub> : HALT output delay time.

The time interval between the instant  $V_0$  is restored to the  $V_{TH1} \pm \Delta V_{TH1}$  level and the instant the HALT output is remove.

t<sub>6 (PW)</sub>: P-RUN input minimum pulse width.

The minimum pulse width for clock signal normality detection.

V<sub>IN-PH</sub>: P-RUN H input voltage.

The minimum input voltage for P-RUN terminal input clock signal High level detection.

V<sub>IN-PL</sub>: The maximum input voltage for P-RUN terminal input clock signal Low level detection.

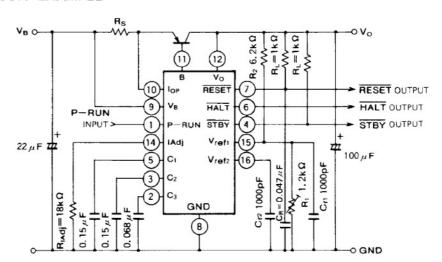

#### APPLICATION CIRCUIT EXAMPLE

- C<sub>1</sub>, C<sub>0</sub> ···· Necessary for oscillation prevention and input/ output stabilization. Be sure that these devices are used near the IC pins.

- $R_{IAdj}$  ····· Resistor for delay time  $\{t_{1(RW)} \text{ to } t_{6(PW)}\}$  setup constant current determination. A standard setting of  $18k\Omega$  should be employed.

- R<sub>1</sub>, R<sub>2</sub>····Resistor for threshold voltage V<sub>TH1</sub> setup. For the setup procedure, see the later section entitled "PERIPHERAL CIRCUIT CONSTANT SETUP AND USAGE PRECAUTIONS."

- C<sub>1</sub> ······ Necessary for watchdog reset pulse width setup.

- If the watchdog timer function is not to be used, ground terminal ⑤.

- $C_2$  ....... Required for watchdog time setup. If the watchdog timer function is not to be used, ground terminal

- C<sub>3</sub> ......Required for reset delay time setup for STBY output generation (V<sub>TH2</sub> detection). When terminal ② is open, the delay time for STBY output is equal to that for HALT output.

$t_{3(R)} = t_{4(R)}$

- $R_L \cdot \cdots \cdot As | STBY$  and RESET are open-collector outputs, load resistor  $R_L$  is needed.

- Cr<sub>1</sub>, Cr<sub>2</sub>. Used when voltage detection terminals (§) and (§) are unstable due to power line noise or other factor.

These devices are not needed when no such problems exist.

CR.....Necessary for  $\overline{RESET}$  output chattering prevention. The setup must be such that  $C_R \cdot R_L \ge 4.0 \times 10^{-5}$  (F· $\Omega$ ).

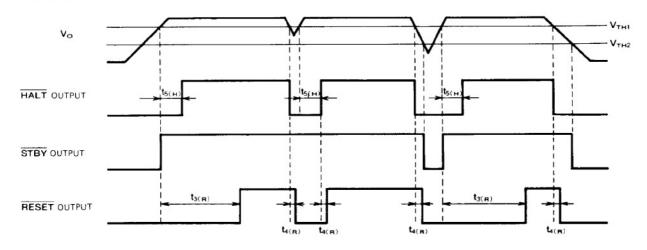

#### TIMING DIAGRAMS

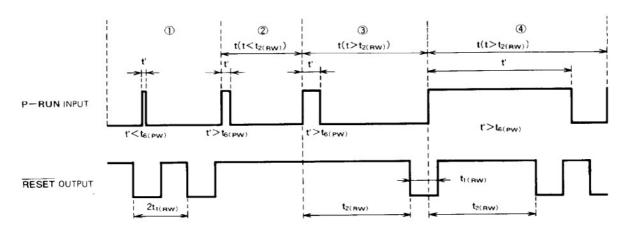

#### 1. Watchdog Timer

When the clock signal input is not give to the P-RUN input terminal or the entered signal has pulse widths (less than  $t_{6\,(PW)}$ ) that are not to be detected as the clock signal, intermittent pulses (pulse width  $t_{1\,(RW)}$  having a duty ratio of about 50% are outputted from the RESET terminal. When the entered clock signal has a pulse width of  $t_{6\,(PW)}$  or more, the RESET intermittent operation stops and the signal goes High so that the watchdog timer (time setting:  $t_{2\,(RW)}$  actuates. If no clock signal having a pulse width of  $t_{6\,(PW)}$  or more is entered for a time period of  $t_{2\,(RW)}$  after clock signal input, the RESET output starts an intermittent operation.

- (1) The clock signal input is give to the P-RUN input terminal. However, as the pulse width is smaller than t<sub>6 (PW)</sub>, the clock signal input is not detected as a signal so that RESET generates intermittent pulsing.

- (2) As the signal input has a pulse width of  $t_{6 \, (PW)}$  or more, the RESET intermittent operation stops and the High output is generated. Further, as the clock signal cycle is not longer than the watchdog time  $t_{2 \, (RW)}$ , RESET keeps its High output.

- (3) RESET maintains its High output by performing the same operations as indicated in paragraph (2) above.

- However, as the clock signal cycle is rendered longer than the watchdog time  $t_{2\,(RW)}$ ,  $\overline{RESET}$  starts an intermittent operation.

- (4) The RESET intermittent operation starts t<sub>2</sub> (RW) after clock signal input due to the same operations as indicated in paragraph (3) above. Even if the clock signal input is fed while the RESET level is Low with intermittent operations performed, RESET does not immediately go High so that the Low pulse width (t<sub>1</sub> (RW) is assured.

#### **VOLTAGE MONITORING TIMING DIAGRAM (P-RUN INPUT NORMALITY)**

# 2. Voltage Monitoring Timing Diagram (P-RUN Input Normality)

HALT output

When  $V_O$  drops below the threshold voltage VTH<sub>1</sub>,  $\overline{HALT}$  generates a Low level.  $\overline{HALT}$  is reset t<sub>5 (H)</sub> after  $V_O$  is restored to the VTH<sub>1</sub>  $\pm \Delta$ VTH<sub>1</sub> level.

STBY output

When  $V_0$  drops below the threshold voltage VTH<sub>2</sub> (VTH<sub>2</sub> < VTH<sub>1</sub>),  $\overline{STBY}$  generates a Low level. When  $V_0$  is restored to the VTH<sub>1</sub> level,  $\overline{STBY}$  is reset.

**RESET** output

When the decreased  $V_O$  level is between  $VTH_2$  and  $VTH_1$  ( $VTH_2 < V_O < VTH_1$ ),  $\overline{RESET}$  output generation takes place  $t_{4\,(R)}$  after  $\overline{HALT}$  fall/rise. When  $V_O$  is lower than  $VTH_2$ ,  $\overline{RESET}$  rise occurs  $t_3\,(R)$  after  $\overline{STBY}$  rise.

However,  $t_{3(H)} > t_{5(H)}$ .

#### PERIPHERAL CIRCUIT CONSTANT SETUP AND USAGE PRECAUTIONS

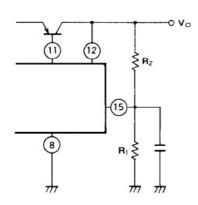

#### 1. Threshold Voltage Setup

As indicated in the timing diagram on the preceding page, the M5296FP checks for output voltage decrease on the basis of two preset values (threshold voltages 1 and 2 [ $V_{TH1}$  and  $V_{TH2}$ ]).  $V_{TH1}$  can be set as desired with an external resistor (however,  $V_{TH1} > V_{TH2}$ ).  $V_{TH2}$  is set to 3.0V Typ by the built-in resistor; however, it is possible to raise it slightly using the  $V_{ref2}$  terminal.

In the above circuit, V<sub>TH1</sub> is calculated as follows.

$$V_{TH1} = 0.63 \times \frac{R_1 + R_2}{R_1}$$

(V)

For V<sub>TH1</sub> detection purposes, hysteresis is provided to avoid operation instability which may be caused by noise ripple or other factor, and its value is as indicated below.

$$\Delta V_{TH1} = 7 \times \frac{R_1 + R_2}{R_1} \quad (mV)$$

NOTE 1: V<sub>TH1</sub> must be set up so that V<sub>TH1</sub> > V<sub>TH2</sub>.

NOTE 2: If malfunctioning occurs due to noise or other problem, connect an about 1000pF capacitor between terminals (§) and GND to assure stable operations.

#### 2. Delay Time Setup

The M5296FP uses an external capacitor to set up three different delay times (watchdog reset pulse width  $t_{1(RW)}$ , watchdog time  $t_{2(RW)}$ , and  $\overline{RESET}$  output delay time  $t_{3(R)}$ ).

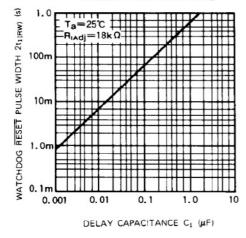

#### (1) t<sub>1 (RW)</sub> Setup

When the clock signal input to the P-RUN terminal is abnormal, intermittent pulsing having a duty ratio of about 50% is generated from the RESET terminal.

The oscillation cycle  $2\mbox{-t}_{1\{RW\}}$  is to be set up using  $C_1$  as indicated below.

$2 \cdot t_{1(RW)} = 6.72 \times 10^5 \times C_1$  (s)

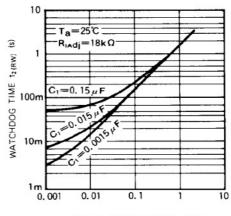

#### (2) t<sub>2(RW)</sub> Setup

The watchdog time  $t_{2(RW)}$  is used for clock signal monitoring purposes. It denotes the clock signal cycle limit. If the clock signal cycle becomes longer than  $t_{2(RW)}$ , intermittent pulses preset by  $C_1$  are generated from the RESET terminal. The value  $t_{2(RW)}$  is to be set up by  $C_2$ .

$t_{2(RW)} = t_{1(RW)} + 1.53 \times 10^6 \times C_2$  (s)

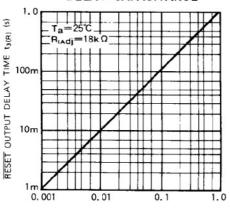

#### (3) t<sub>3(R)</sub> Setup

The RESET output delay time  $t_{3(R)}$  refers to the elapsed time from the instant the  $\overline{STBY}$  output is reset to the moment  $\overline{RESET}$  output is reset. It is to be set up by  $C_3$ .

$$t_{3(R)} = 1.18 \times 10^6 \times C_3$$

(s)

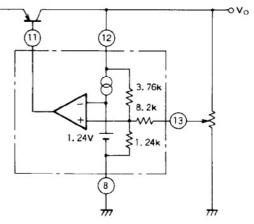

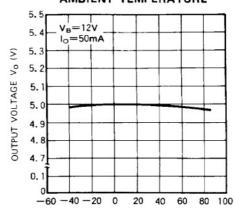

#### 3. Output Voltage Vo Adjustment

As shown above, the  $V_{OAdj}$  terminal permits output voltage fine adjustment. However, as a  $8.2k\Omega$  resistor is series-connected to the  $V_{OAdj}$  terminal, the approximate adjustment range is from -20% to +10%.

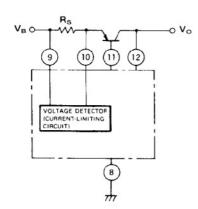

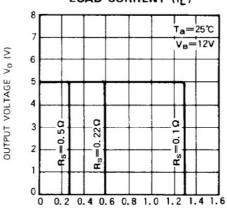

# 4. Overcurrent Protection Setup (Io Peak Current Setup)

In the circuit shown at left, the load current flowing through the detection resistor  $R_{\text{S}}$  is detected as a voltage value (detection voltage: 130mV) for current limiting purposes.

$$I_{OP} = \frac{130 \, (\text{mV})}{R_s \, (\Omega)} \, (\text{mA})$$

NOTE 3: The current flowing through  $R_s$  contains the IC bias current  $I_B$ . Therefore, the setup must be such that  $I_B < 130/R_s$  (mA).

#### TYPICAL CHARACTERISTICS

THERMAL DERATING (MAXIMUM RATING)

AMBIENT TEMPERATURE Ta (°C)

**BIAS CURRENT VS. INPUT VOLTAGE**

INPUT VOLTAGE VB (V)

OUTPUT VOLTAGE (Vo) VS.

INPUT VOLTAGE (VB)

INPUT VOLTAGE VB (V)

OUTPUT VOLTAGE (Vo) VS. LOAD CURRENT (IL)

LOAD CURRENT IL (A)

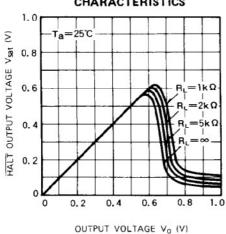

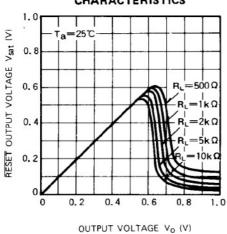

#### CRITICAL OPERATION VOLTAGE CHARACTERISTICS

# CRITICAL OPERATION VOLTAGE CHARACTERISTICS

OUTPUT VOLTAGE Vo (V)

#### CRITICAL OPERATION VOLTAGE CHARACTERISTICS

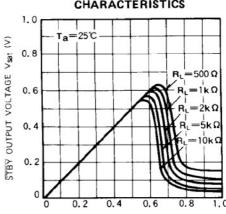

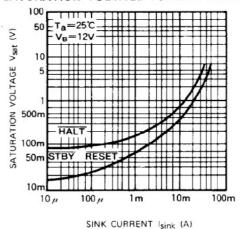

SATURATION VOLTAGE VS. SINK CURRENT

# WATCHDOG RESET PULSE WIDTH VS. DELAY CAPACITANCE

#### WATCHDOG TIME VS. DELAY CAPACITANCE

DELAY CAPACITANCE C2 (µF)

### RESET OUTPUT DELAY TIME VS. DELAY CAPACITANCE

DELAY CAPACITANCE C3 (#F)

# OUTPUT VOLTAGE VS. AMBIENT TEMPERATURE

AMBIENT TEMPERATURE Ta (°C)

# THRESHOLD VOLTAGE VS. AMBIENT TEMPERATURE

# WATCHDOG RESET PULSE WIDTH VS. AMBIENT TEMPERATURE

AMBIENT TEMPERATURE Ta (°C)

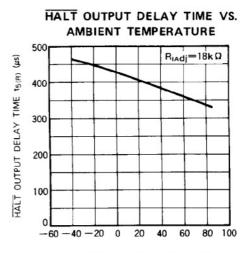

#### WATCHDOG TIME VS. AMBIENT TEMPERATURE

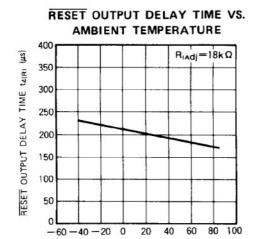

## RESET OUTPUT DELAY TIME VS. AMBIENT TEMPERATURE

AMBIENT TEMPERATURE Ta (°C)

AMBIENT TEMPERATURE Ta (°C)

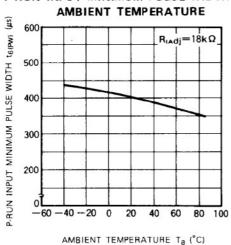

#### P-RUN INPUT MINIMUM PULSE WIDTH VS.

AMBIENT TEMPERATURE Ta (°C)

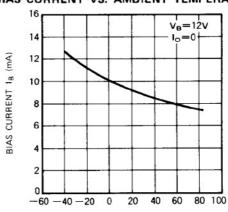

#### BIAS CURRENT VS. AMBIENT TEMPERATURE

AMBIENT TEMPERATURE Ta (°C)