# MX28F1000C

### 1M-BIT (128K x 8) CMOS FLASH MEMORY

#### **FEATURES**

- 131,072 bytes by 8-bit organization

- Fast access time: 90/120/150 ns

- · Low power consumption

- 50mA maximum active current

- 100μA maximum standby current

- Programming and erasing voltage 12V ± 5%

- · Command register architecture

- Byte Programming (15µs typical)

- Auto chip erase 5 seconds typical (including preprogramming time)

- · Auto Chip Erase and Auto Program

- DATA polling

- Toggle bit

- 10,000/1,000 minimum erase/program cycles

- Latch-up protected to 100mA from -1 to VCC+1V

- · Advanced CMOS Flash memory technology

- Compatible with JEDEC-standard byte-wide 32-pin EPROM pinouts

- · Package type:

- 32-pin plastic DIP

- 32-pin PLCC

- 32-pin TSOP (Type 1)

## **GENERAL DESCRIPTION**

The MX28F1000C is a 1-mega bit Flash memory organized as 128K bytes of 8 bits each. MXIC's Flash memories offer the most cost-effective and reliable read/write non-volatile random access memory. The MX28F1000P is packaged in 32-pin PDIP, PLCC and TSOP. It is designed to be reprogrammed and erased in-system or in-standard EPROM programmers.

The standard MX28F1000C offers access times as fast as 90 ns, allowing operation of high-speed microprocessors without wait states. To eliminate bus contention, the MX28F1000C has separate chip enable  $(\overline{CE})$  and output enable  $(\overline{OE})$  controls.

MXIC's Flash memories augment EPROM functionality with in-circuit electrical erasure and programming. The MX28F1000C uses a command register to manage this functionality, while maintaining a standard 32-pin pinout. The command register allows for 100% TTL level control inputs and fixed power supply levels during erase and programming, while maintaining maximum EPROM compatibility.

MXIC Flash technology reliably stores memory contents even after 10,000/1,000 erase and program cycles. The MXIC cell is designed to optimize the erase and programming mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and programming operations produces reliable cycling. The MX28F1000C uses a 12.0V  $\pm$  5% VPP supply to perform the Auto

Program/Erase algorithms.

The highest degree of latch-up protection is achieved with MXIC's proprietary non-epi process. Latch-up protection is proved for stresses up to 100 milliamps on address and data pin from -1V to VCC + 1V.

#### NOTICE:

MX28F1000C-XXC3(1,000 erase/program cycles) might exhibit an in-system failure rate of less than 1%.

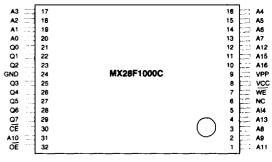

#### **PIN CONFIGURATIONS**

#### 32 PDIP

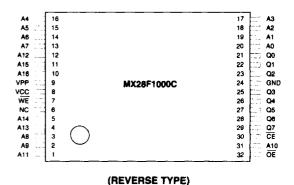

#### 32 PLCC

# TSOP (TYPE 1)

(NORMAL TYPE)

### PIN DESCRIPTION:

| SYMBOL | PIN NAME               |

|--------|------------------------|

| A0~A16 | Address Input          |

| Q0~Q7  | Data Input/Output      |

| CE     | Chip Enable Input      |

| ŌĒ     | Output Enable Input    |

| WE     | Write enable Pin       |

| VPP    | Program Supply Voltage |

| VCC    | Power Supply Pin (+5V) |

| GND    | Ground Pin             |