# Core10100 v4.0

Handbook

#### Actel Corporation, Mountain View, CA 94043

© 2009 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200077-6 Release: February 2009

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel and the Actel logo are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

## **Table of Contents**

|   | Introduction       5         Supported Device Families       7         Core Versions       7         Supported Interfaces       7         Device Utilization and Performance       7         Memory Requirements       10                                                                                                 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Functional Block Descriptions                                                                                                                                                                                                                                                                                             |

| 2 | Tool Flows15Licensing15Importing into Libero IDE17Simulation Flows18Synthesis in Libero IDE18Place-and-Route in Libero IDE18                                                                                                                                                                                              |

| 3 | Interface Descriptions19Parameters on Core1010019Parameters on Core10100_AHBAPB20AHB/APB Interface Signals26                                                                                                                                                                                                              |

| 4 | Software Interface27Register Maps27Frame Data and Descriptors47Internal Operation57                                                                                                                                                                                                                                       |

| 5 | Interface Timing         65           Core10100—CSR Interface         65           Core10100—Data Interface         65           Core10100_AHBAPB—APB Interface         65           Core10100_AHBAPB—AHB Interface         65           Core10100-RMII Interface         65           Clock and Reset Control         65 |

| 6 | Testbench Operation and Modification                                                                                                                                                                                                                                                                                      |

| 7 | System Operation                                                                                                                                                                                                                                                                                                          |

| A | User Testbench Support Routines                                                                                                                                                                                                                                                                                           |

*v4.0* 3

#### Table of Contents Core10100 v4.0

|   | VHDL Support                                    |                          |

|---|-------------------------------------------------|--------------------------|

| В | Transmit and Receive Functional Timing Examples | 87                       |

| C | List of Document Changes                        | 97                       |

| D | Product Support                                 | 101<br>101<br>101<br>101 |

|   | Index 1                                         | 03                       |

## Introduction

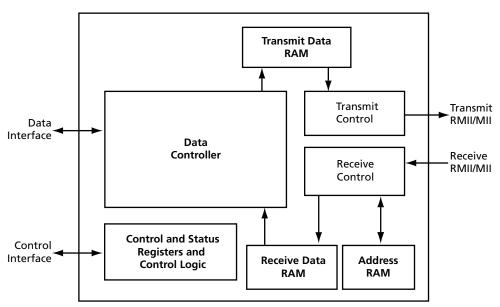

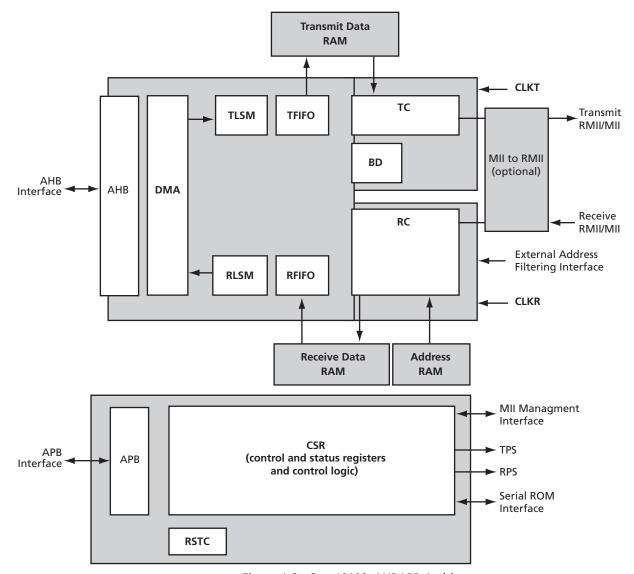

Core10100 is a high-speed media access control (MAC) Ethernet controller (Figure 1). It implements Carrier Sense Multiple Access with Collision Detection (CSMA/CD) algorithms defined by IEEE 802.3 for MAC over an Ethernet connection. Communication with an external host is implemented via a set of Control and Status registers and the DMA controller for external shared RAM. For data transfers, Core10100 operates as a DMA master. It automatically fetches from transmit data buffers and stores receive data buffers into external RAM with minimum CPU intervention. Linked list management enables the use of various memory allocation schemes. Internal RAMs are used as configurable FIFO memory blocks, and there are separate memory blocks for transmit and receive processes. The core has a generic host-side interface that connects with external CPUs. This host interface can be configured to work with 8-, 16-, or 32-bit data bus widths with big- or little-endian byte ordering.

Figure 1 · Core10100 Block Diagram

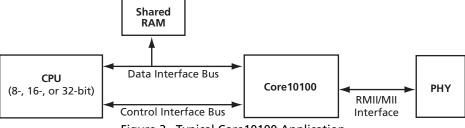

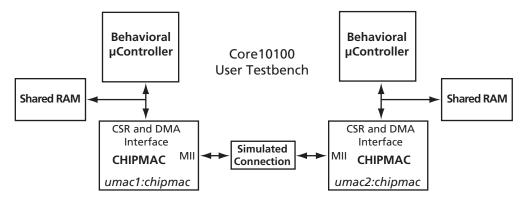

Figure 2 shows a typical application using Core10100. Typical applications include LAN controllers, AFDX controllers, and embedded systems. Figure 1-1 on page 11 shows the primary blocks of Core10100.

Figure 2 · Typical Core10100 Application

v4.0 5

Introduction Core10100 v4.0

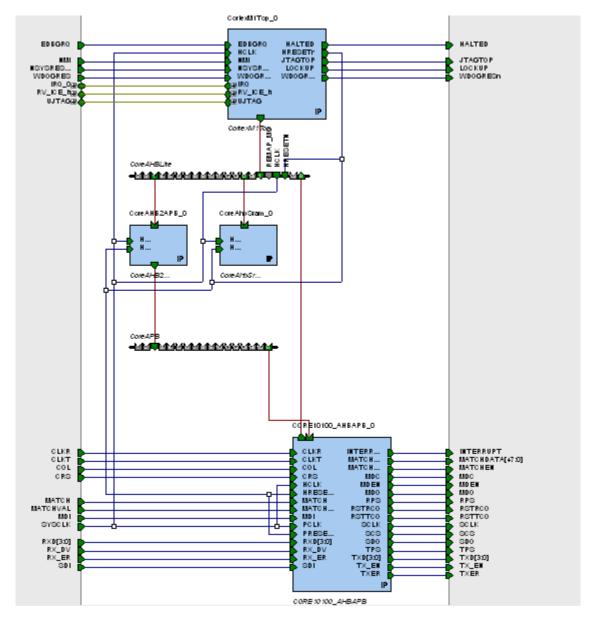

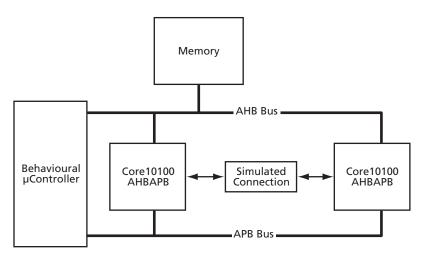

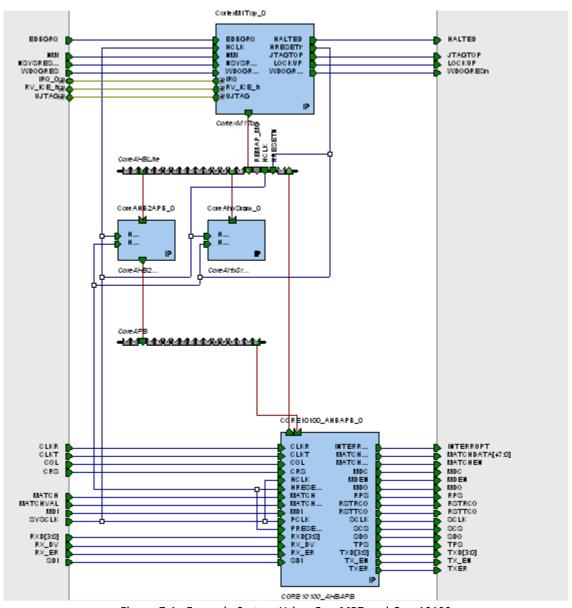

Figure 3 shows an ARM®-based system using Core10100\_AHBAPB. This system can be automatically created in SmartDesign.

Figure 3 · ARM-Based System Using Core10100\_AHBAPB

### **Supported Device Families**

IGLOO®

**IGLOOe**

ProASIC3

ProASIC3E

ProASIC®3L

Fusion

ProASICPLUS®

Axcelerator®

RTAX-S

#### **Core Versions**

This handbook applies to Core10100 and Core10100\_AHB v4.0. The release notes provided with the core list known discrepancies between this handbook and the core release associated with the release notes.

## **Supported Interfaces**

Core10100 is available with the following interfaces:

- Core10100—synchronous CPU and memory interfaces (legacy interface)

- Core10100\_AHBAPB—APB slave CPU interface and AHB master memory interface

Actel recommends that new designs using the SmartDesign environment use the Core10100\_AHBAPB version of the core. Core10100 is provided for backwards compliance to previous versions of Core10100.

The above interfaces are described in "Interface Descriptions" on page 19.

### **Device Utilization and Performance**

Core10100 can be implemented in the following Actel FPGA devices. Table 1 through Table 6 on page 9 provide the typical utilization and performance data for the core implemented in these devices.

Table 1 · Core10100 Device Utilization and Performance for an 8-Bit Datapath

| Family                              | Cel                      | ls or Tiles |       | RAM   | Utilization |       | Performance |

|-------------------------------------|--------------------------|-------------|-------|-------|-------------|-------|-------------|

| Tailing                             | Combinatorial Sequential |             | Total | ICINI | Device      | Total | (MHz)       |

| IGLOO®/e                            | 4,330                    | 1,918       | 6,248 | 14    | AGLE600     | 45%   | 30          |

| ProASIC®3<br>ProASIC3E<br>ProASIC3L | 4,173                    | 1,923       | 6,096 | 14    | A3P6000     | 44%   | 49          |

| Fusion                              | 4,215                    | 1,918       | 6,133 | 14    | AFS600      | 44%   | 56          |

| ProASICPLUS®                        | 5,547                    | 1,958       | 7,505 | 29    | APA600      | 35%   | 27          |

| Axcelerator®                        | 3,087                    | 2,207       | 5,114 | 13    | AX1000      | 28%   | 73          |

| RTAX-S                              | 3,055                    | 2,014       | 5,069 | 13    | RTAX1000S   | 28%   | 57          |

v4.0 7

Introduction Core10100 v4.0

Table 2 · Core10100 Device Utilization and Performance for a 16-Bit Datapath

| Family                             | Cel           | lls or Tiles |       | RAM     | Utilization |       | Performance |

|------------------------------------|---------------|--------------|-------|---------|-------------|-------|-------------|

| Taniny                             | Combinatorial | Sequential   | Total | IQ IIVI | Device      | Total | (MHz)       |

| IGLOO/e                            | 4,715         | 2,045        | 6,760 | 14      | AGLE600     | 49%   | 30          |

| ProASIC3<br>ProASIC3E<br>ProASIC3L | 4,529         | 2,050        | 6,579 | 14      | A3P600      | 49%   | 37          |

| Fusion                             | 4,693         | 2,043        | 6,736 | 14      | AFS600      | 49%   | 36          |

| ProASICPLUS                        | 6,163         | 2,087        | 8,250 | 29      | APA600      | 38%   | 26          |

| Axcelerator                        | 3,328         | 2,170        | 5,498 | 13      | AX1000      | 30%   | 67          |

| RTAX-S                             | 3,316         | 2,153        | 5,469 | 13      | RTAX1000S   | 30%   | 49          |

Table 3 · Core10100 Device Utilization and Performance for a 32-Bit Datapath

| Family                             | Cel                      | Cells or Tiles |       |     | Utilization |       | Performance |

|------------------------------------|--------------------------|----------------|-------|-----|-------------|-------|-------------|

| ranniy                             | Combinatorial Sequential |                | Total | RAM | Device      | Total | (MHz)       |

| IGLOO/e                            | 4,715                    | 1,963          | 6,678 | 14  | AGLE600     | 48%   | 30          |

| ProASIC3<br>ProASIC3E<br>ProASIC3L | 4,435                    | 1,967          | 6,402 | 14  | A3P600      | 46%   | 36          |

| Fusion                             | 4,597                    | 1,961          | 6,558 | 14  | AFS600      | 47%   | 36          |

| ProASIC <sup>PLUS</sup>            | 5,938                    | 1,997          | 7,935 | 29  | APA600      | 65%   | 26          |

| Axcelerator                        | 3,216                    | 2,090          | 5,306 | 13  | AX1000      | 29%   | 55          |

| RTAX-S                             | 3,225                    | 2,089          | 5,314 | 13  | RTAX1000S   | 29%   | 44          |

Table 4 · Core10100\_AHBAPB Device Utilization and Performance for an 8-Bit Datapath

| Family                             | Cel                     | lls or Tiles |       | RAM     | Utilization |       | Performance |

|------------------------------------|-------------------------|--------------|-------|---------|-------------|-------|-------------|

| 1 anny                             | Combinatorial Sequentia |              | Total | IC LIVI | Device      | Total | (MHz)       |

| IGLOO/e                            | 4,408                   | 1,936        | 6,344 | 14      | AGLE600     | 46%   | 30          |

| ProASIC3<br>ProASIC3E<br>ProASIC3L | 4,234                   | 1,941        | 6,175 | 14      | A3P600      | 45%   | 54          |

| Fusion                             | 4,306                   | 1,939        | 6,245 | 14      | AFS600      | 45%   | 54          |

| ProASIC <sup>PLUS</sup>            | 5,656                   | 1,975        | 7,660 | 29      | APA600      | 35%   | 32          |

| Axcelerator                        | 2,974                   | 2,049        | 5,023 | 13      | AX1000      | 28%   | 65          |

| RTAX-S                             | 2,946                   | 2,041        | 4,987 | 13      | RTAX1000S   | 27%   | 46          |

Table 5 · Core10100\_AHBAPB Device Utilization and Performance for a 16-Bit Datapath

| Family                             | Cel           | lls or Tiles |       | RAM     | Utilization |       | Performance |

|------------------------------------|---------------|--------------|-------|---------|-------------|-------|-------------|

| ranny                              | Combinatorial | Sequential   | Total | IV IIVI | Device      | Total | (MHz)       |

| IGLOO/e                            | 4,749         | 2,067        | 6,816 | 14      | AGLE600     | 49%   | 30          |

| ProASIC3<br>ProASIC3E<br>ProASIC3L | 4,579         | 2,065        | 6,644 | 14      | A3P600      | 48%   | 36          |

| Fusion                             | 4,620         | 2.065        | 6,685 | 14      | AFS600      | 48%   | 46          |

| ProASIC <sup>PLUS</sup>            | 6,219         | 2,106        | 8,354 | 29      | APA600      | 39%   | 25          |

| Axcelerator                        | 3,054         | 2,166        | 5,220 | 13      | AX1000      | 29%   | 65          |

| RTAX-S                             | 3,036         | 2,161        | 5,197 | 13      | RTAX1000S   | 28%   | 43          |

Table 6 · Core10100\_AHBAPB Device Utilization and Performance for a 32-Bit Datapath

| Family                             | Cel           | ls or Tiles |       | RAM   | Utilization |       | Performance |  |

|------------------------------------|---------------|-------------|-------|-------|-------------|-------|-------------|--|

| Taniny                             | Combinatorial | Sequential  | Total | ICHVI | Device      | Total | (MHz)       |  |

| IGLOO/e                            | 5,231         | 2,199       | 7,430 | 14    | AGLE600     | 54%   | 30          |  |

| ProASIC3<br>ProASIC3E<br>ProASIC3L | 5,011         | 2,197       | 7,208 | 14    | A3P600      | 53%   | 35          |  |

| Fusion                             | 5,169         | 2,195       | 7,364 | 14    | AFS600      | 53%   | 35          |  |

| ProASICPLUS                        | 6,625         | 2,243       | 8,897 | 29    | APA600      | 41%   | 25          |  |

| Axcelerator                        | 3,340         | 2,348       | 5,688 | 13    | AX1000      | 31%   | 56          |  |

| RTAX-S                             | 3,380         | 2,359       | 5,739 | 13    | RTAX1000S   | 32%   | 45          |  |

Note: Data in the above tables was achieved using Actel Libero® Integrated Design Environment (IDE), using the parameter settings given in Table 7 on page 10. Performance is for Std. speed grade parts, was achieved using the Core10100 macro alone, and represents the system clock (CLKDMA/HCLK) frequency. The CLKR and CLKT clock domains are capable of operating at 25 MHz or 2.5 MHz, depending on the link speed. The CLKCSR/PCLK clock domain is capable of operating in excess of CLKDMA/HCLK.

Introduction Core10100 v4.0

**Table 7 · Parameter Settings**

| Parameter               |       | Core1010 | 0      | Core10100_AHBAPB |        |        |  |

|-------------------------|-------|----------|--------|------------------|--------|--------|--|

| rarameter               | 8-Bit | 16-Bit   | 32-Bit | 8-Bit            | 16-Bit | 32-Bit |  |

| ENDIANESS               | 0     | 0        | 0      | 1                | 1      | 1      |  |

| ADDRFILTER              | 1     | 1        | 1      | 0                | 0      | 0      |  |

| FULLDUPLEX              | 0     | 0        | 0      | 0                | 0      | 0      |  |

| CSRWIDTH<br>APB_DWIDTH  | 8     | 16       | 32     | 8                | 16     | 32     |  |

| DATAWIDTH<br>AHB_DWIDTH | 8     | 16       | 32     | 8                | 16     | 32     |  |

| DATADEPTH<br>AHB_AWIDTH | 20    | 24       | 32     | 20               | 24     | 32     |  |

| TFIFODEPTH              | 11    | 10       | 9      | 11               | 10     | 9      |  |

| RFIFODEPTH              | 12    | 11       | 10     | 12               | 11     | 10     |  |

| TCDEPTH                 | 1     | 1        | 1      | 1                | 1      | 1      |  |

| RCDEPTH                 | 2     | 2        | 2      | 2                | 2      | 2      |  |

| RMII                    | 1     | 1        | 1      | 1                | 1      | 1      |  |

## **Memory Requirements**

Core10100 uses FPGA memory blocks. The actual number of memory blocks varies based on the parameter settings. The approximate number of RAM blocks is given by EQ 1 and EQ 2.

#### IGLOO/e, ProASIC3/E, ProASIC3L, Fusion, Axcelerator, and RTAX-S

NRAMS =  $(DW / 8 \times (2^{TFIFODEPTH} / 512 + 2^{RFIFODEPTH} / 512) + ADDRFILTER$

EQ 1

where DW is DATAWIDTH or AHB\_DWIDTH.

#### **ProASIC**PLUS

NRAMS =  $(DW / 8 \times (2^{TFIFODEPTH} / 256 + 2^{RFIFODEPTH} / 256) + 2 \times ADDRFILTER$

EQ 2

where DW is DATAWIDTH or AHB\_DWIDTH.

The number of RAM blocks may vary slightly from the above equations due to the Synthesis tool selecting different aspect ratios and inferring memories for internal logic.

# **Functional Block Descriptions**

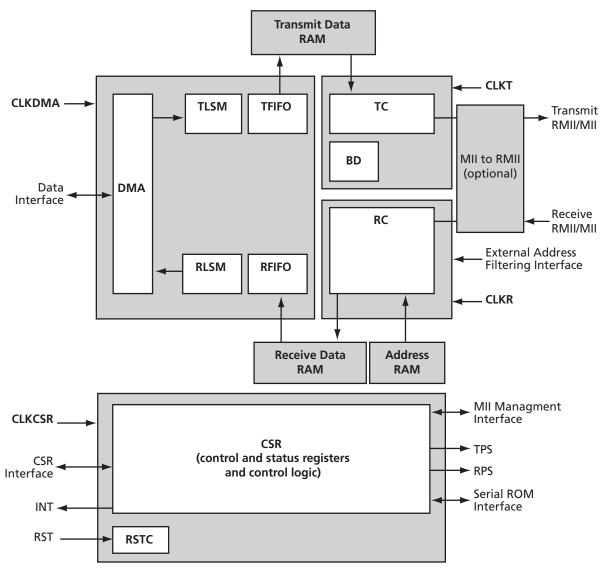

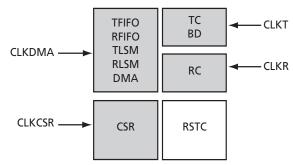

Core10100 architecture, shown in Figure 1-1, consists of the functional blocks described in this section.

Figure 1-1 · Core 10100 Architecture

Figure 1-2 · Core10100\_AHBAPB Architecture

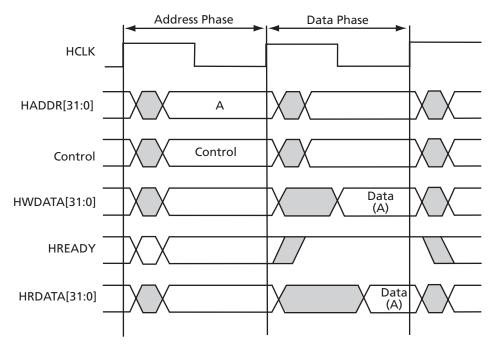

#### **AHB - AHB Interface**

The AHB block implements an AHB master function, allowing the DMA controller to access memory on the AHB bus.

#### **APB - APB Interface**

This APB block implements an APB slave interface, allowing the CPU to access the CSR registers set.

Core10100 v4.0

#### **CSR – Control/Status Register Logic**

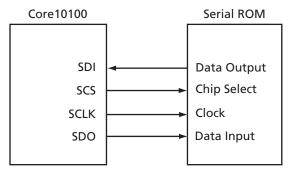

The CSR component is used to control Core10100 operation by the host. It implements the CSR register set and the interrupt controller. It also provides a generic host interface supporting 8-, 16-, and 32-bit transfer. The CSR component operates synchronously with the clkcsr clock from the host CSR interface. The CSR also provides a Serial ROM interface and MII Management interface. The host can access these two interfaces via read/write CSR registers.

#### **DMA - Direct Memory Access Controller**

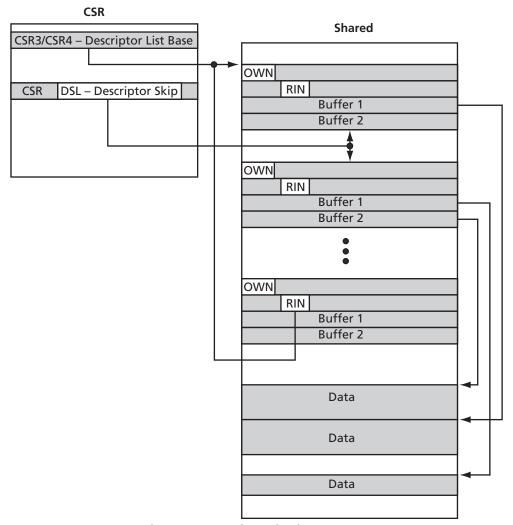

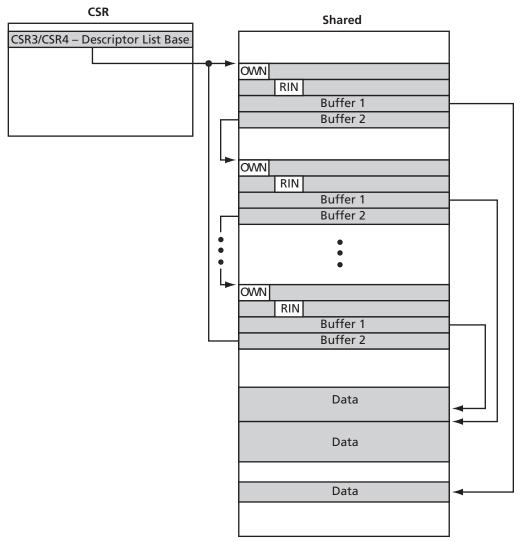

The direct memory access controller implements the host data interface. It services both the receive and transmit channels. The TLSM and TFIFO have access to one DMA channel. The RLSM and RFIFO have access to the other DMA channel. The direct memory access controller operates synchronously with the CLKDMA clock from the host data interface.

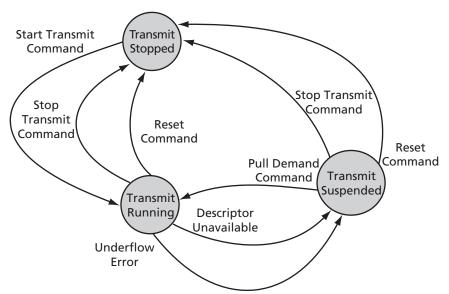

#### **TLSM – Transmit Linked List State Machine**

The transmit linked list state machine implements the descriptor/buffer architecture of Core10100. It manages the transmit descriptor list and fetches the data prepared for transmission from the data buffers into the transmit FIFO. The transmit linked list state machine controller operates synchronously with the CLKDMA clock from the host data interface.

#### **TFIFO - Transmit FIFO**

The transmit FIFO is used for buffering data prepared for transmission by Core10100. It provides an interface for the external transmit data RAM working as FIFO memory. It fetches the transmit data from the host via the DMA interface. The FIFO size can be configured via the core parameters. The transmit FIFO controller operates synchronously with the CLKDMA clock from the host data interface.

#### **TC - Transmit Controller**

The transmit controller implements the 802.3 transmit operation. From the network side, it uses the standard 802.3 MII interface for an external PHY device. The TC unit reads transmit data from the external transmit data RAM, formats the frame, and transmits the framed data via the MII. The transmit controller operates synchronously with the CLKT clock from the MII interface.

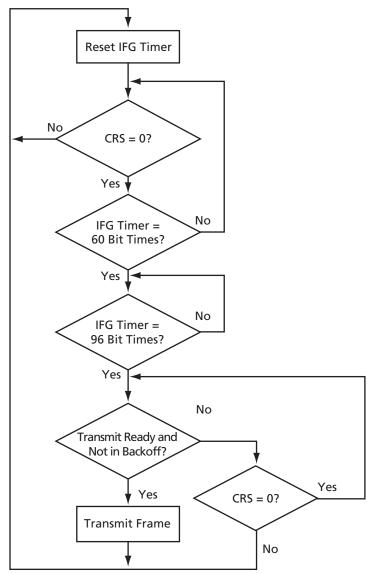

#### **BD - Backoff/Deferring**

The backoff/deferring controller implements the 802.3 half-duplex operation. It monitors the status of the Ethernet bus and decides whether to perform a transmit or backoff/deferring of the data via the MII. It operates synchronously with the CLKT clock from the MII interface.

#### **RLSM – Receive Linked List State Machine**

The receive linked list state machine implements the descriptor/buffer architecture of Core10100. It manages the receive descriptor list and moves the data from the receive FIFO into the data buffers. The receive linked list state machine controller operates synchronously with the clkdma clock from the host data interface.

#### **RFIFO - Receive FIFO**

The receive FIFO is used for buffering data received by Core10100. It provides an interface for the external RAM working as FIFO memory. The FIFO size can be configured by the generic parameters of the core. The receive FIFO controller operates synchronously with the CLKDMA clock from the host data interface.

Core10100 v4.0

#### **RC - Receive Controller**

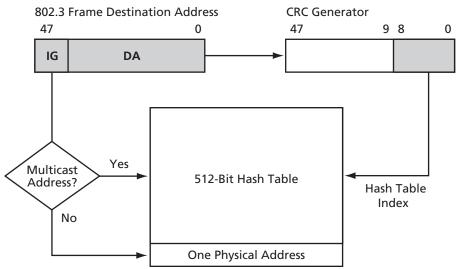

The receive controller implements the 802.3 receive operation. From the network side it uses the standard 802.3 MII interface for an external PHY device. The RC block transfers data received from the MII to the receive data RAM. It supports internal address filtering. It also supports an external address filtering interface. The receive controller operates synchronously with the CLKR clock from the MII interface.

#### **RSTC - Reset Controller**

The reset controller is used to reset all components of Core10100. It generates a reset signal asynchronous to all clock domains in the design from the external reset line and software reset.

#### **Memory Blocks**

There are three internal memory blocks required for the proper operation of Core10100:

- Receive data RAM Synchronous RAM working as receive FIFO

- Transmit data RAM Synchronous RAM working as transmit FIFO

- Address RAM Synchronous RAM working as MAC address memory

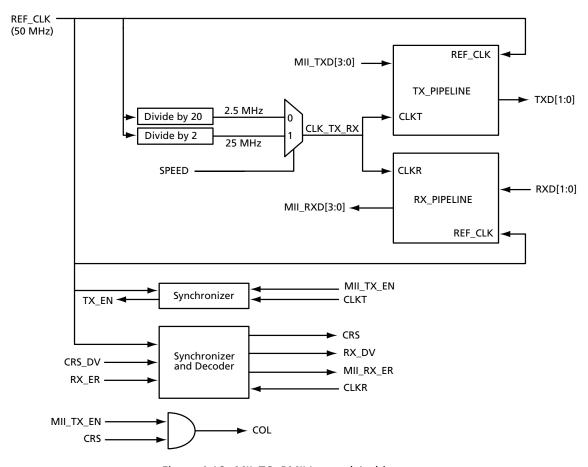

#### **RMII - RMII to MII Interface**

The Reduced Media Independent Interface (RMII) reduces the number of pins required for connecting to the PHY from 16 to 8.

## **Tool Flows**

## Licensing

Core10100 is licensed in two ways: Obfuscated and RTL. Depending on your license, tool flow functionality may be limited.

#### **Obfuscated**

Complete RTL code is provided for the core, enabling the core to be instantiated with SmartDesign. Simulation, Synthesis, and Layout can be performed with Actel Libero® Integrated Design Environment (IDE). The RTL code for the core is obfuscated, <sup>1</sup> and the some of the testbench source files are not provided. They are precompiled into the compiled simulation library instead.

#### **RTL**

Complete RTL source code is provided for the core and testbenches.

v4.0 15

<sup>1.</sup> Obfuscated means the RTL source files have had formatting and comments removed, and all instance and net names have been replaced with random character sequences.

Tool Flows Core10100 v4.0

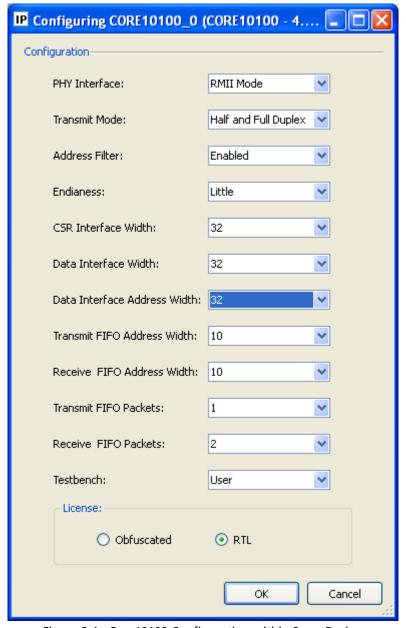

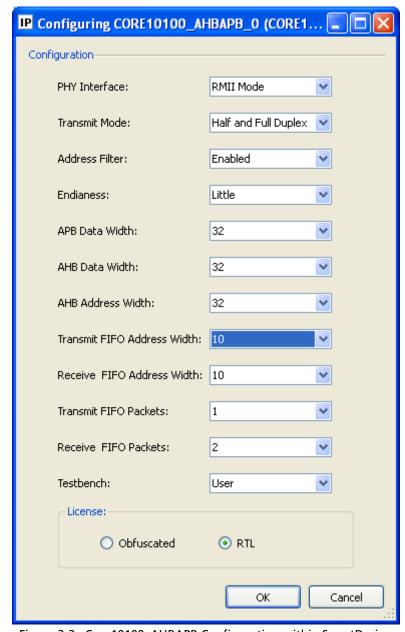

The core can be configured using the configuration GUI within SmartDesign, as shown in Figure 2-1 and Figure 2-2 on page 17.

Figure 2-1  $\cdot$  Core10100 Configuration within SmartDesign

Figure 2-2 · Core10100\_AHBAPB Configuration within SmartDesign

## Importing into Libero IDE

Core10100 v4.0

Core10100 is available for download to the SmartDesign IP Catalog, via the Libero IDE web repository. For information on using SmartDesign to instantiate, configure, connect, and generate cores, refer to the Libero IDE online help.

Tool Flows Core10100 v4.0

#### **Simulation Flows**

To run simulations, select the user testbench within the SmartDesign Core10100 configuration GUI, right-click, and select Generate Design (see Figure 2-1 on page 16).

When SmartDesign generates the design files, it will install the appropriate testbench files. To run the simulation, simply set the design root to the Core10100 instantiation in the Libero IDE design hierarchy pane and click the Simulation icon in the Libero IDE Design Flow window. This will invoke Model Sim and automatically run the simulation.

### Synthesis in Libero IDE

Set the design root appropriately and click the **Synthesis** icon in the Libero IDE. The synthesis window appears, displaying the Synplicity® project. Set Synplicity to use the Verilog 2001 standard if Verilog is being used. To perform synthesis, click the **Run** icon.

"Timing Constraints" on page 70 details the recommended timing constraints that should be used during Synthesis.

#### Place-and-Route in Libero IDE

Having set the design route appropriately and run Synthesis, click the **Layout** icon in Libero IDE to invoke Designer. Core10100 requires no special place-and-route settings.

"Timing Constraints" on page 70 details the recommended timing constraints that should be used during Layout.

# **Interface Descriptions**

Core10100 is available with the following interfaces:

- CSR Interface

- AMBA

Both Core10100 and Core10100\_AHBAPB share a common set of set signals to the backend physical layer (PHY) and address filtering interface.

### Parameters on Core10100

Table 3-1 details the parameters on Core10100.

Table 3-1 · Core10100 Parameters

| Parameter  | Values    | Default<br>Value | Description                                                                                                                           |

|------------|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|            |           |                  | Must be set to match the supported FPGA family:                                                                                       |

|            |           |                  | 11 – Axcelerator                                                                                                                      |

|            |           |                  | 12 – RTAX-S                                                                                                                           |

|            |           |                  | 14 – ProASIC <u>PLUS</u>                                                                                                              |

| D43 6777   |           |                  | 15 – ProASIC3                                                                                                                         |

| FAMILY     | 0 to 99   | 17               | 16 - ProASIC3E                                                                                                                        |

|            |           |                  | 17 – Fusion                                                                                                                           |

|            |           |                  | 20 – IGLOO                                                                                                                            |

|            |           |                  | 21 – IGLOOe                                                                                                                           |

|            |           |                  | 22 – ProASIC3L                                                                                                                        |

|            |           |                  | This controls the core's support of half-duplex operation.                                                                            |

|            | 0 to 1    | 0                | 0 – Half- and full-duplex operation supported                                                                                         |

| FULLDUPLEX |           |                  | 1 – Full-duplex only                                                                                                                  |

|            |           |                  | When set to '1', the collision and backoff logic required to support half-duplex operation is omitted, reducing the size of the core. |

|            |           |                  | Sets the endianess of the core:                                                                                                       |

|            |           |                  | 0 – Programmable by software                                                                                                          |

| ENDIANESS  | 0 to 2    | 1                | 1 – Little                                                                                                                            |

|            |           |                  | 2 – Big                                                                                                                               |

|            |           |                  | When set to a nonzero value, the size of the core is reduced.                                                                         |

|            |           |                  | Enables the internal address filter RAM.                                                                                              |

| ADDRFILTER | 0 to 1    | 1                | 0 – Internal address filter RAM disabled                                                                                              |

|            |           |                  | 1 – Internal address filter RAM enabled                                                                                               |

| DATADEPTH  | 20 to 32  | 32               | Sets the width of the address bus used to interface to the system memory.                                                             |

| DATAWIDTH  | 8, 16, 32 | 32               | Sets the width of the data bus used to interface to the system memory.                                                                |

Table 3-1 · Core10100 Parameters (continued)

| Parameter  | Values    | Default<br>Value | Description                                                                                                                                                                                                                          |  |

|------------|-----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CSRWIDTH   | 8, 16, 32 | 32               | Sets the width of the data bus used to access the registers within the core.                                                                                                                                                         |  |

| TCDEPTH    | 1 to 4    | 1                | Defines the maximum number of frames that can reside in the transmit FIFO at one time. The maximum number of frames that reside in the TX FIFO at one time is 2 <sup>TCDEPTH</sup> .                                                 |  |

| RCDEPTH    | 1 to 4    | 2                | Defines the maximum number of frames that can reside in the receive FIFO at one time. The maximum number of frames that reside in the RX FIFO at one time is 2 <sup>RCDEPTH</sup> -1.                                                |  |

| TFIFODEPTH | 7 to 12   | 9                | Sets the size of the internal FIFO used to buffer transmit data. The size is 2 <sup>TFIFODEPTH</sup> × AHB_DWIDTH / 8 bytes.  The transmit FIFO size must be greater than TCDEPTH times the maximum permitted frame size.            |  |

| RFIFODEPTH | 7 to 12   | 10               | Sets the size of the internal FIFO used to buffer receive data. The size is $2^{\text{RFIFODEPTH}} \times \text{AHB\_DWIDTH} / 8$ bytes.  The receive FIFO size must be greater than RCDEPTH times the maximum permitted frame size. |  |

| RMII       | 0, 1      | 0                | When set to 1, the core supports RMII interface. When set to 0, the core supports MII interface.                                                                                                                                     |  |

## Parameters on Core10100\_AHBAPB

Table 3-2 details the parameters on Core10100\_AHBAPB.

Table 3-2 · Core10100\_AHBAPB Parameters

| Parameter  | Values  | Default Value | Description                                                                                                                           |  |  |  |

|------------|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|            |         |               | Must be set to match the supported FPGA family.                                                                                       |  |  |  |

|            |         |               | 11 – Axcelerator                                                                                                                      |  |  |  |

|            |         |               | 12 – RTAX-S                                                                                                                           |  |  |  |

|            |         |               | 14 – ProASIC <sup>PLUS</sup>                                                                                                          |  |  |  |

| FAMILY     | 0 to 99 | 17            | 15 – ProASIC3                                                                                                                         |  |  |  |

|            |         |               | 16 – ProASIC3E                                                                                                                        |  |  |  |

|            |         |               | 17 – Fusion                                                                                                                           |  |  |  |

|            |         |               | 20 – IGLOO                                                                                                                            |  |  |  |

|            |         |               | 21 – IGLOOe                                                                                                                           |  |  |  |

|            |         |               | This controls the core's support of half-duplex operation.                                                                            |  |  |  |

|            |         |               | 0 – Half- and full-duplex operation supported                                                                                         |  |  |  |

| FULLDUPLEX | 0 to 1  | 0             | 1 – Full-duplex only                                                                                                                  |  |  |  |

|            | 1221    |               | When set to '1', the collision and backoff logic required to support half-duplex operation is omitted, reducing the size of the core. |  |  |  |

Table 3-2 · Core10100\_AHBAPB Parameters (continued)

| Parameter  | Values    | Default Value | Description                                                                                                                                                                                                                           |

|------------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |           |               | Sets the endianess of the core.                                                                                                                                                                                                       |

|            |           |               | 0 – Programmable by software                                                                                                                                                                                                          |

| ENDIANESS  | 0 to 2    | 1             | 1 – Little                                                                                                                                                                                                                            |

|            |           |               | 2 – Big                                                                                                                                                                                                                               |

|            |           |               | When set to nonzero, the size of the core is reduced.                                                                                                                                                                                 |

|            |           |               | Enables the internal address filter RAM.                                                                                                                                                                                              |

| ADDRFILTER | 0 to 1    | 1             | 0 – Internal address filter RAM disabled                                                                                                                                                                                              |

|            |           |               | 1 – Internal address filter RAM enabled                                                                                                                                                                                               |

| AHB_AWIDTH | 20 to 32  | 32            | Sets the width of the AHB address bus used to interface to the system memory.                                                                                                                                                         |

| AHB_DWIDTH | 8, 16, 32 | 32            | Sets the width of the AHB data bus used to interface to the system memory.                                                                                                                                                            |

| APB_DWIDTH | 8, 16, 32 | 32            | Sets the width of the APB data bus used to access the registers within the core.                                                                                                                                                      |

| TCDEPTH    | 1 to 4    | 1             | Defines the maximum number of frames that can reside in the transmit FIFO at one time. The maximum number of frames that reside in the TX FIFO at one time is 2 <sup>TCDEPTH</sup> .                                                  |

| RCDEPTH    | 1 to 4    | 2             | Defines the maximum number of frames that can reside in the receive FIFO at one time. The maximum number of frames that reside in the RX FIFO at one time is 2 <sup>RCDEPTH</sup> -1.                                                 |

| TFIFODEPTH | 7 to 12   | 9             | Sets the size of the internal FIFO used to buffer transmit data. The size is $2^{\text{TFIFODEPTH}} \times \text{AHB\_DWIDTH} / 8$ bytes. The transmit FIFO size must be greater than TCDEPTH times the maximum permitted frame size. |

| RFIFODEPTH | 7 to 12   | 10            | Sets the size of the internal FIFO used to buffer receive data. The size is $2^{RFIFODEPTH} \times AHB\_DWIDTH / 8$ bytes. The receive FIFO size must be greater than RCDEPTH times the maximum permitted frame size.                 |

| RMII       | 0, 1      | 0             | When set to 1, the core supports RMII interface. When set to 0, the core supports MII interface.                                                                                                                                      |

# **CSR Interface Signals**

Table 3-3 lists the signals included on the Core10100 core.

Table 3-3 · Core10100 Signals

| Name     | Type | Polarity   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          | 1    |            | Control and Status Register Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| CLKCSR   | In   | Rise       | CSR clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

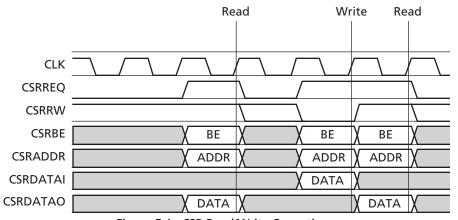

| CSRREQ   | In   | HIGH       | This signal is set by a host to request a data transfer on the CSR interface. It can be a read or a write request, depending on the value of the CSRRW signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| CSRRW    | In   | HIGH       | This signal indicates the type of request on the CSR interface. Setting CSRRW indicates a read operation, and clearing it indicates a write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| CSRBE    | In   | CSRWIDTH/8 | This signal is the data byte enable to indicate which byte lanes of CSRDATAI or CSRDATAO are the valid data bytes. Each bit of the CSRBE controls a single byte lane.  All CSRBE signal combinations are allowed.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| CSRDATAI | In   | CSRWIDTH   | The write data is provided by the system on the CSRDATAI inputs during the write request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| CSRADDR  | In   | 8          | The CSRADDR receives the address of an individual CSR data transaction.  The meaning of CSRADDR depends on the CSRWIDTH parameter.  For CSRWIDTH = 32 (32-bit interface), only the CSRADDR bits from 6 down to 2 are significant. The addresses are longword-aligned (32-bit) in this mode.  For CSRWIDTH = 16 (16-bit interface), the CSRADDR bits from 6 down to 1 are significant. The addresses are word-aligned (16-bit) in this mode.  For CSRWIDTH = 8 (8-bit interface), all bits of CSRADDR are significant. The addresses                                                                                                                                   |  |

| CSRACK   | Out  | HIGH       | are byte-aligned (8-bit) in this mode.  The CSRACK signal indicates either that valid data is present on the CSRDATAO outputs during a read request or that the CSRDATAI inputs have been sampled during a write request. The current version of Core10100 has the CSRACK signal statically tied to logic 1—Core10100 responds to reads and writes immediately.                                                                                                                                                                                                                                                                                                       |  |

| CSRDATAO | Out  | CSRWIDTH   | The CSRDATAO signal provides the read data in response to a read request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

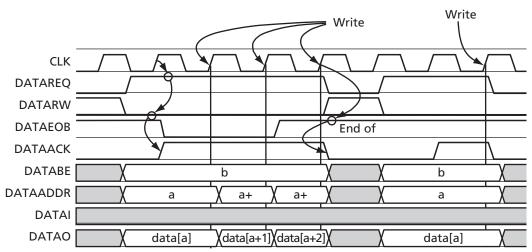

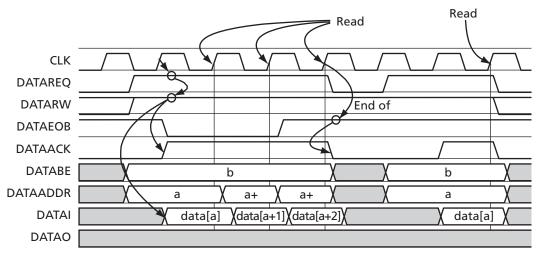

|          |      |            | Data Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| CLKDMA   | In   | Rise       | Data clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| DATAACK  | In   | HIGH       | The DATAACK input is an acknowledge signal supplied by the host in response to the MAC's request. In the case of a read operation, DATAACK indicates valid data is on the DATAI input. The DATAI input must be stable while DATAACK is set. In the case of a write operation, setting DATAACK indicates that the host is ready to fetch the data supplied by Core10100 on the DATAO output. Regardless of the current transaction type (write or read), a data transfer occurs on every rising edge of CLKDMA on which both DATAREQ and DATAACK are set. The DATAACK signal can be asserted or deasserted at any clock cycle, even in the middle of a burst transfer. |  |

| DATAI    | In   | DATAWIDTH  | The read data must be provided on the DATAI input by the system in response to a read request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

Table 3-3 · Core10100 Signals (continued)

| Name             | Type                  | Polarity                                                                                                                                                   | Description                                                                                                                                                                          |

|------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATAREQ          | Out                   | HIGH                                                                                                                                                       | This signal is set by Core10100 to put a request for the data transfer on the interface. While DATAREQ remains active, the DATARW signal is stable—there is no transition on DATARW. |

| DATARW           | Out                   | HIGH                                                                                                                                                       | The DATARW output indicates the type of request on the data interface. When set, it indicates a read operation; when cleared, it indicates a write operation.                        |

|                  |                       |                                                                                                                                                            | The DATAEOB output is an "end-of-burst" signal used for burst transactions.                                                                                                          |

| DATAEOB Out HIGH |                       | HIGH                                                                                                                                                       | When set, it indicates the last data transfer for a current burst; when cleared, it indicates that there will be more data transfers.                                                |

| DATAO            | Out                   | DATAWIDTH                                                                                                                                                  | Data to be written is provided by Core10100 on DATAO during a write request.                                                                                                         |

|                  |                       |                                                                                                                                                            | This signal addresses the external memory space for a data transaction. The meaning of the DATAADDR bits depends on the DATAWIDTH parameter.                                         |

| DATAADDR         | ATAADDR Out DATADEPTI | DATADEPTH                                                                                                                                                  | For DATAWIDTH = 32 (32-bit interface), only DATAADDR bits DATADEPTH-1 down to 2 are significant. The addresses are longword-aligned (32-bit) in this mode.                           |

|                  |                       | For DATAWIDTH = 16 (16-bit interface), the DATAADDR bits from DATADEPTH-1 down to 1 are significant. The addresses are word-aligned (16-bit) in this mode. |                                                                                                                                                                                      |

|                  |                       |                                                                                                                                                            | For DATAWIDTH = 8 (8-bit interface), all bits of DATAADDR are significant. The addresses are byte-aligned (8-bit) in this mode.                                                      |

## **Common Interface Signals**

The following signals are included on both the Core10100 and Core10100\_AHBAPB cores.

Table 3-4  $\cdot$  Signals Included in Core10100 and Core10100\_AHBAPB

| Name        | Туре                          | Polarity /<br>Bus Size | Description                                                                                                                                                                                                                                                                                 |  |  |

|-------------|-------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             | General Host Interface Signal |                        |                                                                                                                                                                                                                                                                                             |  |  |

| RSTCSR      | In                            | HIGH                   | Host-side reset                                                                                                                                                                                                                                                                             |  |  |

| INT         | Out                           | HIGH                   | Interrupt                                                                                                                                                                                                                                                                                   |  |  |

| RSTTCO      | Out                           | HIGH                   | Transmit side reset                                                                                                                                                                                                                                                                         |  |  |

| RSTRCO      | Out                           | HIGH                   | Receive side reset                                                                                                                                                                                                                                                                          |  |  |

| TPS         | Out                           | HIGH                   | Transmit process stopped                                                                                                                                                                                                                                                                    |  |  |

| RPS         | Out                           | HIGH                   | Receive process stopped                                                                                                                                                                                                                                                                     |  |  |

|             |                               |                        | Serial ROM Interface                                                                                                                                                                                                                                                                        |  |  |

| SDI         | In                            | 1                      | Serial data                                                                                                                                                                                                                                                                                 |  |  |

| SCS         | Out                           | 1                      | Serial chip select                                                                                                                                                                                                                                                                          |  |  |

| SCLK        | Out                           | 1                      | Serial clock output                                                                                                                                                                                                                                                                         |  |  |

| SDO         | Out                           | 1                      | Serial data output                                                                                                                                                                                                                                                                          |  |  |

|             |                               |                        | External Address Filtering Interface                                                                                                                                                                                                                                                        |  |  |

|             |                               |                        | External address match                                                                                                                                                                                                                                                                      |  |  |

| МАТСН       | In                            | HIGH                   | When HIGH, indicates that the destination address on the MATCHDATA port is recognized by the external address-checking logic and that the current frame must be received by Core10100.                                                                                                      |  |  |

|             |                               |                        | When LOW, indicates that the destination address on the MATCHDATA port is not recognized and that the current frame should be discarded.                                                                                                                                                    |  |  |

|             |                               |                        | Note that the match signal should be valid only when the MATCHVAL signal is HIGH.                                                                                                                                                                                                           |  |  |

| MATCHVAL In |                               | HIGH                   | External address match valid                                                                                                                                                                                                                                                                |  |  |

|             |                               |                        | When HIGH, indicates that the MATCH signal is valid.                                                                                                                                                                                                                                        |  |  |

| MATCHEN     | Out                           | HIGH                   | External match enable  When HIGH, indicates that the MATCHDATA signal is valid. The MATCHEN output should be used as an enable signal for the external address-checking logic. It is HIGH for at least four CLKR clock periods to allow for the latency of external address-checking logic. |  |  |

| MATCHDATA   | Out                           | 48                     | External address match data  The MATCHDATA signal represents the 48-bit destination address of the received frame.  Note that the MATCHDATA signal is valid only when the MATCHEN signal is HIGH.                                                                                           |  |  |

|             |                               |                        | RMII/MII PHY Interface                                                                                                                                                                                                                                                                      |  |  |

| CLKT        | In                            | Rise                   | Clock for transmit operation This must be a 25 MHz clock for a 100 Mbps operation or a 2.5 MHz clock for a 10 Mbps operation. This input is only used in MII mode. In RMII mode, this input will be grounded by SmartDesign.                                                                |  |  |

Table 3-4 · Signals Included in Core10100 and Core10100\_AHBAPB (continued)

| Name  | Туре | Polarity /<br>Bus Size | Description                                                                                                                                                                                                           |  |

|-------|------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       |      |                        | Clock for receive operation                                                                                                                                                                                           |  |

| CLKR  | In   | Rise                   | This must be a 25 MHz clock for a 100 Mbps operation or a 2.5 MHz clock for a 10 Mbps operation. This input is only used in MII mode. In RMII mode, this input will be grounded by SmartDesign.                       |  |

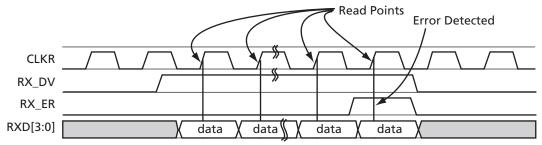

|       |      |                        | Receive error                                                                                                                                                                                                         |  |

| RX_ER | In   | HIGH                   | If RX_ER is asserted during Core10100 reception, the frame is received and status of the frame is updated with RX_ER.                                                                                                 |  |

|       |      |                        | The RX_ER signal must be synchronous to the CLKR receive clock.                                                                                                                                                       |  |

|       |      |                        | Receive data valid signal                                                                                                                                                                                             |  |

| RX_DV | In   | HIGH                   | The PHY device must assert RX_DV when a valid data nibble is provided on the RXD signal.                                                                                                                              |  |

|       |      |                        | The RX_DV signal must be synchronous to the CLKR receive clock.                                                                                                                                                       |  |

|       |      |                        | Collision detected                                                                                                                                                                                                    |  |

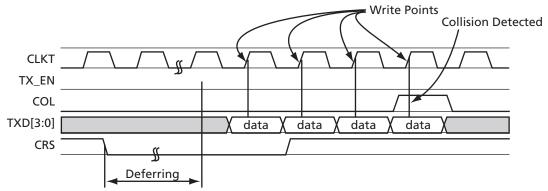

| COL   | In   | HIGH                   | This signal must be asserted by the PHY when a collision is detected on the medium. It is valid only when operating in a half-duplex mode. When operating in a full-duplex mode, this signal is ignored by Core10100. |  |

|       |      |                        | The COL signal is not required to be synchronous to either CLKR or CLKT.                                                                                                                                              |  |

|       |      |                        | The COL signal is sampled internally by the CLKT clock.                                                                                                                                                               |  |

|       |      |                        | Carrier sense                                                                                                                                                                                                         |  |

| CRS   | In   | HIGH                   | This signal must be asserted by the PHY when either a receive or transmit medium is non-idle.                                                                                                                         |  |

|       |      |                        | The CRS signal is not required to be synchronous with either CLKR or CLKT.                                                                                                                                            |  |

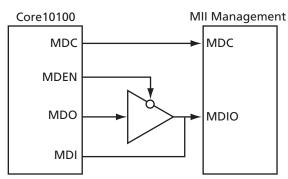

| MDI   | ,    |                        | MII management data input                                                                                                                                                                                             |  |

| MDI   | In   | 1                      | The state of this signal can be checked by reading the CSR9.19 bit.                                                                                                                                                   |  |

|       |      |                        | Receive data recovered and decoded by PHY                                                                                                                                                                             |  |

|       |      |                        | The RXD[0] signal is the least significant bit.                                                                                                                                                                       |  |

| RXD   | In   | 4                      | The RXD bus must be synchronous to the CLKR in MII mode. In RMII mode, RXD[1:0] is used and RXD[3:2] will be grounded by SmartDesign. In RMII mode, RXD[1:0] is synchronous to RMII_CLK.                              |  |

|       |      |                        | Transmit enable                                                                                                                                                                                                       |  |

| TX_EN | Out  | HIGH                   | When asserted, indicates valid data for the PHY on the TXD port.                                                                                                                                                      |  |

|       |      |                        | The TX_EN signal is synchronous to the CLKT transmit clock.                                                                                                                                                           |  |

|       |      |                        | Transmit error                                                                                                                                                                                                        |  |

| TXER  | Out  | HIGH                   | The current version of Core10100 has the TXER signal statically tied to logic 0 (no transmit errors).                                                                                                                 |  |

| MDC   | Out  | Rise                   | MII management clock                                                                                                                                                                                                  |  |

| MIDC  | Out  | Kise                   | This signal is driven by the CSR9.16 bit.                                                                                                                                                                             |  |

| MDO   | 04   | 1                      | MII management data output                                                                                                                                                                                            |  |

| MDO   | Out  | 1                      | This signal is driven by the CSR9.18 bit.                                                                                                                                                                             |  |

| MDEN  | Out  | HIGH                   | MII management buffer control                                                                                                                                                                                         |  |

Table 3-4 · Signals Included in Core10100 and Core10100\_AHBAPB (continued)

| Name     | Туре | Polarity /<br>Bus Size | Description                                                                                                                                                                                         |

|----------|------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXD      | Out  | 4                      | Transmit data The TXD[0] signal is the least significant bit. In RMII mode TXD[1:0] is used. In RMII mode, TXD[1:0] is synchronous to RMII_CLK. The TXD bus is synchronous to the CLKT in MII mode. |

| RMII_CLK | In   | Rise                   | 50 MHz ± 50 ppm clock source shared with RMII PHY. This input is used only in RMII mode. In MII mode, this input will be grounded by SmartDesign.                                                   |

| CRS_DV   | In   | High                   | Carrier sense/receive data valid for RMII PHY                                                                                                                                                       |

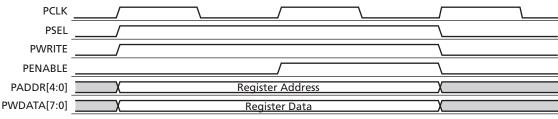

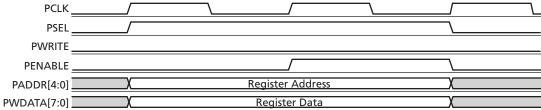

## **AHB/APB Interface Signals**

Table 3-5 lists the signals included in the Core10100\_AHBAPB core.

Table 3-5 · Core10100\_AHBAPB Signals

| Name                                | Туре                 | Description                             |  |  |  |  |

|-------------------------------------|----------------------|-----------------------------------------|--|--|--|--|

| APB Interface (CPU register access) |                      |                                         |  |  |  |  |

| PCLK                                | In                   | APB clock                               |  |  |  |  |

| PRESETN                             | In                   | APB reset (active low and asynchronous) |  |  |  |  |

| PSEL                                | In                   | APB select                              |  |  |  |  |

| PENABLE                             | In                   | APB enable                              |  |  |  |  |

| PWRITE                              | In                   | APB write                               |  |  |  |  |

| PADDR                               | In [7:0]             | APB address                             |  |  |  |  |

| PWDATA                              | In [APB_DWIDTH-1:0]  | APB write data                          |  |  |  |  |

| PRDATA                              | Out [APB_DWIDTH-1:0] | APB read data                           |  |  |  |  |

|                                     | AHB Interface (mea   | mory access)                            |  |  |  |  |

| HCLK                                | In                   | AHB clock                               |  |  |  |  |

| HRESETN                             | In                   | AHB reset (active low and asynchronous) |  |  |  |  |

| HWRITE                              | Out                  | AHB write                               |  |  |  |  |

| HADDR                               | Out [AHB_AWIDTH-1:0] | AHB address                             |  |  |  |  |

| HREADY                              | In                   | AHB ready                               |  |  |  |  |

| HTRANS                              | Out [1:0]            | AHB transfer type                       |  |  |  |  |

| HSIZE                               | Out [2:0]            | AHB transfer size                       |  |  |  |  |

| HBURST                              | Out [2:0]            | AHB burst size                          |  |  |  |  |

| HPROT                               | Out [3:0]            | AHB protection; set to '0000'           |  |  |  |  |

| HRESP                               | In [1:0]             | AHB response                            |  |  |  |  |

| HWDATA                              | Out [AHB_DWIDTH-1:0] | AHB data out                            |  |  |  |  |

| HRDATA                              | In [AHB_DWIDTH-1:0]  | AHB data in                             |  |  |  |  |

| HBUSREQ                             | Out                  | AHB bus request                         |  |  |  |  |

| HGRANT                              | In                   | AHB bus grant                           |  |  |  |  |

All signals listed in Table 3-5 conform to the AMBA specification rev. 2.0.

## **Software Interface**

## **Register Maps**

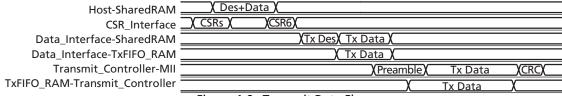

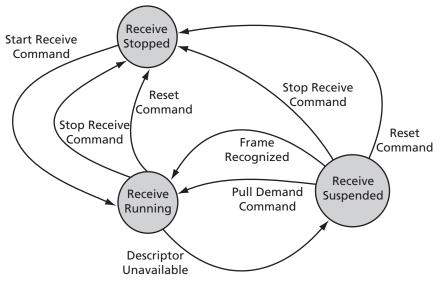

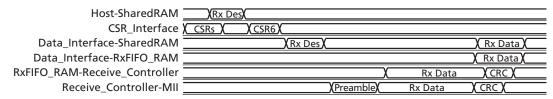

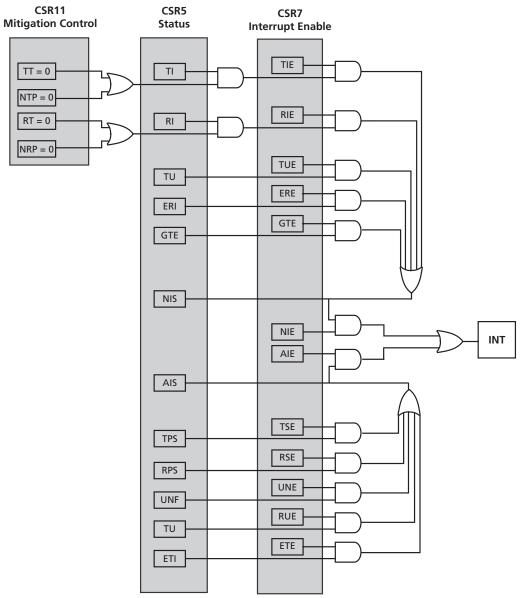

#### **Control and Status Register Addressing**