### Octal IMA/UNI PHY Device

#### **Features**

- Cost effective, single chip, 8-port ATM IMA and UNI processor

- Up to 4 IMA groups over 8 T1/E1 links can be implemented

- Supports MIXED mode; links not assigned to an IMA group can be used in UNI mode

- Versatile PCM Interface to most popular T1 or E1 framers, reducing development time

- Supports Symmetrical and Asymmetrical Operation

- Supports both Common Transmit Clock (CTC) and Independent Transmit Clock (ITC) clocking modes

- Supports T1 ISDN lines

- Provides UTOPIA Level 2 MPHY Interface (MT90220 device slaved to ATM device)

- Complies with ITU G.804 recommendations for performing cell mapping into T1 and E1 transmission systems

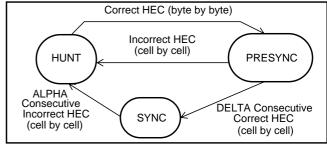

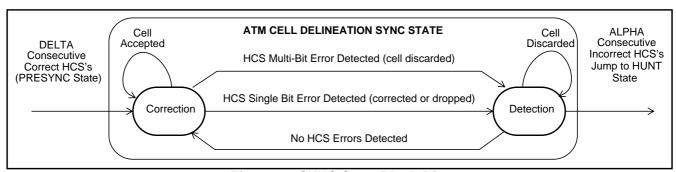

- Provides ATM framing using cell delineation according to the ITU I.432 cell delineation process

- Provides Header Error Control (HEC)

verification and generation, error detection,

Filler cell filtering (IMA mode) and Idle/

Unassigned cell filtering (UNI mode)

- Provides statistics to support MIB

- Connects to popular asychronous SRAM

- Provides statistics on the number of HEC errors

- 8 bit Microprocessor Interface, compatible with Intel and Motorola

- 3.3V operation / 5V tolerant inputs

- MQFP-208 pin

- JTAG Test support

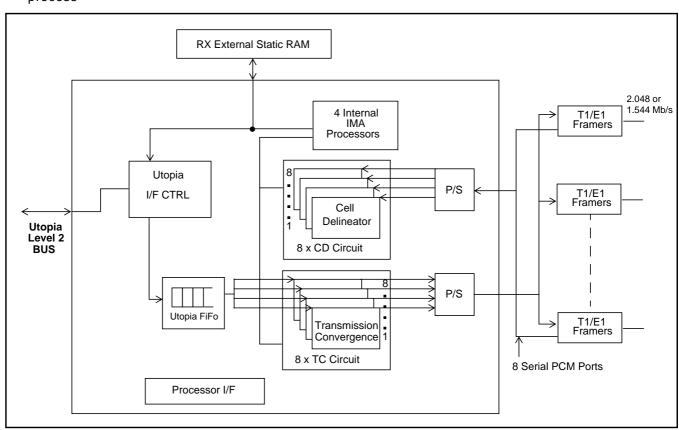

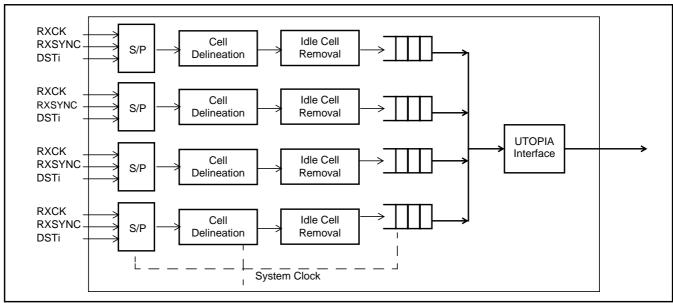

Figure 1 - MT90220 Block Diagram with Built-in IMA functions for 4 IMA Groups over up to 8 links

#### **Applications**

- Cost effective single chip solution to implement IMA and UNI links over T1 or E1 in all public or private UNI, NNI and B-ICI applications

- ATM Edge switch IMA and UNI Line Card Design

- Can be used for cost reduction in current applications based on FPGA implementation

#### **Description**

The MT90220 device is targeted to systems implementing the ATM FORUM UNI specifications for T1/E1 rates or Inverse Multiplexing for ATM (IMA). In the MT90220 architecture, up to 8 physical and independent T1/E1 streams can be terminated through the utilization of off-the-shelf, traditional T1/E1 framers and LIUs. This allows ATM designers to leverage previous T1/E1 design experience, hardware and software implementation, and to select the best T1/E1 framer for the required application.

The MT90220 device provides ATM system designers with a flexible architecture when implementing ATM access over existing and deployed trunk interfaces, allowing a migration towards ATM service technology. In addition to allowing for the design of ATM UNI specifications for T1/E1 rates, the MT90220 device is compliant with the ATM FORUM IMA specifications for controlling IMA groups of up to 8 trunks in a single chip. The MT90220 can be configured to operate in different modes to facilitate the implementation of the IMA function at both CPE and Central Office sites. For systems targeting ATM over T1/E1 with IMA and UNI operating simultaneously, the MT90220 device provides the ideal architecture and capabilities.

The device provides up to 4 internal IMA circuits and allows for bandwidth scaleability through the use of the UTOPIA MPHY, Level 2 specification at 25Mhz.

The implementation of the IMA as per AF-PHY-0086.001 Inverse Multiplexing for ATM (IMA) Specification Version 1.1 is divided into hardware and software functions. Hardware functions are implemented in the MT90220 device and software functions are implemented by the user. Additional hardware functions are included to assist in the collection of statistical information to support MIB implementation.

Hardware functions that are implemented in the MT90220 device are:

- Utopia Level 2 PHY Interface

- Incoming HEC verification and correction (optional),

- Generation of a new HEC byte

- Format outgoing bytes into multi-vendor PCM formats

- Retrieve ATM Cells from the incoming multivendor PCM format

- Perform cell delineation

- Provide various counters to assist in performance monitoring

Hardware functions that are implemented by the IMA processor in the MT90220 device are:

- Transmit scheduler (one per IMA group)

- Generation of the TX IMA Data Cell Rate

- Generation and insertion of ICP cells, Filler

Cells and Stuff Cells in IMA mode and Idle Cells

in UNI (non-IMA) mode; the ICP cells are

programmed by the user and the Filler and Idle

cells are pre-defined

- Retrieve and process ICP cells in IMA Mode

- Perform IMA Frame synchronization

- Management of RX links to be part of the internal re-sequencer when active

- Extraction of RX IMA Data Cell Rate

- Verification of delays between links

- Perform re-sequencing of ATM cells using external asynchronous Static RAM

- Can accommodate more than 400 msec of link differential delay depending on the amount of external memory

- Provide structured Interrupt scheme to report various events.

| 1.0 Device Architecture                           | 8  |

|---------------------------------------------------|----|

| 1.1 Software Functions                            | 8  |

| 1.1.1 Link State Machines                         | 8  |

| 1.1.2 IMA Group State Machines                    | 8  |

| 1.1.3 Link Addition, Removal or Restoration       | 8  |

| 1.1.4 Interrupt                                   | 8  |

| 1.1.5 Signaling and Rate Adjustment               | 8  |

| 1.1.6 Performance Monitoring                      | 8  |

| 1.2 Hardware Functions                            | 9  |

|                                                   |    |

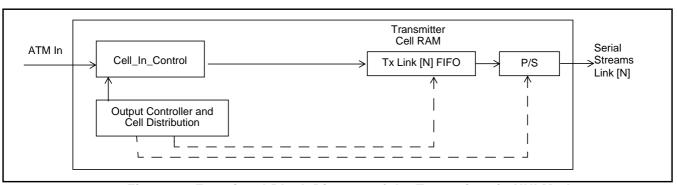

| 2.0 The ATM Transmit Path                         | 9  |

| 2.1 Cell_In_Control                               | 9  |

| 2.2 The ATM Transmission Convergence              | 10 |

| 2.2.1 TX Cell Ram and TX FIFO Length              | 10 |

| 2.3 Parallel to Serial PCM Interface              | 11 |

| 2.4 ATM Transmit Path in IMA Mode                 | 11 |

| 2.4.1 IMA Frame Length (M)                        | 11 |

| 2.4.2 Position of the ICP Cell in the IMA Frame   | 11 |

| 2.4.3 Transmit Clock Operation                    | 11 |

| 2.4.4 Stuff Cell Rate                             | 12 |

| 2.4.5 IMA Data Cell Rate                          |    |

| 2.4.6 IMA Controller (RoundRobin Scheduler)       |    |

| 2.4.7 ICP Cell Generator                          |    |

| 2.4.8 IMA Frame Programmable Interrupt            |    |

| 2.4.9 Filler Cell Definition                      |    |

| 2.4.10 TX IMA Group Start-Up                      |    |

| 2.4.11 TX Link Addition                           |    |

| 2.4.12 TX Link Deletion                           |    |

| 2.5 ATM Transmit Path in UNI Mode                 |    |

|                                                   |    |

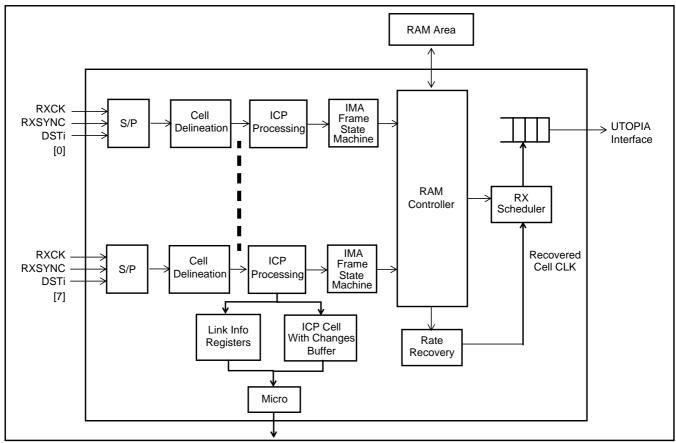

| 3.0 The ATM Receive Path                          |    |

| 3.1 Cell Delineation Function                     |    |

| 3.2 De-Scrambling and ATM Cell Filtering          |    |

| 3.3 ATM Receive Path in IMA Mode                  |    |

| 3.3.1 ICP Cell Processor                          |    |

| 3.3.1.1 IMA Frame Synchronization                 |    |

|                                                   | 18 |

| 3.3.1.3 RX OAM Label                              |    |

| 3.3.2 Out of IMA Frame (OIF) Condition            |    |

| 3.3.3 Link Out Of IMA Frame (LIF) Synchronization |    |

| 3.3.4 Filler Cell Handling                        |    |

| 3.3.5 Stuff Cell Handling                         |    |

| 3.3.6 Received ICP Cell Buffer                    | 18 |

| 3.3.7 Rate Recovery                                                  | 19 |

|----------------------------------------------------------------------|----|

| 3.3.8 Cell Buffer/RAM Controller                                     | 19 |

| 3.3.9 Cell Sequence Recovery                                         | 19 |

| 3.3.10 Delay Between Links                                           | 20 |

| 3.3.10.1 RX Recombiner Delay Value                                   | 20 |

| 3.3.10.2 RX Maximum Operational Delay Value                          | 20 |

| 3.3.10.3 Link Out of Delay Synchronization (LODS)                    | 20 |

| 3.3.10.4 Negative Delay Values                                       | 21 |

| 3.3.10.5 Measured Delay Between Links                                | 21 |

| 3.3.10.6 Incrementing/Decrementing the Recombiner Delay              | 21 |

| 3.3.11 RX IMA Group Start-Up                                         | 21 |

| 3.3.12 Link Addition                                                 | 22 |

| 3.3.13 Link Deletion                                                 | 22 |

| 3.3.14 Disabling an IMA Group                                        | 22 |

| 3.4 The ATM Receive Path in UNI                                      | 22 |

| 4.0 Description of the PCM Interface                                 |    |

| 4.1 Serial to Parallel (S/P) and Parallel to Serial (P/S) Converters |    |

| 4.2 PCM System Interface Modes                                       |    |

| 4.2.1 Mode 2 and 6: ST-BUS Interface for T1                          |    |

| 4.2.1.1 Detailed S1-BOS Spaced Mapping (3 of Every 4 Charmels)       |    |

| 4.2.1.3 Detailed ST-BUS Grouped Mapping (24 Consecutive Charmels)    |    |

| 4.2.1.3 Detailed 31-B03 ISDN Mapping (11 ISDN Modes)                 |    |

| 4.2.3 Mode 1 and 5: Generic PCM Interface for T1                     |    |

| 4.2.3.1 1.544 MHz Clock                                              |    |

| 4.2.3.2 2.048 MHz Clock                                              |    |

| 4.2.4 Mode 3 and 7: Generic PCM Interface for E1                     |    |

| 4.2.5 TXSYNC Signal in Mode 5 and 7.                                 |    |

| 4.3 Clocking Options                                                 |    |

| 4.3.1 Verification of the RXSYNC Period                              |    |

| 4.3.2 Verification of the TXSYNC Period                              |    |

| 4.3.3 Primary and Secondary Reference Signals                        |    |

| 4.3.4 Verification of Clock Activity                                 |    |

| 4.3.5 Clock Selection                                                |    |

|                                                                      |    |

| 5.0 UTOPIA Interface Operation                                       |    |

| 5.1 ATM Input Port                                                   |    |

| 5.2 ATM Output Port                                                  |    |

| 5.3 UTOPIA Operation With a Single PHY                               |    |

| 5.4 UTOPIA Operation with Multiple PHY                               |    |

| 5.5 UTOPIA Operation in UNI Mode                                     |    |

| 5.6 UTOPIA Operation in IMA Mode                                     |    |

| 5.7 Examples of UTOPIA Operation Modes                               | 32 |

| 6.0 Support Blocks                                                                   | 33 |

|--------------------------------------------------------------------------------------|----|

| 6.1 Counter Block                                                                    | 33 |

| 6.1.1 UTOPIA Input I/F counters                                                      | 33 |

| 6.1.2 Transmit PCM I/F Counters                                                      | 33 |

| 6.1.3 Receive PCM I/F Counters                                                       | 33 |

| 6.1.4 Access to the Counters                                                         | 33 |

| 6.2 Interrupt Block                                                                  | 34 |

| 6.2.1 IRQ Master Status and IRQ Master Enable Registers                              | 34 |

| 6.2.2 IRQ Link Status and IRQ Link Enable Registers                                  | 35 |

| 6.2.2.1 Bit 7 and 6 of IRQ Link 0 Status and IRQ Link 0 Enable Registers             | 35 |

| 6.2.3 IRQ Link UNI Overflow and IRQ UTOPIA Input UNI Overflow Status Registers       | 36 |

| 6.2.4 IRQ IMA Group Overflow Status and Enable Registers                             |    |

| 6.2.5 IRQ IMA Overflow Status and RX UTOPIA IMA Group FIFO Overflow Enable Registers | 36 |

| 6.3 Register and Memory Map                                                          | 36 |

| 6.3.1 Access to the Various Registers                                                | 36 |

| 6.3.2 Direct Access                                                                  | 37 |

| 6.3.3 Indirect Access                                                                | 37 |

| 6.3.4 Clearing of Status Bits                                                        | 37 |

| 6.3.4.1 Toggle Bit                                                                   | 37 |

| 6.3.5 Test Modes                                                                     | 37 |

| 7.0 Register Descriptions                                                            | 41 |

| 7.2 TX Registers Description                                                         |    |

| 7.3 TX ICP Register Description                                                      |    |

| 7.4 RX Registers Description                                                         |    |

| 7.5 RX ICP Cell Registers Description                                                |    |

| 7.6 External SRAM Register Description                                               |    |

| 7.7 RX Delay Registers Description                                                   |    |

| 7.8 RX Recombiner Registers Description                                              |    |

| 7.9 TX/RX and PLL Control Registers Description                                      |    |

| 7.10 Counter Registers Description                                                   |    |

| 7.11Interrupt Registers Description                                                  |    |

| 7.12 Miscellaneous Registers Description                                             | 78 |

|                                                                                      |    |

| 3.0 Application Notes                                                                |    |

| 8.1 Connecting the MT90220 to Various T1/E1 Framers                                  | 79 |

|                                                                                      |    |

| 9.0 AC/DC Characteristics                                                            | 85 |

| Packaging Information              | 100 |

|------------------------------------|-----|

| List of Changes                    | 102 |

| List of Abbreviations and Acronyms | 104 |

| ATM Glossary                       | 104 |

## **List of Figures**

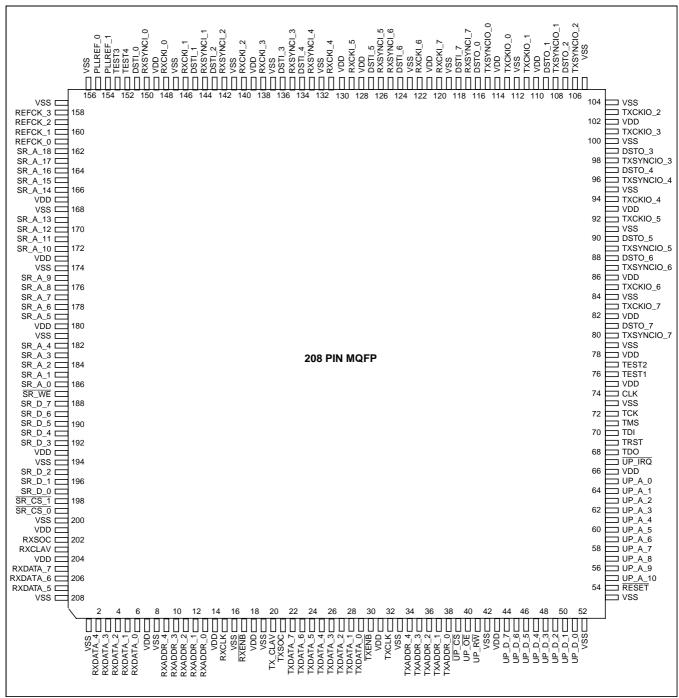

| Figure 2 - Pin Connections                                              | 3   |

|-------------------------------------------------------------------------|-----|

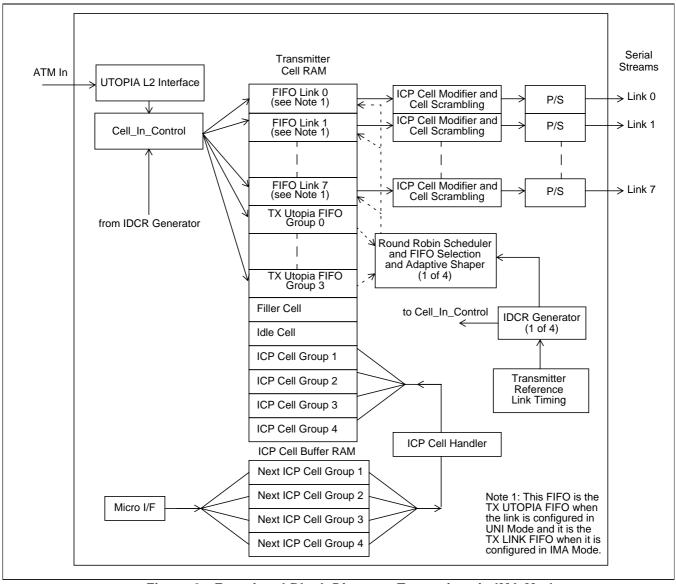

| Figure 3 - Functional Block Diagram -Transmitter in IMA Mode            | 10  |

| Figure 4 - Functional Block Diagram of the Transmitter in UNI Mode      | 14  |

| Figure 5 - Cell Delineation State Diagram                               | 15  |

| Figure 6 - SYNC State Block Diagram                                     | 15  |

| Figure 7 - The MT90220 Receiver Circuit in IMA Mode                     | 17  |

| Figure 8 - Example of UNI Mode Operation                                | 23  |

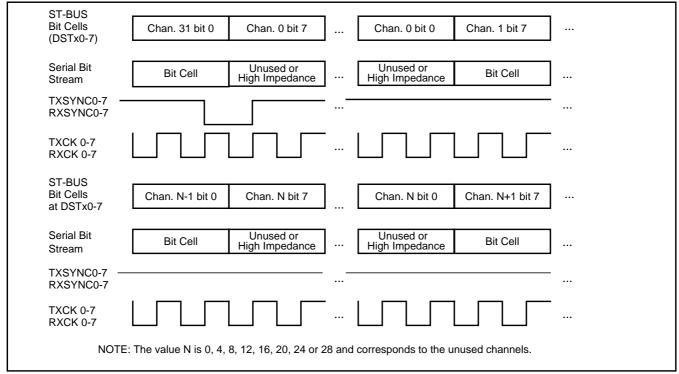

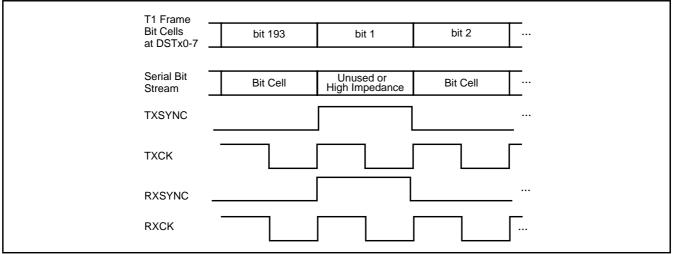

| Figure 9 - PCM Mode 2 and 6: ST-BUS Interface for T1 (Spaced Mapping)   | 25  |

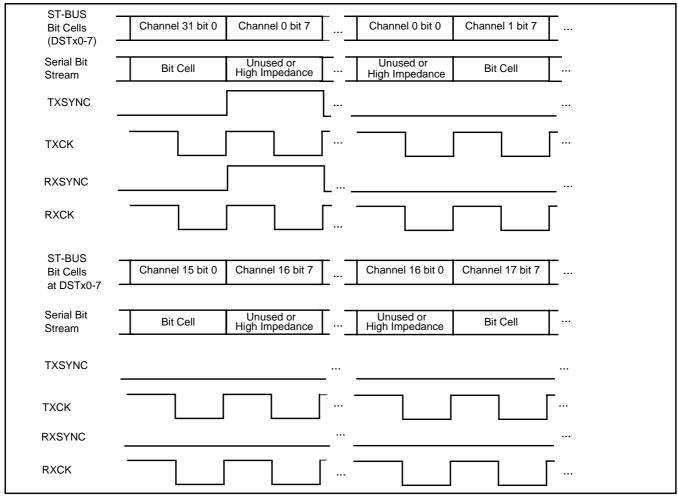

| Figure 10 - PCM Mode 2 and 6: ST-BUS Interface for T1 (Grouped Mapping) | 26  |

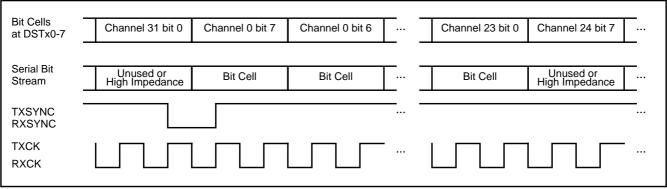

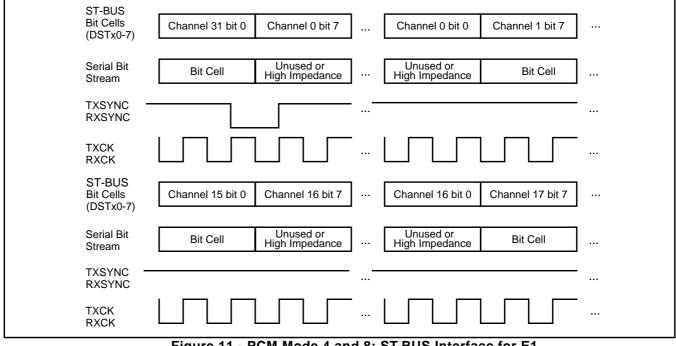

| Figure 11 - PCM Mode 4 and 8: ST-BUS Interface for E1                   | 27  |

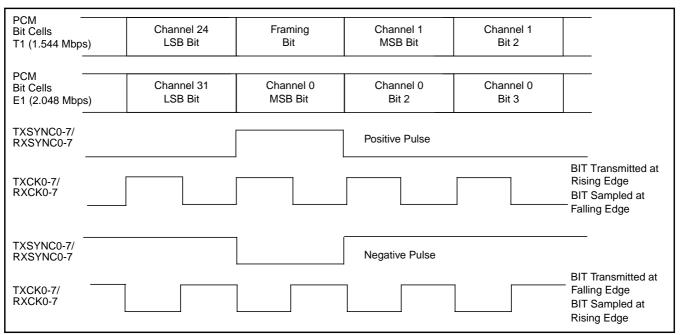

| Figure 12 - Mode 1 and 5: Generic PCM Interface for T1                  | 28  |

| Figure 13 - Mode 3 and 7: Generic PCM Interface for E1                  | 29  |

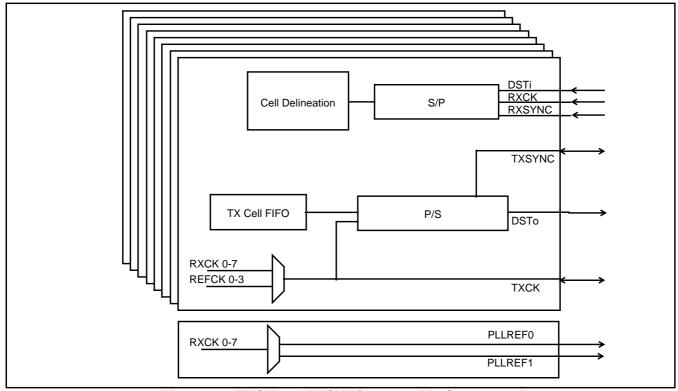

| Figure 14 - TXCK and TXSYNC Output Pin Source Options                   | 29  |

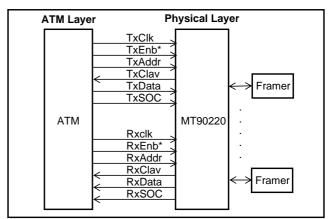

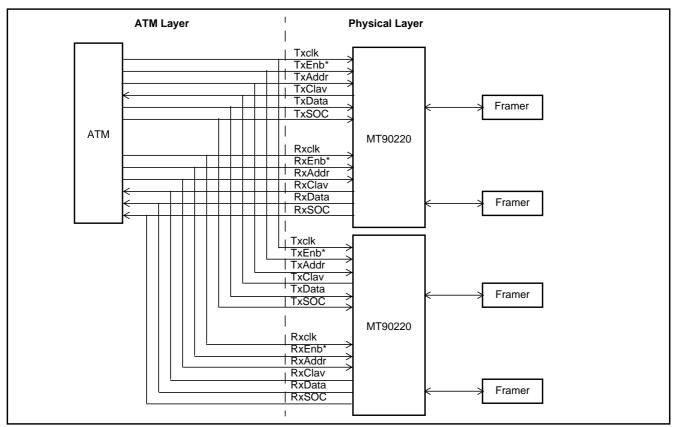

| Figure 15 - ATM Interface to MT90220                                    | 32  |

| Figure 16 - ATM Interface to Multiple MT90220s                          | 32  |

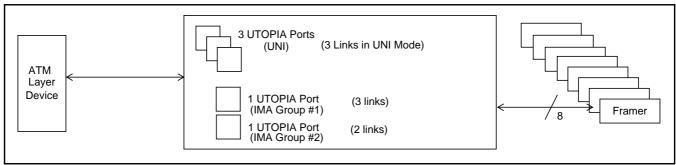

| Figure 17 - ATM Mixed-Mode Interface to One MT90220                     | 33  |

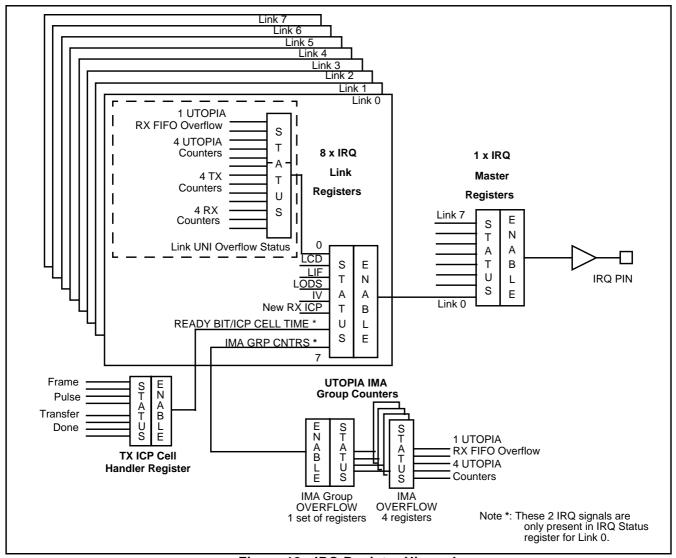

| Figure 18 - IRQ Register Hierarchy                                      | 34  |

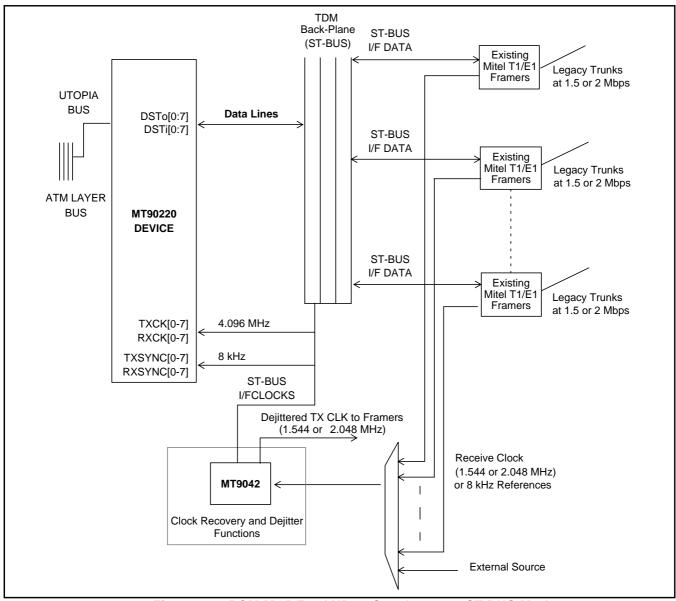

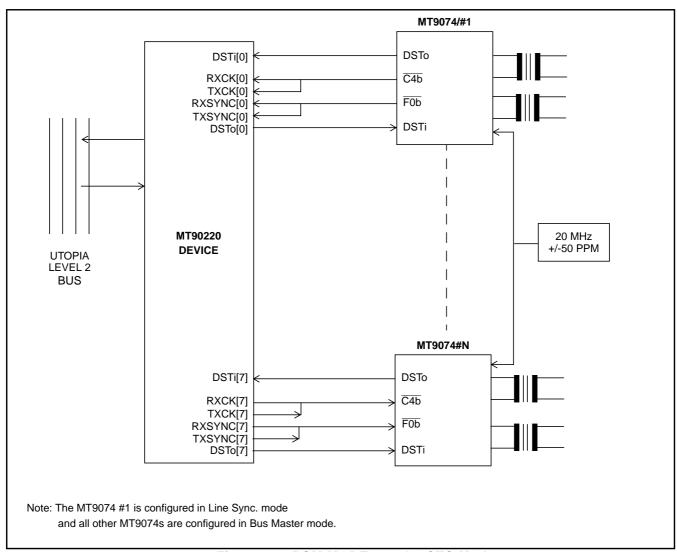

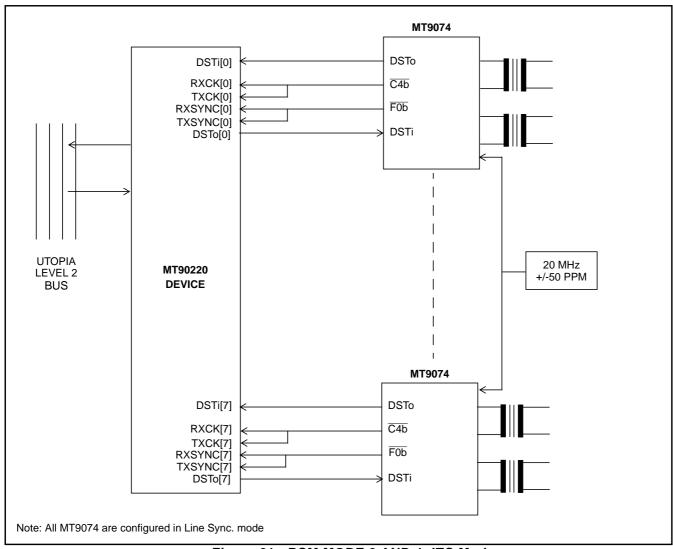

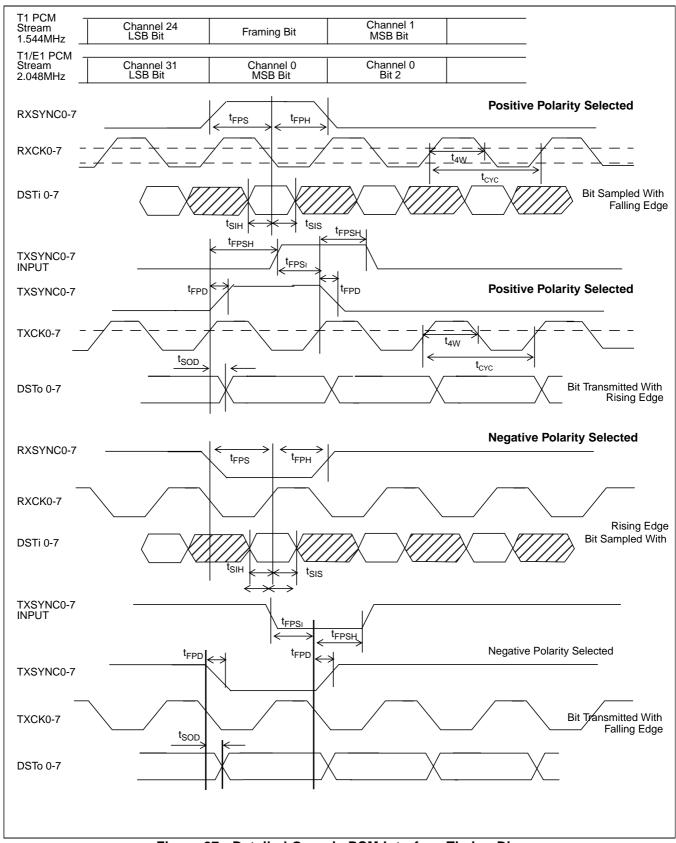

| Figure 19 - PCM MODE 2 AND 4: Synchronous ST-BUS Mode                   | 80  |

| Figure 20 - PCM MODE 2 and 4 CTC Mode                                   | 81  |

| Figure 21 - PCM MODE 2 AND 4: ITC Mode                                  | 82  |

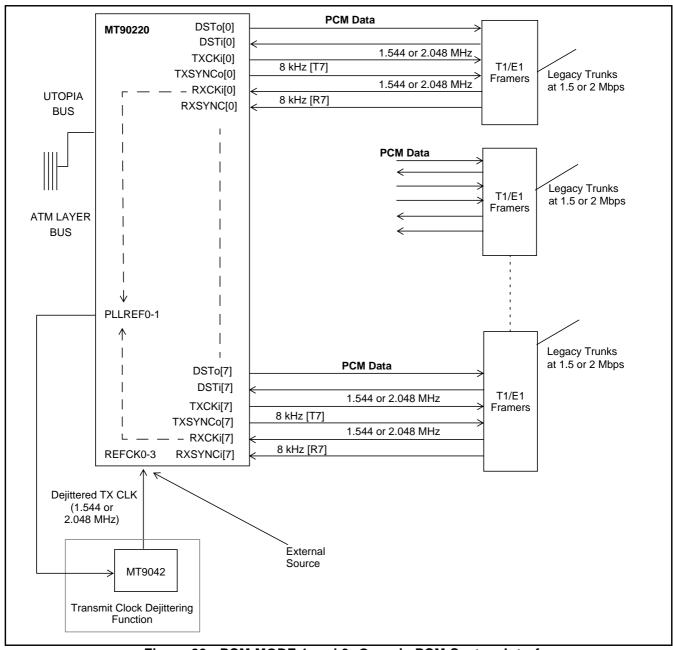

| Figure 22 - PCM MODE 1 and 3: Generic PCM System Interface              | 83  |

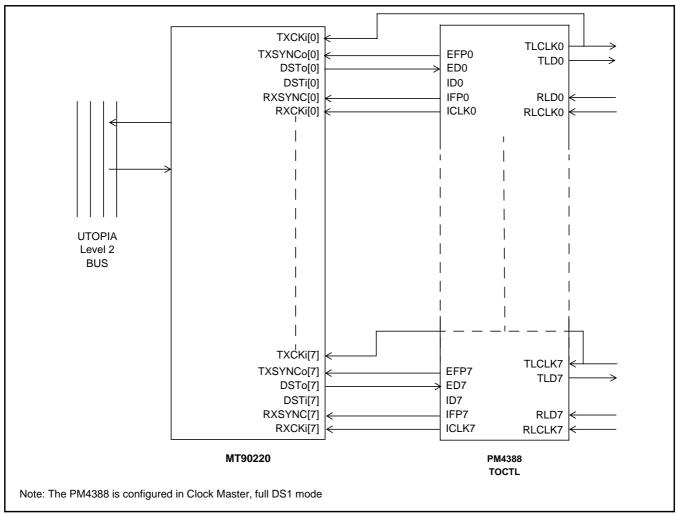

| Figure 23 - PCM MODE 5 and 7: Asynchronous Operations                   | 84  |

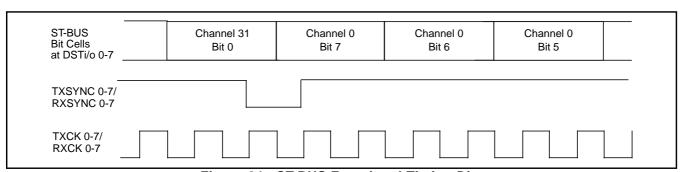

| Figure 24 - ST-BUS Functional Timing Diagram                            | 86  |

| Figure 25 - ST-BUS Timing Diagram                                       | 87  |

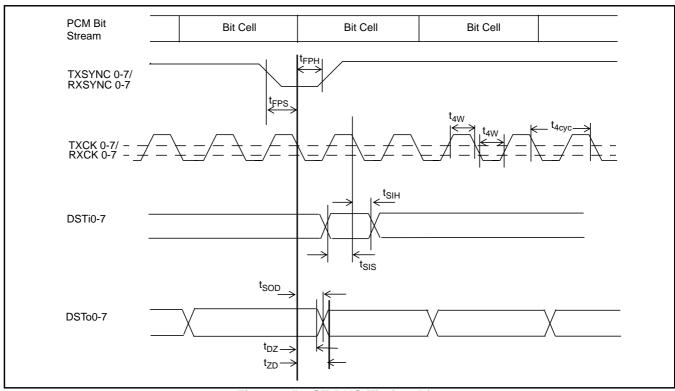

| Figure 26 - Generic PCM Interface Timing Diagram                        | 88  |

| Figure 27 - Detailed Generic PCM Interface Timing Diagram               | 89  |

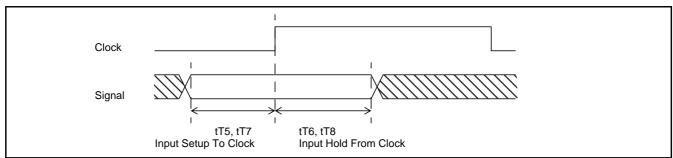

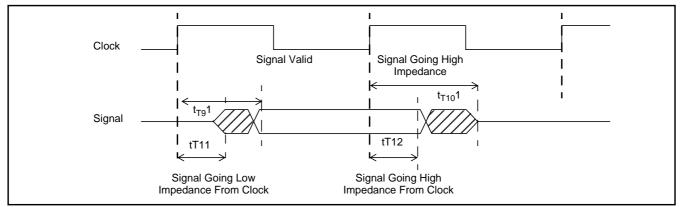

| Figure 28 - Setup and Hold Time Definition                              | 91  |

| Figure 29 - Tri-State Timing                                            | 91  |

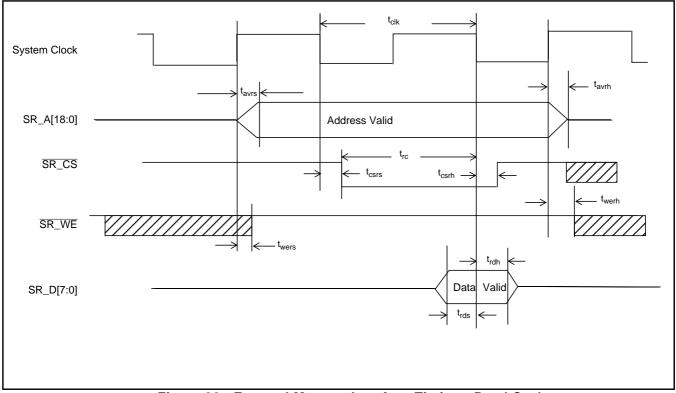

| Figure 30 - External Memory Interface Timing - Read Cycle               | 92  |

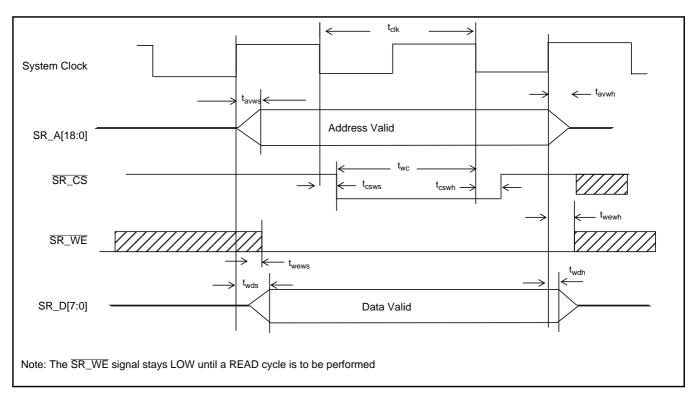

| Figure 31 - External Memory Interface Timing - Write Cycle              | 93  |

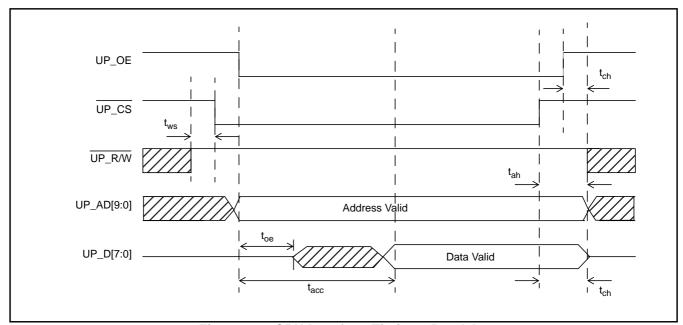

| Figure 32 - CPU Interface Timing - Read Access                          | 95  |

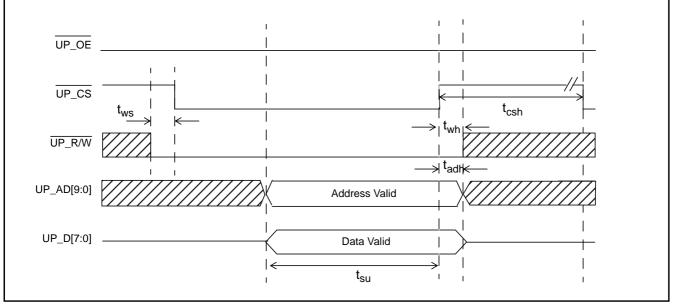

| Figure 33 - CPU Interface Motorola Timing - Write Access                | 96  |

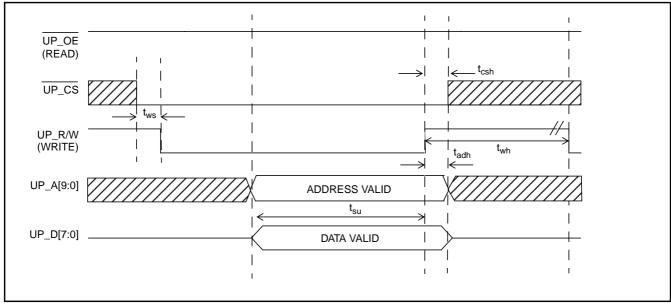

| Figure 34 - CPU Interface Intel Timing - Write Access                   | 97  |

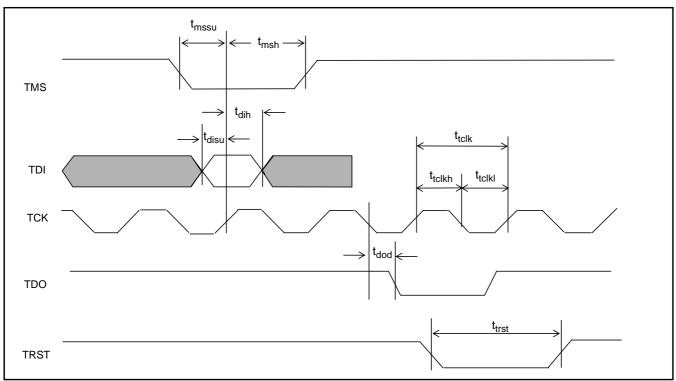

| Figure 35 - JTAG Port Timing                                            |     |

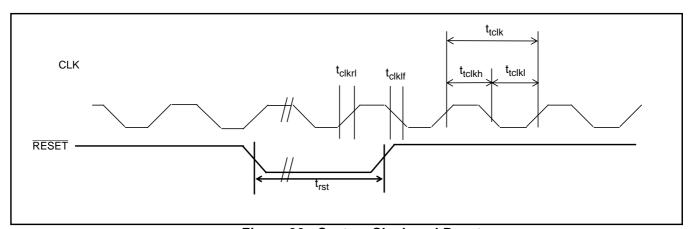

| Figure 36 - System Clock and Reset                                      |     |

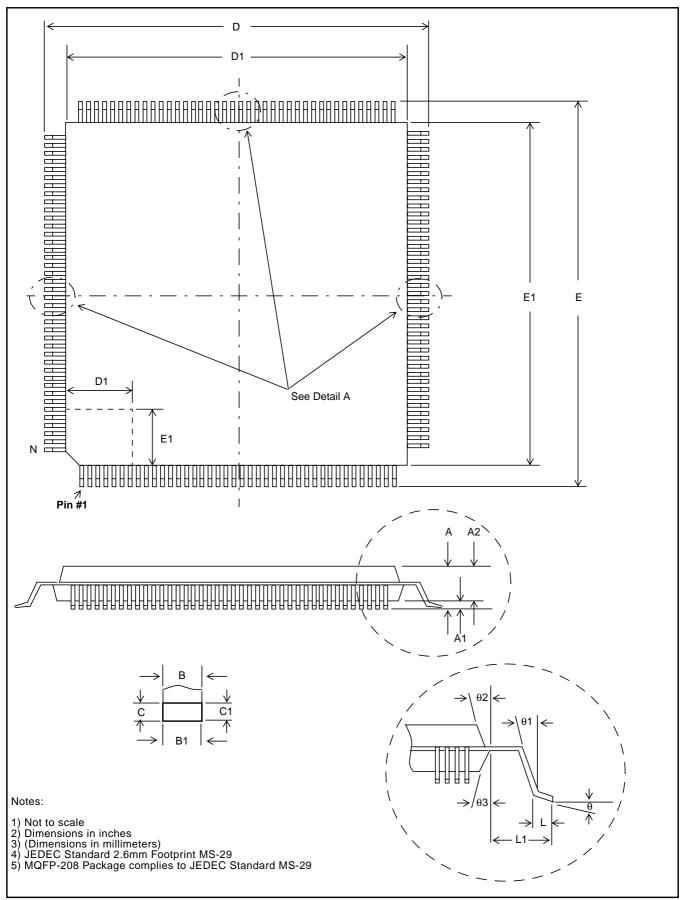

| Figure 37 - Matric Quad Flat Package - 208 Pin                          | 100 |

## **List of Tables**

| Pin Description                                               |    |

|---------------------------------------------------------------|----|

| Pinout Summary                                                | 7  |

| Table 1 - IDCR Integration Register Value                     | 12 |

| Table 2 - ICP Cell Description                                |    |

| Table 3 - Cell Acquisition Time                               | 16 |

| Table 4 - Differential Delay for Various Memory Configuration | 19 |

| Table 5 - Conversion Factors Time/Cell (msec)                 | 20 |

| Table 6 - PCM Modes                                           |    |

| Table 7 - PCM Clock and Mapping Options                       | 24 |

| Table 8 - T1Channel Mapping Using 3 Channels Every 4 Channels | 25 |

| Table 9 - T1 Channel Mapping Using 24 Consecutive Channels    |    |

| Table 10 - Channel Mapping from ST-BUS to E1                  | 26 |

| Table 11 - Register Summary                                   | 38 |

| Table 12 - UTOPIA Input Link Address Registers                | 41 |

| Table 13 - UTOPIA Input Group Address Registers               | 41 |

| Table 14 - UTOPIA Input Link PHY Enable Register              | 41 |

| Table 15 - UTOPIA Input Group PHY Enable Register             | 42 |

| Table 16 - Utopia Input Control Register                      | 42 |

| Table 17 - UTOPIA Output Link Address Registers               | 42 |

| Table 18 - UTOPIA Output Group Address Registers              | 43 |

| Table 19 - UTOPIA Output Link PHY Enable Register             | 43 |

| Table 20 - UTOPIA Output Group PHY Enable Register            | 43 |

| Table 21 - RX UTOPIA IMA Group FIFO Overflow Enable Register  | 44 |

| Table 22 - RX UTOPIA Link FIFO Overflow Enable Register       | 44 |

| Table 23 - TX Cell RAM Control Register                       | 45 |

| Table 24 - TX UTOPIA FIFO Level Register                      | 45 |

| Table 25 - TX FIFO Length Definition Register 1               | 45 |

| Table 26 - TX FIFO Length Definition Register 2               | 45 |

| Table 27 - TX FIFO Length Definition Register 3               | 46 |

| Table 28 - TX FIFO Length Definition Register 4               | 46 |

| Table 29 - TX FIFO Length Definition Register 5               | 46 |

| Table 30 - TX FIFO Length Definition Register 6               | 46 |

| Table 31 - TX Group Control Mode Registers                    | 47 |

| Table 32 - TX Link ID Registers                               | 47 |

| Table 33 - TX ICP Cell Offset Registers                       | 47 |

| Table 34 - TX IDCR Integration Registers                      | 48 |

| Table 35 - TX Link Control Registers                          | 48 |

| Table 36 - TX IMA Control Registers                           | 49 |

| Table 37 - TX IMA Mode Status Register                        | 49 |

| Table 38 - TX ICP Cell Handler Register                       | 50 |

| Table 39 - TX ICP Cell Interrupt Enable Register              |    |

| Table 40 - TX ICP Cell Registers                              | 51 |

| Table 41 - RX Link Control Registers                          | 52 |

| Table 42 - Cell Delineation Register                          | 52 |

| Table 43 - Loss of Delineation Register                       |    |

| Table 44 - IMA Frame Delineation Register                     |    |

| Table 45 - RX OAM Label Register                              | 53 |

## **List of Tables**

| Table 46 - RX OIF Status Register                             |      |

|---------------------------------------------------------------|------|

| Table 47 - RX OIF Counter Clear Command Register              | . 54 |

| Table 48 - RX Load Values/Link Select Register                | . 54 |

| Table 49 - RX Link IMA ID Registers                           | . 54 |

| Table 50 - RX ICP Cell Offset Register                        | . 55 |

| Table 51 - RX Link Frame Sequence Number Register             | 55   |

| Table 52 - RX Link SCCI Sequence Number Register              | 55   |

| Table 53 - RX Link OIF Counter Value Register                 | . 55 |

| Table 54 - RX Link ID Number Register                         |      |

| Table 55 - RX State Register                                  | . 56 |

| Table 56 - RX ICP Cell Type RAM Register 1                    | . 57 |

| Table 57 - ICP Cell Type RAM Register 2                       |      |

| Table 58 - RX ICP Cell Buffer Increment Read Pointer Register |      |

| Table 59 - RX ICP Cell Level FIFO Status Register             | . 59 |

| Table 60 - Test Mode Enable Register                          |      |

| Table 61 - SRAM Control Register                              | . 60 |

| Table 62 - RX External SRAM Read/Write Data                   | 60   |

| Table 63 - RX External SRAM Read/Write Address 0              |      |

| Table 64 - RX External SRAM Read/Write Address 1              |      |

| Table 65 - RX External SRAM Read/Write Address 2              |      |

| Table 66 - RX External SRAM Control Register                  | 62   |

| Table 67 - Increment/Decrement Delay Control Register         |      |

| Table 68 - RX Delay Select Register                           |      |

| Table 69 - RX Delay MSB Register                              |      |

| Table 70 - RX Delay LSB Register                              |      |

| Table 71 - RX Delay Link Number Register                      |      |

| Table 72 - RX Guardband/Delta Delay LSB Register              |      |

| Table 73 - RX Guardband/Delta Delay MSB Register              |      |

| Table 74 - RX Maximum Operational Delay LSB Register          |      |

| Table 75 - RX Maximum Operational Delay MSB Register          |      |

| Table 76 - RX Recombiner Registers                            |      |

| Table 77 - RX Recombiner Delay Control Registers              |      |

| Table 78 - Enable Recombination Status                        |      |

| Table 79 - RX Reference Link Control Registers                |      |

| Table 80 - RX IDCR Integration Registers                      |      |

| Table 81 - TX PCM Link Control Register Number 2              |      |

| Table 82 - TX PCM Link Control Register Number 1              |      |

| Table 83 - RX PCM Link Control Register                       |      |

| Table 84 - PLL Reference Control Register                     |      |

| Table 85 - Clock Activity Register                            |      |

| Table 86 - RX Sync. Status Register                           |      |

| Table 87 - TX Sync. Status Register                           |      |

| Table 88 - TX Clock Disabled Status                           |      |

| Table 89 - PLL REF Clock Disabled Status/Device Rev           |      |

| Table 90 - Counter Byte Number 3 Register                     |      |

| Table 91 - Counter Byte Number 2 Register                     |      |

| Table 92 - Counter Byte Number 1 Register                     | 73   |

## **List of Tables**

| Table 93 - Select Counter Register                                              | 74 |

|---------------------------------------------------------------------------------|----|

| Table 94 - Counter Transfer Command Register                                    | 74 |

| Table 95 - IRQ Master Status Register                                           | 75 |

| Table 96 - IRQ Master Enable Register                                           | 75 |

| Table 97 - IRQ Link Status Registers                                            | 75 |

| Table 98 - IRQ Link Enable Registers                                            |    |

| Table 99 - IRQ IMA Group Overflow Status Register                               | 76 |

| Table 100 - IRQ IMA Group Overflow Enable Register                              | 76 |

| Table 101 - IRQ IMA Overflow Status Registers                                   | 76 |

| Table 102 - IRQ UTOPIA UNI Overflow Status Registers                            | 77 |

| Table 103 - IRQ Link UNI Overflow Status Registers                              | 77 |

| Table 104 - General Status Register                                             | 78 |

| Table 105 - Test 1 Register                                                     |    |

| Table 106 - Test 2 Register                                                     | 78 |

| Absolute Maximum Conditions                                                     | 85 |

| Recommended Operating Conditions                                                | 85 |

| DC Electrical Characteristics                                                   | 86 |

| AC Electrical Characteristics - PCM PORT ST-BUS Interface Mode                  | 86 |

| AC Electrical Characteristics - Generic PCM Interface Mode                      | 88 |

| AC Electrical Characteristics - Utopia Interface Transmit Timing                | 90 |

| AC Electrical Characteristics - Receive Timing                                  | 90 |

| AC Electrical Characteristics - External Memory Interface Timing - Read Access  | 92 |

| AC Electrical Characteristics - External Memory Interface Timing - Write Access | 93 |

| AC Electrical Characteristics - CPU Interface Timing - Read Cycle               | 95 |

| AC Electrical Characteristics - CPU Interface Motorola Timing - Write Cycle     | 96 |

| AC Electrical Characteristics - CPU Interface Intel Timing - Write Cycle        | 97 |

| AC Electrical Characteristics - JTAG Port and RESET Pin Timing                  | 98 |

| AC Electrical Characteristics - System Clock and Reset                          |    |

| Metric Quad Flat Package Dimensions1                                            | 00 |

Figure 2 - Pin Connections

## **Pin Description**

| Pin #                                | Name            | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                 | -     | ATM Input Port Signals (UTOPIA Transmit Interface)                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22, 23, 24,<br>25, 26, 27,<br>28, 29 | TxData<br>[7:0] | I     | UTOPIA Transmit Data Bus. Byte-wide data driven from ATM LAYER device to MT90220. Bit 7 is the MSB. All arriving data between the last byte of the previous cell and the first byte of the following cell (indicated by the SOC signal) is ignored.                                                                                                                                                                                                             |

| 21                                   | TxSOC           | I     | UTOPIA Transmit Start of Cell Signal. Active HIGH signal asserted by the ATM LAYER device when TxData[7:0] contains the first valid byte of the cell. After this signal is high, the following 52 bytes should contain valid data. The MT90220 waits for another TxSOC signal after reading a complete cell.                                                                                                                                                    |

| 32                                   | TxClk           | I     | UTOPIA Transmit Clock. Transfer clock from the ATM Layer device to the MT90220 which synchronizes data transfers on TxData[7:0]. This signal is the clock of the incoming data. Data is sampled on the rising edge of this signal.                                                                                                                                                                                                                              |

| 30                                   | TxEnb           | I     | UTOPIA Transmit Data Enable. Active LOW signal asserted by the ATM LAYER device during cycles when TxData contains valid cell data.                                                                                                                                                                                                                                                                                                                             |

| 20                                   | TxClav          | 0     | UTOPIA Transmit Cell Available Indication Signal. For cell-level flow control in a MPHY environment, TxClav is an active high tri-stateable signal from the MT90220 to the ATM LAYER device. A polled MT90220 drives TxClav only during each cycle following one with its address on the TxAddr lines. The polled MT90220 asserts TxClav high to indicate it can accept the transfer of a complete cell, otherwise it deasserts the signal.                     |

| 34, 35, 36,<br>37, 38                | TxAddr<br>[4:0] | I     | <b>Transmit Address</b> . Five bit wide true data driven from the ATM to the PHY layer to poll and select the appropriate MT90220. TxAddr[4] is the MSB. Each MT90220 keeps its addresses. The value for the Tx and Rx portions of the MT90220 can be different                                                                                                                                                                                                 |

|                                      | A               | ΓΜ Οι | utput Port Signals (UTOPIA Receive Interface) (see Note 1)                                                                                                                                                                                                                                                                                                                                                                                                      |

| 205, 206,<br>207, 2, 3,<br>4, 5, 6   | RxData<br>[7:0] | 0     | <b>UTOPIA Receive Data Bus.</b> Byte-wide data driven from MT90220 to ATM layer device. RxData[7] is the MSB. To support multiple PHY configurations, RxData is tri-stateable, enabled only in cycles following those with RxEnb asserted.                                                                                                                                                                                                                      |

| 202                                  | RxSOC           | 0     | UTOPIA Receive Start of Cell Signal. Active high asserted by the MT90220 when RxData contains the first valid byte of a cell. To support multiple PHY configurations, RxSOC is tri-stateable, enabled only in cycles following those with RxEnb asserted.                                                                                                                                                                                                       |

| 15                                   | RxClk           | I     | UTOPIA Receive Byte Clock. This signal is the clock of the outgoing data. Data changes after the rising edge of this signal. The RxClk needs to be synchronized with the system clock.                                                                                                                                                                                                                                                                          |

| 17                                   | RxEnb           | I     | <b>UTOPIA Receive Data Enable.</b> Active LOW signal asserted by the ATM layer device to indicate that RxData[7:0] and RxSOC will be sampled at the end of the next cycle. In multiple PHY configurations, RxEnb* is used to tri-state RxData and RxSOC MT90220 outputs. In that case, RxData and RxSOC would be enabled only in cycles following those with RxEnb asserted.                                                                                    |

| 203                                  | RxClav          | 0     | UTOPIA Receive Cell Available Indication Signal. For cell-level flow control in a MPHY environment, RxClav is an active high tri-stateable signal from the MT90220 to ATM LAYER device. A polled MT90220 drives RxClav only during each cycle following one with its address on the TxAddr lines. The polled MT90220 asserts RxClav high to indicate it has a complete cell available for transfer to the ATM Layer device, otherwise it de-asserts the signal. |

## **Pin Description (continued)**

| 12, 13   [4:0]   select the appropriate MT90220. RxAddf(4] is the MSB. Each MT90220 keeps its address. The value for the Tx and Rx portions of the MT90220 can be different.    Receiver Static Memory Interface Signals (see Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pin#                                                                                                 | Name       | 1/0 | Description                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 188, 189,   191,   191,   192, 195,   196, 197   192, 195,   196, 197   192, 195,   196, 197   192, 195,   196, 197   192, 195,   196, 197   192, 195,   196, 197   192, 195,   196, 197   192, 195,   196, 197   192, 195,   196, 197   192, 193,   192, 193,   193, 194, 195,   193, 196,   193, 196,   193, 196,   193, 194, 195,   193, 196,   193, 196,   193, 196,   193, 196,   193, 194, 195,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196,   193, 196   | 9, 10, 11,<br>12, 13                                                                                 |            | I   | select the appropriate MT90220. RxAddr[4] is the MSB. Each MT90220 keeps its                                                                                                                                                                                                 |

| the external static memory.  Static Memory Address Bus. The signal is used to select an entry in the external static memory.  Static Memory Address Bus. The signal is used to select an entry in the external static memory.  Static Memory Read/Not Write. If low, data is written from the MT90220 to the memory. If high, data is read from the memory to the MT90220.  Static Memory Chip Control Signal.  Processor Interface Signals (see Note 2)    Volume   V |                                                                                                      |            | R   | eceiver Static Memory Interface Signals (see Note 1)                                                                                                                                                                                                                         |

| 164, 165,   16, 169,   170, 171,   172, 175,   176, 177,   178, 179,   182, 183,   184, 185,   186     187                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 190, 191,<br>192, 195,                                                                               |            | I/O |                                                                                                                                                                                                                                                                              |

| memory. If high, data is read from the memory to the MT90220.    198, 199   sr_cs_1, 0   0   Static Memory Chip Control Signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 164, 165,<br>166, 169,<br>170, 171,<br>172, 175,<br>176, 177,<br>178, 179,<br>182, 183,<br>184, 185, | l          | 0   |                                                                                                                                                                                                                                                                              |

| Processor Interface Signals (see Note 2)  44, 45, 46,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 187                                                                                                  | sr_we      | 0   |                                                                                                                                                                                                                                                                              |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 198, 199                                                                                             | sr_cs_1, 0 | 0   | Static Memory Chip Control Signal.                                                                                                                                                                                                                                           |

| local processor.   local processor processor processor to the MT90220.   local processor processor.   local processor.   loca   |                                                                                                      |            |     | Processor Interface Signals (see Note 2)                                                                                                                                                                                                                                     |

| memory positions of the MT90220.    Tocol   To | 44, 45, 46,<br>47, 48, 49,<br>50, 51                                                                 |            | I/O |                                                                                                                                                                                                                                                                              |

| written from the processor to the MT90220. If high, data is read from the MT90220 to the processor.  Processor Not Write (Intel Mode). This is an input signal. If low, data is written from the processor to the MT90220. De-asserting this signal to high will terminate a write access cycle.  1 Output enable Motorola Mode. This is an input signal. This signal should be tied to GND for Motorola timing mode.  Processor Not Read (Intel Mode). This is an input signal. If low, data is read from the MT90220.  39 Up_cs  1 Processor Chip Select. This is an active low input signal. If this signal is high, the MT90220 ignores all other signals on its processor bus. If this signal is low, the MT90220 accepts the signals on its processor bus. De-asserting this signal to high will terminate an access cycle.  67 Up_irq  O Processor Interrupt Request. If this signal is low, the MT90220 signals to the processor that an interrupt condition is pending inside the MT90220. Otherwise no interrupt is pending inside the MT90220. Open drain signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55, 56, 57,<br>58, 59, 60,<br>61, 62, 63,<br>64, 65                                                  |            | I   |                                                                                                                                                                                                                                                                              |

| to GND for Motorola timing mode.  Processor Not Read (Intel Mode). This is an input signal. If low, data is read from the MT90220.  I Processor Chip Select. This is an active low input signal. If this signal is high, the MT90220 ignores all other signals on its processor bus. If this signal is low, the MT90220 accepts the signals on its processor bus. De-asserting this signal to high will terminate an access cycle.  O Processor Interrupt Request. If this signal is low, the MT90220 signals to the processor that an interrupt condition is pending inside the MT90220. Otherwise no interrupt is pending inside the MT90220. Open drain signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41                                                                                                   | <u>or</u>  | I   | written from the processor to the MT90220. If high, data is read from the MT90220 to the processor.  Processor Not Write (Intel Mode). This is an input signal. If low, data is written from the processor to the MT90220. De-asserting this signal to high will terminate a |

| MT90220 ignores all other signals on its processor bus. If this signal is low, the MT90220 accepts the signals on its processor bus. De-asserting this signal to high will terminate an access cycle.  O Processor Interrupt Request. If this signal is low, the MT90220 signals to the processor that an interrupt condition is pending inside the MT90220. Otherwise no interrupt is pending inside the MT90220. Open drain signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40                                                                                                   | or         | I   | to GND for Motorola timing mode. <b>Processor Not Read (Intel Mode).</b> This is an input signal. If low, data is read from                                                                                                                                                  |

| processor that an interrupt condition is pending inside the MT90220. Otherwise no interrupt is pending inside the MT90220. Open drain signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                                                                   | up_cs      | I   | MT90220 ignores all other signals on its processor bus. If this signal is low, the MT90220 accepts the signals on its processor bus. De-asserting this signal to high                                                                                                        |

| PCM Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67                                                                                                   | up_irq     | 0   | processor that an interrupt condition is pending inside the MT90220. Otherwise no                                                                                                                                                                                            |

| PCM Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                      |            |     |                                                                                                                                                                                                                                                                              |

## **Pin Description (continued)**

| Pin#                                            | Name              | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81,88, 90,<br>97,99,107,<br>109,116             | DSTo<br>[7:0]     | 0   | <b>Serial PCM Data Output 7-0</b> . A 1.544 Mbit/s or 2.048 Mbps serial stream which contain 24 (T1) or 32 (E1) PCM or data channels received on T1 or E1 line. The output is set to high impedance for unused channels and if the link is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 118, 124,<br>127, 134,<br>136, 143,<br>145, 151 | DSTi<br>[7:0]     | I   | <b>Serial PCM Data Input 7-0</b> . A 1.544 Mbit/s or 2.048 Mbps serial stream which contains the 24 (T1) or 32 (E1) PCM or data channels on T1 or E1 line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 83, 85, 92,<br>94, 101,<br>103, 111,<br>113     | TXCKi/o<br>[7:0]  | I/O | PCM Interface Transmit Clock 7-0. This pin is an input for PCM Modes 2, 4, 5 and 7. It is an output for Interface Modes 1, 3, 6 and 8 (see Section 4.2, PCM System Interface Modes). It is the clock for serial PCM data transmission of the T1 and E1 framers. The TXCK source is software selectable and can be either one of the eight RXCK or one of the four REFCK signals. It is used for internal transmit timing and should be connected to the Transmit Clock of the framer.  1. The TXCK is 4.096 MHz for ST-BUS applications.  2. For generic PCM Interfaces (non ST-BUS or asynchronous line termination), these outputs can be programmed to provide either a 1.544 MHz (T1) or 2.048 MHz (T1 or E1) clock.                                                                                                                                                                       |

| 80, 87, 89,<br>96, 98,<br>106, 108,<br>115      | TXSYNCio<br>[7:0] | I/O | Transmit Line 8KHz Frame Pulse 7-0. This pin is an input for Interface Modes 2, 4, 5 and 7. It is an output for Interface Modes 1, 3, 6 and 8 (see PCM Section 4.2, PCM System Interface Modes). It is the 8 kHz reference used as transmit synchronization for the PCM system interface. When an output, the TXSYNC is generated from the TXCK signal and is independent from other TXSYNC signals. Two output modes can be programmed: 1. For ST-BUS applications, it is a low going pulse (F0), that delimits the 32 channel frame of the ST-BUS interface at DSTi and DSTo lines (see Figure 25 - ST-BUS Timing Diagram for this sync pulse). The frame pulse is typically received through the RXSYNC[0] pin.  2. For generic PCM Interfaces, it can be programmed to generate either a positive or negative pulse polarity that lines up with the first bit of the PCM system interface. |

| 117, 125,<br>126, 133,<br>135, 142,<br>144, 150 | RXSYNCi<br>[7:0]  | ı   | Receive line 8KHz Frame Pulse 7-0. This signal represents the 8 KHz reference received from the incoming T1 or E1 line. The MT90220 can be programmed to accept different 8 KHz pulse formats at this input.  1. For ST-BUS applications, it is a low going pulse (F0), which delimits the 32 channel frame of ST-BUS interface at DSTi and DSTo lines. See STBUS timing diagram for this sync pulse.  2. For generic PCM Interfaces, it can be programmed to accept either positive or negative pulse polarities.                                                                                                                                                                                                                                                                                                                                                                             |

| 120, 122,<br>129, 131,<br>138, 140,<br>146, 148 | RXCKi<br>[7:0]    | I   | PCM Interface Receive Clock 7-0. This input line represents the clock for the receive serial PCM data of the T1 and E1 framers. The T1 or E1 frequency value to be received at this input clock is defined by the user through an internal register.  1. For ST-BUS applications, input pin RXCKi receives the 4.096 MHz signal.  2. For generic PCM Interfaces, these inputs can be programmed to accept either a 1.544 MHz (T1) or 2.048 MHz (T1 or E1) clock.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 154, 155                                        | PLLREF<br>[1:0]   | 0   | Output reference to an external PLL. See 4.3 Description of the PCM Interface for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |