# Active Errata List

- Limitation to the operating conditions inside a timing and data marginal configuration

- Reading Errors

- Empty Flag Parasitic Pulse

# **Errata History**

| Lot Number                                 | Errata List |  |

|--------------------------------------------|-------------|--|

| M67206F, M672061F, M67204F all lot numbers | 1, 2, 3     |  |

# **Errata Description**

1. Limitation to the operating conditions inside a timing and data marginal configuration.

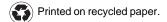

Rising edge of READ from 0 ns up to 8 ns (typical) before the falling edge of WRITE when only one data is left to read.

See Figure 1 for behavior description.

# Failure Mode:

Empty flag glitch and following data shift out 2nd byte corruption occurs when the rising edge of the first "READ" for data shift out occurs before falling edge of the third "WRITE" for data shift in.

# Worst Case Range:

between 0 ns and 11 ns Temperature = 125°C Voltage = 4.5V Characterization: -55°C / 5.5V: 6 ns 25°C / 5V: 8 ns 125°C / 4.5V: 11 ns

#### Workaround

These FIFOs are functional outside of the above timing and data marginal configuration.

The recommended action is to avoid this particular configuration.

Please contact Atmel for a case by case application conditions analysis.

# Radiation Tolerant FIFOs

M67206F M672061F M67204F Errata Sheet

#### Figure 1. Behavior Description

# 2. Reading errors.

#### Description

Sometimes a bit that has been written "1" is read "0".

#### **Failure Conditions**

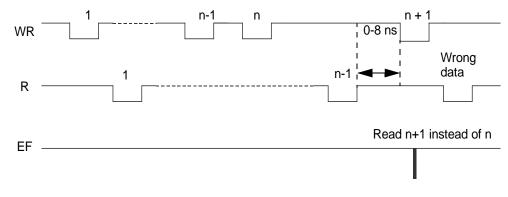

- 1. Read and write commands fall down almost at the same time, t<sub>WLRL</sub> parameter in the hereunder table.

- 2. Write bit "0" on input port while a bit "1" is expected on output port.

- 3. Reading the  $64^{th}+1_{(mod 64)}$  location ( $16^{th}+1_{(mod 16)}$  for 4Kx9 FIFO) vs. the writing location.

- 4. Read pulse (t<sub>RLRH</sub>) less than the one specified in the hereunder table.

#### **Root Cause**

The memory array of the 16Kx9 FIFO contains 64 columns, the 4Kx9 contains 16 columns. To reduce the read access time, a pipe line has been implemented on the data path. When the data<sub>n</sub> is going out of the FIFO, the data<sub>n+1</sub> is prefetched for the next read access. When the internal writing and reading are different from 64  $_{(mod 64)}$  (16  $_{(mod 16)}$ ), a write and a read access are made on the same column. Coupling between the read bit-line and the write bit-line only disturbs the pre-fetch operation, forcing the sense amplifier to output "0". Then, the next external reading may be wrong.

#### Characterization

Worst case condition: 125°C / 4.5V

|                     | <b>t</b> <sub>WLRL</sub> |         | •                        |

|---------------------|--------------------------|---------|--------------------------|

|                     | minimum                  | maximum | <b>t</b> <sub>RLRH</sub> |

| 67206H /<br>672061H | $\ge 0$ ns               | ≤ 8 ns  | ≤ 30 ns                  |

| 67204H              | ≥ -2 ns                  | ≤ 8 ns  | ≤ 25 ns                  |

# Workaround

The workaround depends of the available ways to implement it. One of these workarounds is available:

- 1. No read sequence while write sequence.

- 2. Control the gap between the read and write locations

- 3. Control the  $t_{WLRL}$  parameter in accordance with the above table.

- 4. Apply a read pulse t<sub>RLRH</sub> greater than the value given in the above table.

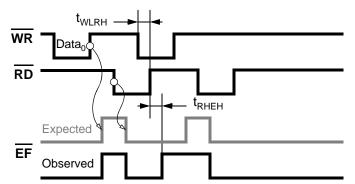

# 3. Empty Flag Parasitic Pulse.

# Description

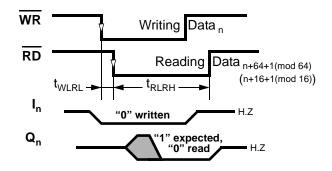

A parasitic positive pulse can be obseved during a FIFO write if it is applied during the read of first data of the FIFO buffer (c.f. hereunder chronograms).

# Side Effect

No side effect on flags computation, internal FIFO control and data integrity.

# Behavior

1. WR wide pulse width:

2. WR short pulse width:

In this case, the falling edge of the parasitic pulse is masked by the beginning of the regular hight level of  $\overline{\mathsf{EF}}$  flag.

# Root Cause

Un-controlled delays on input signals of a flags logic decoder generate an internal glitch. This glitch is re-formatted by the on-chip ETD system (Edge Transition Detection) and a parasitic pulse is output on EF pin.

#### Work Around

Any of the following workarounds can be used:

- 1. No write sequence while read sequence.

- 2.  $\overline{\mathsf{EF}}$  evaluation according to the following characterization.

# Characterization

$\bullet$  Un-functionning window - t  $_{\rm WLRH}$ :

|                   | from | up to | Condition       |

|-------------------|------|-------|-----------------|

| t <sub>WLRH</sub> | 0 ns | 10 ns | Vcc min, +125°C |

|                   | 0 ns | 6 ns  | Vcc Max, -55°C  |

$\bullet$  Parasitic pulse delay - t  $_{\rm RHEH}$ :

|                   | delay | Condition       |

|-------------------|-------|-----------------|

| +                 | 15 ns | Vcc min, +125°C |

| <sup>L</sup> RHEH | 8 ns  | Vcc Max, -55°C  |

$\bullet$  Parasitic pulse width- t  $_{\rm pulse}$ :

|                    | width | Comment |

|--------------------|-------|---------|

| t <sub>pulse</sub> | 20 ns | Maximum |

# **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

# **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### **Microcontrollers**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

© Atmel Corporation 2006. All rights reserved. Atmel<sup>®</sup> and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be the trademarks of others.