# SP8503, SP8505, SP8510

## 12-Bit Sampling A/D Converters

- 3μs, 5μs or 10μs Sample/Conversion Time

- Standard ±10V and ±5V Input

- No Missing Codes Over Temperature

- AC Performance Over Temperature 71.5dB Signal-to-Noise Ratio at Nyquist 85dB Spurious-free Dynamic Range at 49kHz

- -81dB Total Harmonic Distortion at 49kHz

- Internal Sample/Hold, Reference, Clock, and 3-State Outputs

- Low Power Dissipation: 90mW

- 28–Pin Narrow PDIP and SOIC

#### DESCRIPTION...

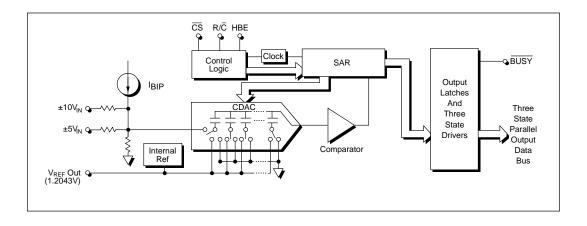

The **SP85XX Series** are complete 12-bit sampling A/D converters using state–of–the–art CMOS structures. They contain a complete 12–bit successive approximation A/D converter with internal sample/hold, reference, clock, digital interface for microprocessor control, and three–state output drivers. Power dissipation is only 90mW. AC and DC performance are completely specified. Sampling/conversion rates of  $3\mu$ s,  $5\mu$ s and  $10\mu$ s are offered.

#### **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these or any other above those indicated in the operation actives of an expectation below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| V <sub>s</sub> to Digital Common                       | +7V                           |

|--------------------------------------------------------|-------------------------------|

| Pin 26 (V <sub>so</sub> ) to Pin 27 (V <sub>sa</sub> ) | ±0.3V                         |

| Analog Common to Digital Common                        | ±0.3V                         |

| Control Inputs to Digital Common                       | 0.3 to V <sub>s</sub> + 0.3 V |

| Analog Input Voltage                                   | ±16.5V                        |

| Maximum Junction Temperature                           | 160°C                         |

| Internal Power Dissipation                             | 750mW                         |

|                                                        |                               |

| Lead Temperature (soldering, 10 | s) +300°C |

|---------------------------------|-----------|

| Thermal Resistance. Ø IA:       |           |

| Plastic DIP                     | 50°C/W    |

| SOIC                            | 100°C/M   |

CAUTION: ESD (ElectroStatic Discharge) sensitive device. Permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. Personnel should be properly grounded prior to handling this device. The protective foam should be discharged to the destination socket before devices are removed.

#### **SPECIFICATIONS**

(T<sub>a</sub> = 25°C; Sampling Frequency, F<sub>s</sub>, = 333kHz for SP8503, 200kHz for SP8505, 100kHz for SP8510, V<sub>s</sub> = +5V, unless otherwise specified.)

| PARAMETER                            | MIN.   | TYP.      | MAX.   | UNITS    | CONDITIONS                                                     |

|--------------------------------------|--------|-----------|--------|----------|----------------------------------------------------------------|

| ANALOG INPUT                         |        |           |        |          |                                                                |

| Voltage Ranges                       |        | ±10V/±5V  | /      | V        |                                                                |

| Impedance                            |        |           |        |          |                                                                |

| ±10V Range                           | 4.7    | 6.7       | 8.7    | kΩ       | $T_{MIN} \le T_A \le T_{MAX}$                                  |

| ±5V Range                            | 2.7    | 3.9       | 5.1    | kΩ       | $T_{MIN} \le T_A \le T_{MAX}$                                  |

| DC PERFORMANCE                       |        |           |        |          |                                                                |

| Full Scale Error                     |        |           |        |          | Externally adjustable to zero;                                 |

| –K                                   |        | ±0.1      | ±0.50  | %        | T <sub>MIN</sub> ≤ T <sub>A</sub> ≤ T <sub>MAX</sub><br>Note 1 |

| Integral Linearity Error             |        |           |        |          | Note 1                                                         |

| –K                                   |        | ±0.35     | ±0.75  | LSB      |                                                                |

| Differential Linearity Error         |        |           |        |          |                                                                |

| –K                                   |        | ±0.35     | ±0.95  | LSB      |                                                                |

| No Missing Codes                     |        | Guarantee | d      |          |                                                                |

| Bipolar Zero                         |        |           |        |          | Externally adjustable to zero                                  |

| K                                    |        | ±1        | ±5     | LSB      | $T_{MIN} \le T_A \le T_{MAX}$                                  |

| VOLTAGE REFERENCE                    |        |           |        |          |                                                                |

| Voltage Output                       | 1.1440 | 1.2043    | 1.2645 | V        |                                                                |

| Output Source Current                |        | 100       |        | μΑ       |                                                                |

| Output Resistance                    |        | 280       |        | Ω        |                                                                |

| AC PERFORMANCE                       |        |           |        |          | $T_{MIN} \le T_A \le T_{MAX}$                                  |

| SP8503                               |        |           |        |          |                                                                |

| Conversion Time                      |        | 2.6       |        | μs       |                                                                |

| Complete Cycle                       | 3.0    |           |        | μs       |                                                                |

| Throughput Rate                      |        |           | 333    | kHz      |                                                                |

| Spurious-Free Dynamic Range          |        |           |        |          | Note 2                                                         |

| @ 49kHz                              |        | 85        |        | dB       |                                                                |

| @ 161kHz                             |        | 72        |        | dB       | Note 0                                                         |

| Total Harmonic Distortion<br>@ 49kHz |        | 81        |        | dB       | Note 2                                                         |

| @ 161kHz                             |        | -71       |        | dB       |                                                                |

| Signal to Noise Ratio (SNR)          |        |           |        | üD       | Note 2                                                         |

| @ 49kHz                              |        | 71.5      |        | dB       |                                                                |

| @ 161kHz                             |        | 71.5      |        | dB       |                                                                |

| Signal to (Noise + Distortion) Ra    | atio   | _         |        |          | Note 2                                                         |

| ّ@ 49kHz                             |        | 71        |        | dB       |                                                                |

| @ 161kHz                             |        | 68        |        | dB       |                                                                |

| SP8505                               |        |           |        |          |                                                                |

| Conversion Time                      | _      | 4.5       |        | μs       |                                                                |

| Complete Cycle                       | 5.0    |           |        | μs       |                                                                |

| Throughput Rate                      |        |           | 200    | kHz      | Nata O                                                         |

| Spurious-Free Dynamic Range          |        | 05        |        | دا ت     | Note 2                                                         |

| @ 49kHz<br>@ 97kHz                   |        | 85<br>77  |        | dB<br>dB |                                                                |

|                                      |        | 11        |        | ub       |                                                                |

|                                      |        |           |        |          |                                                                |

|                                      |        |           |        |          |                                                                |

#### **SPECIFICATIONS** (continued)

(T = 25°C' Sampling Frequency, F := 333kHz for SP8503, 200kHz for SP8505, 100kHz for SP8510, V<sub>2</sub> = +5V, unless otherwise specified.)

| $T_{A} = 25^{\circ}C$ ; Sampling Frequency, $F_{S}$ , = 333kHz for SP8503, 200kHz for SP8505, 100kHz for SP8510, $V_{S} = +5V$ , unless otherwise specified.) |          |              |                       |          |                                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-----------------------|----------|--------------------------------------------------|--|

| PARAMETER                                                                                                                                                     | MIN.     | TYP.         | MAX.                  | UNITS    | CONDITIONS                                       |  |

| AC PERFORMANCE                                                                                                                                                |          |              |                       |          | $T_{MIN} \le T_A \le T_{MAX}$                    |  |

| SP8505                                                                                                                                                        |          |              |                       |          |                                                  |  |

| Total Harmonic Distortion                                                                                                                                     |          |              |                       |          | Note 2                                           |  |

| @ 49kHz                                                                                                                                                       |          | -81          |                       | dB       |                                                  |  |

| @ 97kHz                                                                                                                                                       |          | -76          |                       | dB       |                                                  |  |

| Signal to Noise Ratio (SNR)                                                                                                                                   |          |              |                       |          | Note 2                                           |  |

| @ 49kHz                                                                                                                                                       |          | 71.5         |                       | dB       |                                                  |  |

| @ 97kHz                                                                                                                                                       |          | 71.5         |                       | dB       |                                                  |  |

| Signal to (Noise + Distortion) Ra                                                                                                                             | atio     |              |                       |          | Note 2                                           |  |

| @ 49kHz                                                                                                                                                       |          | 71           |                       | dB       |                                                  |  |

| @ 97kHz                                                                                                                                                       |          | 70           |                       | dB       |                                                  |  |

| SP8510                                                                                                                                                        |          |              |                       |          |                                                  |  |

| Conversion Time                                                                                                                                               | 40.0     | 9.5          |                       | μs       |                                                  |  |

| Complete Cycle                                                                                                                                                | 10.0     |              | 400                   | μs       |                                                  |  |

| Throughput Rate                                                                                                                                               |          | 05           | 100                   | kHz      | @ 40kl In: Nata 2                                |  |

| Spurious-Free Dynamic Range<br>Total Harmonic Distortion                                                                                                      |          | 85<br>81     |                       | dB<br>dB | @ 49kHz; Note 2<br>@ 49kHz; Note 2               |  |

| Signal to Noise Ratio (SNR)                                                                                                                                   |          | 71.5         |                       | dB       | @ 49kHz; Note 2                                  |  |

| Signal to (Noise + Distortion) Ra                                                                                                                             | atio     | 71.5         |                       | dB       | @ 49kHz; Note 2                                  |  |

|                                                                                                                                                               |          |              |                       | ub l     | @ 49KHZ, NOIC 2                                  |  |

| SAMPLING DYNAMICS                                                                                                                                             |          |              |                       |          |                                                  |  |

| Aperture Delay                                                                                                                                                |          | 13           |                       | ns       |                                                  |  |

| Aperture Jitter                                                                                                                                               |          | 150          |                       | ps, rms  |                                                  |  |

| Transient Response                                                                                                                                            |          | 100          |                       | p3, 1113 | Note 3                                           |  |

| -K                                                                                                                                                            |          | 150          |                       | ns       |                                                  |  |

| Overvoltage Recovery                                                                                                                                          |          | 150          |                       | ns       | Note 4                                           |  |

| DIGITAL INPUTS                                                                                                                                                |          |              |                       |          |                                                  |  |

| Logic Levels                                                                                                                                                  |          |              |                       |          |                                                  |  |

| V <sub>IL</sub>                                                                                                                                               | -0.3     |              | +0.8                  | V        |                                                  |  |

| VIH                                                                                                                                                           | +2.4     |              | +5.3                  | v        |                                                  |  |

|                                                                                                                                                               |          | ±0.1         | ±50                   | μA       |                                                  |  |

|                                                                                                                                                               |          |              | ±5                    | μA       |                                                  |  |

| DIGITAL OUTPUTS                                                                                                                                               |          |              |                       |          |                                                  |  |

| Resolution                                                                                                                                                    | 12       |              |                       | Bits     |                                                  |  |

| Data Format                                                                                                                                                   | Para     | llel; 12-bit | or 8-bit/4-           | bit      |                                                  |  |

| Data Coding                                                                                                                                                   | C        | ffset Bina   | ry                    |          |                                                  |  |

| V <sub>OL</sub>                                                                                                                                               | 0.0      |              | +0.4                  | V        | I <sub>SINK</sub> = 1.6mA                        |  |

| V <sub>OH</sub>                                                                                                                                               | +2.4     |              | V <sub>DD</sub><br>±5 | V        | $I_{\text{SOURCE}}^{\text{SHAR}} = 1.6\text{mA}$ |  |

| LEAKAGE (HIGH-Z State)                                                                                                                                        |          | ±0.1         | ±5                    | μΑ       |                                                  |  |

| POWER SUPPLY REQUIRE                                                                                                                                          |          |              |                       |          |                                                  |  |

| Rated Voltage                                                                                                                                                 | +4.75    | +5.0         | +5.25                 | V        | $V_{S}$ (V <sub>SA</sub> and V <sub>SD</sub> )   |  |

| Current                                                                                                                                                       |          | 18           | 21                    | mA       | I <sub>S</sub>                                   |  |

| Power Consumption                                                                                                                                             |          | 90           |                       | mW       |                                                  |  |

| ENVIRONMENTAL AND MECHANICAL                                                                                                                                  |          |              |                       |          |                                                  |  |

| Specification                                                                                                                                                 |          |              |                       |          |                                                  |  |

| —К                                                                                                                                                            | 0        |              | +70                   | °C       |                                                  |  |

|                                                                                                                                                               | <u> </u> |              |                       |          |                                                  |  |

| Storage                                                                                                                                                       | -65      |              | +150                  | °C       |                                                  |  |

| Package                                                                                                                                                       |          | l            |                       |          |                                                  |  |

| -KN                                                                                                                                                           |          | oin Narrow   |                       |          |                                                  |  |

| –KS                                                                                                                                                           | 2        | 8–pin SOI    | C                     |          |                                                  |  |

| L                                                                                                                                                             |          | i            | I                     | 1        |                                                  |  |

NOTES

- LSB means Least Significant Bit. For **SP85XX Series**, 1LSB = 2.44mV for  $\pm$ 5V range, 1 LSB = 4.88mV for  $\pm$ 10V range. 1.

- 2.

- 3.

- All specifications in dB are referred to a full-scale input, either  $\pm 10V$  or  $\pm 5V$ . For full-scale step input, 12-bit accuracy attained in specified time. Recovers to specified performance in specified time after 2 x F<sub>s</sub> input overvoltage. 4.

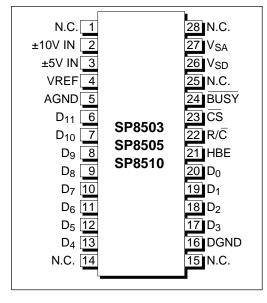

#### PINOUT

#### **PIN ASSIGNMENT**

Pin 1 — No Connection — This pin is not internally connected.

Pin 2 —  $IN_1$  — ±10V Analog Input. Connected to AGND for ±5V range.

Pin 3 —  $IN_2$  —  $\pm 5V$  Analog Input. Connected to AGND for  $\pm 10V$  range.

Pin 4 — V<sub>RFF</sub> – Internal Voltage. Reference Output.

Pin 5 — AGND — Analog Ground. Connect to pin 16 at the device.

Pin 6 —  $D_{11}$  — Data Bit 11. Most Significant Bit (MSB).

Pin 7 —  $D_{10}$  — Data Bit 10.

Pin 8— $D_9$  — Data Bit 9.

$Pin 9 - D_8 - Data Bit 8.$

Pin 10 — D<sub>7</sub> — Data Bit 7 if HBE is LOW; LOW if HBE is HIGH.

Pin 11 —  $D_6$  — Data Bit 6 if HBE is LOW; LOW if HBE is HIGH.

Pin 12 — D<sub>5</sub> — Data Bit 5 if HBE is LOW; LOW if HBE is HIGH.

Pin 13 — D<sub>4</sub> — Data Bit 4 if HBE is LOW; LOW if HBE is HIGH.

Pin 14 - N.C. - This pin is not internally connected.

Pin 15—N.C.—This pin is not internally connected.

Pin 16— DGND — Digital Ground. Connect to pin 5, at the device.

Pin 17 — D<sub>3</sub> — Data Bit 3 if HBE is LOW; Data Bit 11 if HBE is HIGH.

Pin 18 — D<sub>2</sub> — Data Bit 2 if HBE is LOW; Data Bit 10 if HBE is HIGH.

Pin 19—  $D_1$  — Data Bit 1 if HBE is LOW; Data Bit 9 if HBE is HIGH.

Pin 20 —  $D_0$  — Data Bit 0 if HBE is LOW. Least Significant Bit (LSB). Data Bit 8 if HBE is HIGH.

Pin 21 — HBE — High Byte Enable, When held LOW, data output as 12-bits in parallel. When held HIGH, four MSBs presented on pins 17–20, pins 10 - 13 output LOWs. Must be LOW to initiate conversion.

Pin 22— $R/\overline{C}$ —Read/Convert. Falling edge initiates conversion when  $\overline{CS}$  is LOW, HBE is LOW, and BUSY is HIGH.

Pin 23 —  $\overline{\text{CS}}$  —  $\overline{\text{Chip Select}}$ . Outputs in Hi-Z state when HIGH. Must be LOW to initiate conversion or read data.

Pin 24 — BUSY. Output LOW during conversion. Data valid on rising edge in Convert Mode.

Pin 25 — N.C. — This pin is not internally connected.

Pin 26—V<sub>sD</sub>—Positive Digital Power Supply, +5V. Connect to pin 27, and bypass to DGND.

Pin 27 —  $V_{SA}$  — Positive Analog Power Supply. +5V. Connect to pin 26, and bypass to AGND.

Pin 28-N.C. - This pin is not internally connected.

#### FEATURES...

The **SP85XX** Series are specified at sampling rates of 333kHz (**SP8503**), 200kHz (**SP8505**) or 100kHz (**SP8510**). Conversion times are factory set for 2.70 $\mu$ s, 4.7 $\mu$ s and 9.7 $\mu$ s maximum, respectively, over temperature, and the highspeed sampling input stage insures a total acquisition and conversion time of 3 $\mu$ s, 5 $\mu$ s and 10 $\mu$ s maximum, respectively, over temperature. Precision, laser-trimmed scaling resistors provide industry–standard input ranges of ±5V or ±10V.

The 28-pin **SP85XX Series** are available in narrow body plastic DIP, and SOIC packages and it operates from a single +5V supply. The **SP85XX Series** are available in grades specified over the 0°C to +70°C commercial temperature ranges.

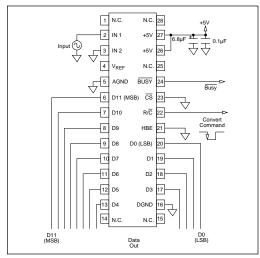

#### OPERATION Basic Operation

*Figure 1* shows the simple hookup circuit required to operate the **SP85XX Series** in a  $\pm 10V$  range in the Convert Mode. A convert command arriving on R/C puts the **SP85XX Series** in the HOLD mode, and a conversion is started. This pulse must be LOW for a minimum of 40ns. Because this pulse establishes the sampling instant of the A/D, it must have very low jitter. BUSY will be held LOW during the conversion, and rises only after the conversion is completed and the data has been transferred to the output drivers. Thus, the rising

Figure 1. Basic ±10V Operation

edge can be used to read the data from the conversion. Also, during conversion, the  $\overline{BUSY}$  signal puts the output data lines in Hi-Z states and inhibits the input lines. This means that pulses on  $R/\overline{C}$  are ignored, so that new conversions cannot be initiated during a conversion, either as a result of spurious signals or to short-cycle the **SP85XX Series.**

In the Read Mode, the input to  $R/\overline{C}$  is kept normally LOW, and a HIGH pulse is used to read data and initiate a conversion. In this mode, the rising edge of  $R/\overline{C}$  will enable the output data pins, and the data from the previous conversion becomes valid. The falling edge then puts the **SP85XX Series** in a hold mode, and initiates a new conversion.

The **SP85XX Series** will begin acquiring a new sample just prior to the  $\overline{\text{BUSY}}$  output rising, and will track the input signal until the next conversion is started.

For use with an 8-bit bus, the data can be readout in two bytes under the control of HBE. With a LOW input on HBE, at the end of a conversion, the 8 LSBs of data are loaded into the output drivers on  $D_7$  through  $D_4$  and  $D_3$  through  $D_0$ . Taking HBE HIGH then loads the 4 MSBs on  $D_3$  through  $D_0$ , with  $D_7$  through  $D_4$  being forced LOW.

#### **Analog Input Ranges**

The **SP85XX Series** offers two standard bipolar input ranges:  $\pm 10V$  and  $\pm 5V$ . If a  $\pm 10V$  range is required, the analog input signal should be connected to pin 2. A signal requiring a  $\pm 5V$  range should be connected to pin 3. In either case, the other pin of the two must be grounded or connected to the adjustment circuits described in the section on calibration.

#### **Controlling The SP85XX Series**

The **SP85XX Series** can be easily interfaced to most microprocessor-based and other digital systems. The microprocessor may take full control of each conversion, or the **SP85XX Series** may operate in a standalone mode, controlled only by the R/ $\overline{C}$  input. Full control consists of initiating the conversion and reading the output data at user command, transmitting data either all 12-bits in one parallel word, or in two 8-bit bytes. The three control inputs ( $\overline{CS}$ , R/ $\overline{C}$  and HBE) are

| CS | R/Ĉ   | HBE | BUSY | OPERATION                                                                                                         |  |

|----|-------|-----|------|-------------------------------------------------------------------------------------------------------------------|--|

| 1  | х     | Х   | 1    | None – outputs in Hi-Z state.                                                                                     |  |

| 0  | 1 ₹ 0 | 0   | 1    | Holds signal and initiates conversion.                                                                            |  |

| 0  | 1     | 0   | 1    | Output three-state buffers enabled once<br>conversion has finished.                                               |  |

| 0  | 1     | 1   | 1    | Enable hi-byte in 8-bit bus mode.                                                                                 |  |

| 0  | 1 ₹ 0 | 1   | 1    | Inhibit start of conversion.                                                                                      |  |

| 0  | 0     | 1   | 1    | None – outputs in Hi-Z state.                                                                                     |  |

| x  | x     | Х   | 0    | Conversion in progress. Outputs Hi-Z<br>state. New conversion inhibited until<br>present conversion has finished. |  |

Table 1. Control Line Functions

all TTL/CMOS compatible. The functions of the control lines are shown in *Table 1*.

For stand-alone operation, control of the **SP85XX Series** is accomplished by a single control line connected to R/C. In this mode, CS and HBE are connected to GND. The output data are presented as 12-bit words. The stand-alone mode is used in systems containing dedicated input ports which do not require full bus interface capability.

Conversion is initiated by a HIGH-to-LOW transition on R/ $\overline{C}$ . The three-state data output buffers are enabled when R/ $\overline{C}$  is HIGH and  $\overline{B}USY$  is HIGH. Thus, there are two possible modes of operation: conversion can be initiated with either positive or negative pulses. In either case, the R/ $\overline{C}$  pulse must remain LOW a minimum of 40ns.

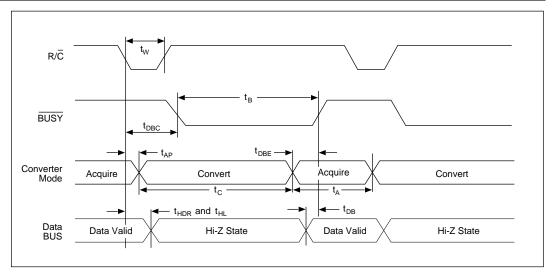

*Figure 5* illustrates timing when conversion is initiated by an  $R/\overline{C}$  pulse which goes LOW and returns HIGH during the conversion. In this case (Convert Mode), the three-state outputs go into the Hi-Z state in response to the falling edge of  $R/\overline{C}$ , and are enabled for external access to the data after completion of the conversion.

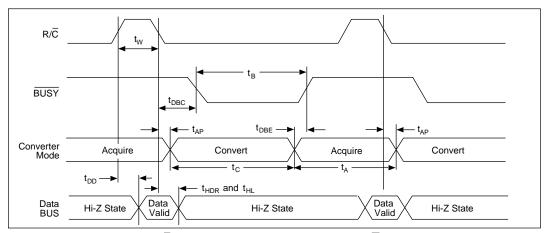

*Figure* 6 illustrates the timing when conversion is initiated by a positive  $R/\overline{C}$  pulse. In this mode (Read Mode), the output data from the previous conversion is enabled during the HIGH portion of  $R/\overline{C}$ . A new conversion starts on the falling edge of  $R/\overline{C}$ , and the three-state outputs return to the Hi-Z state until the next occurrence of a HIGH on  $R/\overline{C}$ .

#### **Conversion Start**

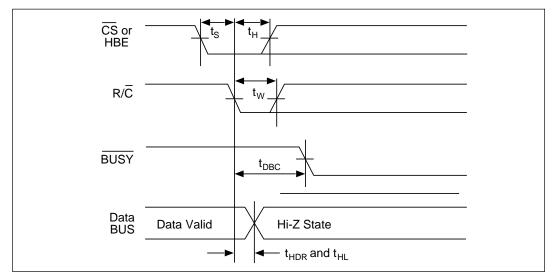

A conversion is initiated on the **SP85XX Series** only by a negative transition occurring on  $R/\overline{C}$ , as shown

in *Table 2*. No other combination of states or transitions will initiate a conversion. Conversion is inhibited if either  $\overline{CS}$  or HBE are HIGH, or if  $\overline{BUSY}$  is LOW.  $\overline{CS}$  and HBE should be stable a minimum of 25ns prior to the transition on  $R/\overline{C}$ . Timing relationships for start of conversion are illustrated in *Figure 7*.

The  $\overline{\text{BUSY}}$  output indicates the current state of the converter by being LOW only during conversion. During this time the three-state output buffers remain in a Hi-Z state, and therefore data cannot be read during conversion. During this period, additional transitions on the three digital inputs ( $\overline{\text{CS}}$ ,  $R/\overline{\text{C}}$  and HBE) will be ignored, so that conversion cannot be prematurely terminated or restarted.

#### Internal Clock

The **SP85XX Series** has an internal clock that is factory trimmed to achieve the typical conversion times given in the specifications, and a maximum conversion time over the full operating temperature range of  $2.7\mu$ s,  $4.7\mu$ s or  $9.7\mu$ s, depending on the model. No external adjustments are required, and with the guaranteed maximum acquisition time of 300ns, throughput performance is assured with convert pulses as close as  $3\mu$ s for the **SP8503**.

### **Reading Data**

After conversion is initiated, the output buffers remain in a Hi-Z state until the following three logic conditions are simultaneously met:  $R/\overline{C}$  is HIGH,  $\overline{BUSY}$  is HIGH and  $\overline{CS}$  is LOW. Upon satisfying these conditions, the data lines are enabled according to the state of HBE. See *Figure 7* for timing relationships and specifications.

## CALIBRATION ...

**Optional External Gain And Offset Trim**

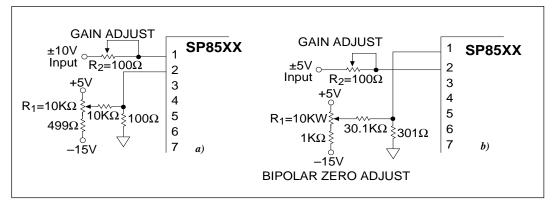

Offset and full-scale errors may be trimmed to zero using external offset and full-scale trim potentiometers connected to the **SP85XX Series** as shown in *Figure 3*.

If adjustment of offset and full scale is not required, connections as shown in *Figure 2* should be used.

Figure 2. a) ±10V Range b) ±5V Range — Without Trims

| INPUT VOLTAGE RANGE AND LSB VALUES |                          |                               |                               |  |  |  |  |

|------------------------------------|--------------------------|-------------------------------|-------------------------------|--|--|--|--|

| Input Voltage Range Defined As:    |                          | ±10V                          | ±5V                           |  |  |  |  |

| Analog Input Connected to Pin      |                          | 2                             | 3                             |  |  |  |  |

| Pin Connected to AGND              |                          | 3                             | 2                             |  |  |  |  |

| One Least Significant Bit (LSB)    | FSR/2 <sup>12</sup>      | 20V/2 <sup>12</sup><br>4.88mV | 10V/2 <sup>12</sup><br>2.44mV |  |  |  |  |

|                                    | OUTPUT TRANSITION VALUES |                               |                               |  |  |  |  |

| FFEH TO FFFH                       | + FULL SCALE             | +10V-3/2LSB                   | +5V-3/2LSB                    |  |  |  |  |

|                                    |                          | +9.9927V                      | +4.9963V                      |  |  |  |  |

| 7FFH TO 800H                       | Mid Scale                | 0V-1/2LSB                     | 0V-1/2LSB                     |  |  |  |  |

|                                    | (Bipolar Zero)           | -2.44mV                       | -1.22mV                       |  |  |  |  |

| 000H to 001H                       | -Full Scale              | -10V+1/2LSB                   | -5V+1/2LSB                    |  |  |  |  |

|                                    |                          | -9.9976V                      | -4.9988V                      |  |  |  |  |

Table 2. Input Voltages, Transition Voltages and LSB Values

#### **Calibration Procedure**

Apply a precision input voltage source to your chosen input range ( $\pm 10V$  range at pin 2 or  $\pm 5V$  at pin 3). Set the A/D to convert continuously. Monitor the output code. Trim the offset first, then gain. Use the appropriate input voltages and output target codes for your chosen input range as follows. The recommended offset calibration voltage values eliminate interaction between the offset and gain calibration

#### ±5V Range Offset and Gain

**Offset** — Apply 1.5637V to the  $\pm$ 5V input at pin 3. Adjust the offset potentiometer until the LSB toggles on and off at code 1010 1000 0000<sub>BIN</sub> = A80<sub>B</sub> = 2688<sub>DEC</sub>.

**Gain** — Apply 4.9963V to the  $\pm$ 5V input at pin 3. Adjust the gain potentiometer until the LSB

toggles on and off at code 1111 1111 1110  $_{\text{BEN}} = \text{FFE}_{\text{H}} = 4094_{\text{DEC}}$ .

#### $\pm$ 10V Range Offset and Gain

**Offset** — Apply 1.2622V to the  $\pm 10V$  input at pin 2. Adjust the offset potentiometer until the LSB toggles on and off at code 1001 0000  $0010_{BIN} = 902_{H} = 2306_{DEC}$ .

**Gain** — Apply 9.9927V to the ±10V input at pin 2. Adjust the gain potentiometer until the LSB toggles on and off at code 1111 1111 1110<sub>BIN</sub> =  $FFE_{H} = 4094_{DEC}$ .

#### Layout Considerations

Because of the high resolution and linearity of the **SP85XX Series**, system design problems such as ground path resistance and contact resistance become very important.

Figure 3. a) ±10V Range b) ±5V Range — With External Trims

The input resistance of the **SP85XX Series** is  $6.3k\Omega$  or  $4.2K\Omega$  (for the ±10V and ±5V ranges respectively). To avoid introducing distortion, the source resistance must be very low, or constant with signal level. The output impedance provided by most op amps is ideal. Pins 26 Digital Supply Voltage ( $V_{sD}$ ) and 27 Analog Supply Voltage ( $V_{sA}$ ) are brought out to separate pins to maximize accuracy on the chip. They should be connected together as close as possible to the unit. Pin 27 may be slightly more sensitive than pin 26 to supply variations, but to maintain maximum system accuracy, both should be well–isolated from digital supplies with wide load variations.

To limit the effects of digital switching elsewhere in a system on the analog performance of the system, it often makes sense to run a separate +5Vsupply conductor from the supply regulator to any analog components requiring +5V, including the SP85XX Series. If the SP85XX Series traces cannot be separated back to the power supply terminals, and therefore share the same trace as the logic supply currents, then a 10 Ohm isolating resistor should be used between the board supply and pin 24  $(V_{DA})$  and its bypass capacitors, to keep  $V_{DA}$  glitch-free. The  $V_s$  pins (26 and 27) should be connected together and bypassed with a parallel combination of a 6.8µF Tantalum capacitor and a 0.1µF ceramic capacitor located close to the converter to obtain noise-free operation. (See Figure

*1*). Noise on the power supply lines can degrade converter performance, especially noise and spikes from a switching power supply. Appropriate supplies or filters must be used.

The GND pins (5 and 16) are also separated internally, and should be directly connected to a ground plane under the converter. A ground plane is usually the best solution for preserving dynamic performance and reducing noise coupling into sensitive converter circuits. Where any compromises must be made, the common return of the analog input signal should be referenced to pin 5, AGND, on the **SP85XX Series**, which prevents any voltage drops that might occur in the power supply common returns from appearing in series with the input signal.

Coupling between analog input and digital lines should be minimized by careful layout. For instance, if the lines must cross, they should do so at right angles. Parallel analog and digital lines should be separated from each other by a pattern connected to common.

If external full scale and offset potentiometers are used, the potentiometers and related resistors should be located as close to the **SP85XX Series** as possible.

#### "Hot Socket" Precaution

Two separate  $+5V V_s$  pins, 26 and 27, are used to minimize noise caused by digital transients. If one pin is powered and the other is not, the **SP85XX**

| R/C<br>BUSY<br>Converter<br>Mode<br>t <sub>AP</sub><br>Hold Time                    |                                       |                      |                      |                |                            |  |

|-------------------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|----------------|----------------------------|--|

| SYMBOL/PARAMETER                                                                    | SYMBOL/PARAMETER MIN. TYP. MAX. UNITS |                      |                      |                |                            |  |

| $t_{\text{\tiny DEC}} = \overline{\text{BUSY}}$ delay from R/ $\overline{\text{C}}$ |                                       | 80                   | 150                  | ns             |                            |  |

| t <sub>a</sub> BUSY Low                                                             |                                       | 2.5                  | 2.7                  | μs             | SP8503                     |  |

|                                                                                     |                                       | 4.5                  | 4.7                  | μs             | SP8505                     |  |

|                                                                                     |                                       | 9.5                  | 9.7                  | μs             | SP8510                     |  |

| t <sub>AP</sub> Aperture Delay                                                      | t <sub>x</sub> Aperture Delay 13 ns   |                      |                      |                |                            |  |

| $\Delta t_{{}_{\!\!AP}}$ Aperture Jitter                                            |                                       | 150                  |                      | ps, rms        |                            |  |

| $t_{\rm c}$ Conversion Time                                                         |                                       | 2.47<br>4.47<br>9.47 | 2.70<br>4.70<br>9.70 | μs<br>μs<br>μs | SP8503<br>SP8505<br>SP8510 |  |

Figure 4. Acquisition and Conversion Timing

Figure 5. Convert Mode Timing  $- R/\overline{C}$  Pulse LOW, Outputs Enabled After Conversion

**Series** may draw excessive current. In normal operation, this is not a problem because both pins will be soldered together. However, during evaluation, incoming inspection, repair, etc., where the potential of a "Hot Socket" exists, care should be taken to apply power to the **SP85XX Series** only after it has been socketed.

#### Minimizing "Glitches"

Coupling of external transients into an analog-todigital converter can cause errors which are difficult to debug. In addition to the discussions earlier on layout considerations for supplies, bypassing and grounding, there are several other useful steps that can be taken to get the best analog performance out of a system using the **SP85XX Series.** These potential system problem sources are particularly important to consider when developing a new system, and looking for the causes of errors in breadboards.

First, care should be taken to avoid glitches during critical times in the sampling and conversion process. Since the **SP85XX Series** has an internal sample/hold function, the signal that puts it into the hold state ( $R/\overline{C}$  going LOW) is critical, as it would be on any sample/hold amplifier. The  $R/\overline{C}$  falling edge should have a 5 to 10ns transition time, low jitter, and have minimal ringing, especially during the 20ns after it falls.

Figure 6. Read Mode Timing —  $R/\overline{C}$  Pulse HIGH, Outputs Enabled Only When  $R/\overline{C}$  is High

#### AC DYNAMIC TIMING DATA

| SYMBO                           | DL/PARAMETER                                                                  | MIN . | TYP. | MAX. | UNITS   |

|---------------------------------|-------------------------------------------------------------------------------|-------|------|------|---------|

| t <sub>w</sub>                  | $R/\overline{C}$ Pulse Width                                                  | 40    |      |      | ns      |

| t <sub>DBC</sub>                | BUSY delay from R/C                                                           |       | 80   | 150  | ns      |

| t <sub>B</sub>                  | BUSY LOW                                                                      |       | 2.47 | 2.7  | μs      |

| t <sub>AP</sub>                 | Aperture Delay                                                                |       | 13   |      | ns      |

| $\Delta t_{AP}$                 | Aperture Jitter                                                               |       | 150  |      | ps, rms |

| t <sub>c</sub>                  | Conversion Time                                                               |       | 2.5  | 2.70 | μs      |

| t <sub>DBE</sub>                | BUSY from End of Conversion                                                   |       | 100  |      | ns      |

| t <sub>DB</sub>                 | BUSY Delay after Data Valid                                                   | 25    | 75   | 200  | ns      |

| t <sub>A</sub>                  | Acquisition Time                                                              |       | 130  | 300  | ns      |

| t <sub>A</sub> + t <sub>C</sub> | Throughput Time                                                               |       |      |      |         |

|                                 | SP8503                                                                        |       |      |      | μs      |

|                                 | SP8505                                                                        | 5.0   |      |      | μs      |

|                                 | SP8510                                                                        | 10.0  |      |      | μs      |

| t <sub>HDR</sub>                | Valid Data Held After $R/\overline{C}$ LOW                                    | 20    | 50   |      | ns      |

| t <sub>s</sub>                  | $\overline{\text{CS}}$ or HBE LOW before R/ $\overline{\text{C}}$ Falls       | 25    | 5    |      | ns      |

| t <sub>H</sub>                  | CS or HBE LOW after R/C Falls                                                 | 25    | 0    |      | ns      |

| t <sub>DD</sub>                 | $t_{pp}$ Data Valid from $\overline{CS}$ LOW, R/ $\overline{C}$ HIGH, and HBE |       | 65   | 150  | ns      |

|                                 | in Desired State (Load = 100pF)                                               |       |      |      |         |

| t <sub>HL</sub>                 | Delay to Hi-Z State after R/C Falls or                                        |       | 50   | 150  | ns      |

|                                 | $\overline{CS}$ Rises (3K $\Omega$ Pullup or Pulldown                         |       |      |      |         |

| All para                        | meters Guaranteed By Design.                                                  |       |      |      |         |

Although not normally required, it is also good practice to avoid glitches from coupling to the **SP85XX Series** while bit decisions are being made. Since the above discussion calls for a fast, clean rise and fall on  $R/\overline{C}$ , it makes sense to keep the rising edge of the convert pulse outside the time when bit decisions are being made. In other words, the convert pulse should either be short (under 100ns so that it transitions before the MSB decision), or relatively long (over 2.75µs to transition after the LSB decision).

Next, although the data outputs are forced into a Hi-Z state during conversion, fast bus transients can still be capacitively coupled into the **SP85XX Series.** If the data bus experiences fast transients during conversion, these transients can be attenuated by adding a logic buffer to the data outputs. The BUSY output can be used to enable the buffer.

Naturally, transients on the analog input signal are to be avoided, especially at times within  $\pm 20$ ns of R/ $\overline{C}$  going LOW, when they may be trapped as part of the charge on the capacitor array. This requires careful layout of the circuit in front of the **SP85XX Series**.

Finally, in multiplexed systems, the timing relative to when the multiplexer is switched may affect the analog performance of the system. In most applications, the multiplexer can be switched as soon as  $R/\overline{C}$  goes LOW (with appropriate delays), but this may affect the conversion if the switched signal shows glitches or significant ringing at the **SP85XX Series** input. Whenever possible, it is safer to wait until the conversion is completed before switching and multiplexer. The extremely fast acquisition time and conversion time of the **SP85XX Series** make this practical in many applications.

Figure 7. Conversion Start Timing

| ORDERING INFORMATION |            |         |  |  |

|----------------------|------------|---------|--|--|

| 0°C to +70°C         |            |         |  |  |

| Model                | Throughput | Package |  |  |

| SP8503KN             |            |         |  |  |

| SP8503KS             |            |         |  |  |

|                      |            |         |  |  |

| SP8505KS             |            |         |  |  |

| SP8510KN             | 100kHz     |         |  |  |

| SP8510KS             | 100kHz     |         |  |  |

|                      |            |         |  |  |

THIS PAGE LEFT INTENTIONALLY BLANK