3

# **MOTOROLA** SEMICONDUCTOR • **TECHNICAL DATA**

# Designer's Data Sheet

# **Power Field Effect Transistor N-Channel Enhancement-Mode** Silicon Gate

This Logic Level TMOS Power FET is designed for high speed power switching applications such as switching regulators, converters, solenoid and relay drivers.

- Low Drive Requirement to Interface Power Loads to Logic Level ICs or Microprocessors — V<sub>GS(th)</sub> = 2 Volts max

- Silicon Gate for Fast Switching Speeds Switching Times Specified at 100°C

- Designer's Data IDSS, VDS(on), VGS(th) and SOA Specified at Elevated Temperature

- Rugged SOA is Power Dissipation Limited

- Source-to-Drain Diode Characterized for Use With Inductive Loads

# MTP15N05EL

**Motorola Preferred Device**

**TMOS POWER FET LOGIC LEVEL** 15 AMPERES  $R_{DS(on)} = 0.1 \text{ OHM}$ 50 VOLTS

#### **MAXIMUM RATINGS**

| Rating                                                                     | Symbol                              | Value        | Unit          |

|----------------------------------------------------------------------------|-------------------------------------|--------------|---------------|

| Drain-Source Voltage                                                       | V <sub>DSS</sub>                    | 50           | Vdc           |

| Drain-Gate Voltage (R <sub>GS</sub> = 1 MΩ)                                | V <sub>DGR</sub>                    | 50           | Vdc           |

| Gate-Source Voltage<br>Continuous<br>Non-repetitive ( $t_p \le 50 \mu s$ ) | V <sub>GS</sub><br>V <sub>GSM</sub> | ± 15<br>± 20 | Vdc<br>Vpk    |

| Drain Current — Continuous<br>— Pulsed                                     | IDM IDM                             | 15<br>40     | Adc           |

| Total Power Dissipation @ T <sub>C</sub> = 25°C<br>Derate above 25°C       | PD                                  | 75<br>0.6    | Watts<br>W/°C |

| Operating and Storage Temperature Range                                    | T <sub>J</sub> , T <sub>stg</sub>   | -65 to 150   | °C            |

## THERMAL CHARACTERISTICS

| Thermal Resistance<br>Junction to Case                                     | R <sub>ØJC</sub> | 1.67       | °C/W |  |

|----------------------------------------------------------------------------|------------------|------------|------|--|

| Junction to Ambient MTM15N05L/06L MTP15N05L/06L                            | $R_{\theta JA}$  | 30<br>62.5 |      |  |

| Maximum Lead Temp. for Soldering<br>Purposes, 1/8" from case for 5 seconds | TL               | 260        | °C   |  |

# **ELECTRICAL CHARACTERISTICS** ( $T_C = 25^{\circ}C$ unless otherwise noted)

| Characteristic                                                                                            | Symbol               | Min      | Max     | Unit |

|-----------------------------------------------------------------------------------------------------------|----------------------|----------|---------|------|

| OFF CHARACTERISTICS                                                                                       |                      |          |         |      |

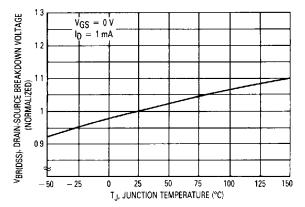

| Drain-Source Breakdown Voltage<br>(VGS = 0, ID = 1 mA) MTM/MTP15N05L<br>MTM/MTP15N06L                     | V <sub>(BR)DSS</sub> | 50<br>60 | _       | Vdc  |

| Zero Gate Voltage Drain Current<br>{VDS = Rated VDSS, VGS = 0}<br>{VDS = Rated VDSS, VGS = 0, TJ = 125°C} | IDSS                 | <u></u>  | 1<br>50 | μAdc |

(continued)

Designer's Data for "Worst Case" Conditions — The Designer's Data Sheet permits the design of most circuits entirely from the information presented SOA Limit curves — representing boundaries on device characteristics — are given to facilitate "worst case" design

Preferred device is a Motorola recommended choice for future use and best overall value.

# **ELECTRICAL CHARACTERISTICS** — continued ( $T_C = 25^{\circ}C$ unless otherwise noted)

| Cha                                                                                       | racteristic                                                             | Symbol              | Min                         | Max      | Unit |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------|-----------------------------|----------|------|

| FF CHARACTERISTICS (continue                                                              | d)                                                                      |                     |                             |          |      |

| Gate-Body Leakage Current, For                                                            | ward ( $V_{GSF} = 15 \text{ Vdc}, V_{DS} = 0$ )                         | IGSSF               | _                           | 100      | nAdc |

| Gate Body Leakage Current, Rev                                                            | verse (V <sub>GSR</sub> = 15 Vdc, V <sub>DS</sub> = 0)                  | IGSSR               | _                           | 100      | nAdc |

| N CHARACTERISTICS                                                                         |                                                                         |                     |                             |          |      |

| Gate Threshold Voltage<br>(VDS = VGS, ID = 1 mA)<br>(TJ = 100°C)                          |                                                                         | VGS(th)             | 1<br>0.75                   | 2<br>1.5 | Vdc  |

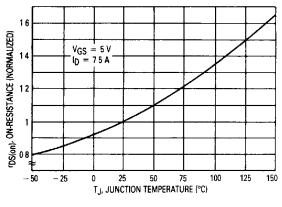

| Static Drain-Source On-Resistan<br>(VGS = 5 Vdc, ID = 7.5 Adc)                            | се                                                                      | R <sub>DS(on)</sub> | _                           | 0.1      | Ohm  |

| Drain-Source On-Voltage (VGS (ID = 15 Adc) (ID = 7.5 Adc, TJ = 100°C)                     | = 5 V)                                                                  | V <sub>DS(on)</sub> | _                           | 3<br>1.5 | Vdc  |

| Forward Transconductance (VD)                                                             | S = 15 V, I <sub>D</sub> = 7.5 A)                                       | 9FS                 | 5                           | -        | mhos |

| YNAMIC CHARACTERISTICS                                                                    |                                                                         |                     |                             |          |      |

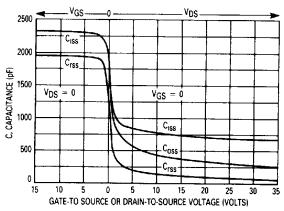

|                                                                                           | V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0, f = 1 MHz                  |                     |                             | 900      | pF   |

| Input Capacitance                                                                         | V <sub>GS</sub> = 15 V, V <sub>DS</sub> = 0, f = 1 MHz<br>See Figure 4  | C <sub>iss</sub>    |                             | 2800     |      |

|                                                                                           | V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0, f = 1 MHz                  |                     | _                           | 200      |      |

| Reverse Transfer Capacitance                                                              | V <sub>GS</sub> = 15 V, V <sub>DS</sub> = 0, f = 1 MHz<br>See Figure 4  | C <sub>rss</sub>    | <del>-</del>                | 2400     | pF   |

| Output Capacitance                                                                        | V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0, f = 1 MHz<br>See Figure 4  | Coss                | _                           | 450      | pF   |

| WITCHING CHARACTERISTICS (                                                                | T <sub>J</sub> = 100°C)                                                 |                     |                             |          |      |

| Turn-On Delay Time                                                                        |                                                                         | td(on)              | _                           | 40       | ns   |

| Rise Time                                                                                 | $(V_{DD} = 25 \text{ V, I}_{D} = 7.5 \text{ A,}$                        | t <sub>r</sub>      | _                           | 260      |      |

| Turn-Off Delay Time                                                                       | V <sub>GS</sub> = 5 V, R <sub>gen</sub> = 50 ohms)                      | td(off)             | _                           | 200      |      |

| Fall Time                                                                                 |                                                                         | tf                  | _                           | 200      |      |

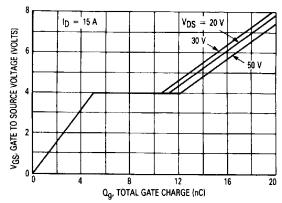

| Total Gate Charge                                                                         | · (V <sub>DS</sub> = 0.8 Rated V <sub>DSS</sub> ,                       | $\alpha_{g}$        | 14 (typ)                    | 22       | nC   |

| Gate-Source Charge                                                                        | I <sub>D</sub> = 15 A, V <sub>GS</sub> = 5 Vdc)                         | Qgs                 | 7 (typ)                     | _        | ]    |

| Gate-Drain Charge                                                                         | See Figures 6 and 10.                                                   | Ogd                 | 7 (typ)                     | _        |      |

| OURCE DRAIN DIODE CHARACT                                                                 | ERISTICS                                                                |                     |                             |          |      |

| Forward On-Voltage                                                                        |                                                                         | V <sub>SD</sub>     | 1.8 (typ)                   |          | Vdc  |

| Forward Turn-On Time                                                                      | (I <sub>S</sub> = Rated I <sub>D</sub> , V <sub>GS</sub> = 0)           | ton                 | Limited by stray inductance |          |      |

| Reverse Recovery Time                                                                     |                                                                         | t <sub>rr</sub>     | 300 (typ)                   |          | ns   |

| TERNAL PACKAGE INDUCTANO                                                                  | CE (TO-220)                                                             |                     |                             |          |      |

| Internal Drain Inductance<br>(Measured from the contact s<br>(Measured from the drain lea | crew on tab to center of die)<br>d 0.25" from package to center of die) | Ld                  | 3.5 (Typ)<br>4.5 (Typ)      | _        | nH   |

| Internal Source Inductance<br>(Measured from the source le<br>source bond pad.)           | ad 0.25" from package to                                                | L <sub>S</sub>      | 7.5 (Typ)                   | _        |      |

# BAE D TYPICAL CHARACTERISTICS

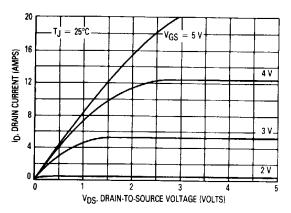

Figure 1. On-Region Characteristics

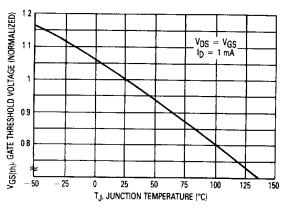

Figure 2. Gate-Threshold Voltage Variation With Temperature

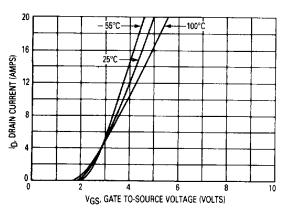

Figure 3. Transfer Characteristics

Figure 4. Capacitance Variation

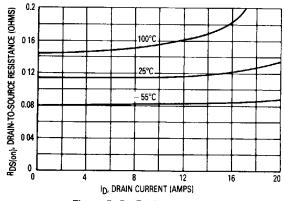

Figure 5. On-Resistance versus **Drain Current**

Figure 6. Gate Charge Variation

Figure 7. On-Resistance Variation with Temperature

Figure 8. Drain-Source Breakdown Voltage Variation with Temperature

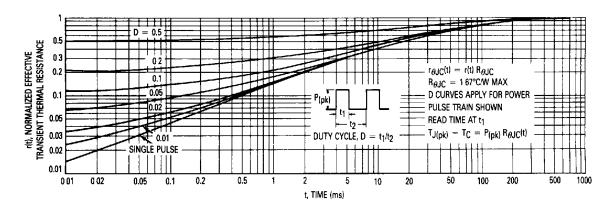

Figure 9. Thermal Response

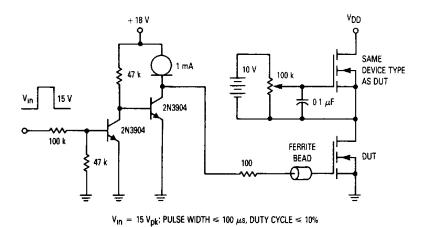

Figure 10. Gate Charge Test Circuit

3

SAFE OPERATING AREA INFORMATION

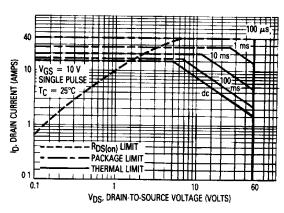

## FORWARD BIASED SAFE OPERATING AREA

The FBSOA curves define the maximum drain-tosource voltage and drain current that a device can safely handle when it is forward biased, or when it is on, or being turned on. Because these curves include the limitations of simultaneous high voltage and high current, up to the rating of the device, they are especially useful to designers of linear systems. The curves are based on a case temperature of 25°C and a maximum junction temperature of 150°C. Limitations for repetitive pulses at various case temperatures can be determined by using the thermal response curves. Motorola Application Note, AN569, "Transient Thermal Resistance-General Data and Its Use" provides detailed instructions.

Figure 11. Maximum Rated Forward **Biased Safe Operating Area**

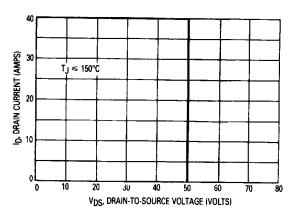

## **SWITCHING SAFE OPERATING AREA**

The switching safe operating area (SOA) of Figure 12 is the boundary that the load line may traverse without incurring damage to the MOSFET. The fundamental limits are the peak current, IDM and the breakdown voltage, V(BR)DSS. The switching SOA shown in Figure 12 is applicable for both turn-on and turn-off of the devices for switching times less than one microsecond.

The power averaged over a complete switching cycle must be less than:

$$\frac{\mathsf{T}_{\mathsf{J}(\mathsf{max})} - \mathsf{T}_{\mathsf{C}}}{\mathsf{R}_{\theta \mathsf{J}\mathsf{C}}}$$

Figure 12. Maximum Rated Switching Safe Operating Area