SANYO

# 4-Bit Single-Chip CMOS Microcontroller for Small-Scale Control Applications

CMOS IC

LC65F1306A

### Preliminary

#### Overview

The LC65F1306A belongs to our 4-bit single-chip microcontroller LC6500 series fabricated using CMOS process technology. They are ideally suited for use in small-scale control applications. Their basic architecture and instruction set are the same. These microcontrollers include an 8-input 8-bit A/D converter and are appropriate for use in a wide range of applications. That range includes applications with a small number of control circuits that were previously implemented in standard logic, and applications with a larger scale such as home appliances, automotive equipment, communications equipment, office equipment, and audio equipment such as decks and players. This microcontroller, with some exceptions, has identical functions to the LC651306A, 1304A, 1302A and 1301A mask ROM version microcontrollers. It can also be used as an OTP version microcontroller. Further, through a rewrite operation on the FLASH memory, the LC65F1306A can be used in applications where previously microcontrollers of this type could not have been implemented.

#### Features

1) CMOS technology for a low-power consumption operation (A standby function that can be invoked under program control is also provided.)

#### 2) Flash ROM/RAM

LC65F1306A Flash ROM :  $6K \times 8$  bits, RAM :  $256 \times 4$  bits

- 3) Instruction set : 81 instructions common to all microcontrollers of the LC6500 series

- 4) Wide operating voltage range : 3.0 V to 5.5 V

- 5) Instruction cycle time :  $0.92 \ \mu s$

- 6) On-chip serial I/O port

Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

| 7) Flexible I/O po            | xet                                                                                                                      |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| · •                           | of ports : 5 ports / 18 pins (max.)                                                                                      |

| All ports                     |                                                                                                                          |

| 1                             | Input / output capacity voltage 15V max. (open-drain specification C and D only)                                         |

|                               | Output current 20 mA max. sink current (Can drive an LED directly)                                                       |

|                               | option for system specification                                                                                          |

| Output le                     | evel in the reset mode : high/low level for port C and D specified in 4-bit unit                                         |

| 8) Interrupt functi           |                                                                                                                          |

|                               | y timer overflow (can be tested under program control)                                                                   |

| -                             | by the state of the $\overline{INT}$ pin or completion of transmission/reception at serial I/O port (can be tested under |

| program c                     | ontrol)                                                                                                                  |

| 9) Stack level :              | 8 levels (common use with interrupt)                                                                                     |

| 10) Timer :                   | 4-bit variable prescaler + 8-bit programmable counter                                                                    |

| 11) Clock oscillat            | ion options for user's intended system                                                                                   |

| <ul> <li>Oscillato</li> </ul> | r circuit options : two-pin RC oscillator                                                                                |

|                               | two-pin ceramic oscillator                                                                                               |

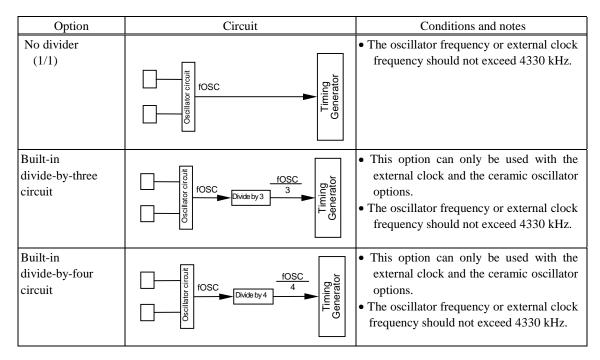

| • Divider o                   | circuit options : No divider                                                                                             |

|                               | built-in divide by 3                                                                                                     |

|                               | built-in divide by 4                                                                                                     |

| 12) Continuous so             | quare wave output (64 times of the cycle time)                                                                           |

| 13) AD converter              | (successive approximation)                                                                                               |

| • Precise c                   | onversion (expressed in 8 bits), 8 input channels                                                                        |

| 14) Watchdog tin              | ner                                                                                                                      |

| • RC circuit                  | t time constant                                                                                                          |

| Watchdo                       | g timer reset function can be assigned to an external pin by the option.                                                 |

| 15) Low voltage of            | letection circuit                                                                                                        |

| • Can be in                   | plemented by the option.                                                                                                 |

| 16) Factory shipn             | nent                                                                                                                     |

| • DIP24S,                     | MFP24S                                                                                                                   |

17) Flash Memory

- Rewrite block size : 128 bytes / page

- Erase / write voltage : 3.0 to 5.5V

- Rewritable limit : 10000 times (target number, to be decided after evaluation)

- Operating temperature : 0 to  $+85^{\circ}C$  (when writing to the flash memory)

-20 to  $+85^{\circ}$ C (when reading from the flash memory)

### **Function Table**

| Parameter       |                         | LC651306A/04A/02A/01A                          | LC65F1306A                                 |  |

|-----------------|-------------------------|------------------------------------------------|--------------------------------------------|--|

| Memory          | ROM                     | 6144 × 8 bits (1306A)<br>4096 × 8 bits (1304A) | 6144 × 8 bits                              |  |

|                 |                         | $2048 \times 8$ bits (1302A)                   |                                            |  |

|                 |                         | $1024 \times 8$ bits (1301A)                   |                                            |  |

|                 | RAM                     | $256 \times 4$ bits                            | $256 \times 4$ bits                        |  |

|                 |                         | (1306A/04A/02A/01A)                            |                                            |  |

| Instructions    | Instruction set         | 81                                             | 81                                         |  |

|                 | Table reference         | Supported                                      | Supported                                  |  |

| On-chip         | Interrupt               | 1 external, 1 internal                         | 1 external, 1 internal                     |  |

| functions       | Timer                   | 4-bit variable prescaler + 8-bit               | 4-bit variable prescaler + 8-bit           |  |

|                 |                         | timers                                         | timers                                     |  |

|                 | Stack level             | 8                                              | 8                                          |  |

|                 | Standby function        | Standby mode by the HALT                       | Standby mode by the HALT                   |  |

|                 |                         | instruction supported                          | instruction supported                      |  |

| I/O ports       | Port number             | 18 I/O port pins                               | 22 I/O port pins                           |  |

|                 | Serial port             | Input and output in 4 or 8 bit                 | Input and output in 4 or 8 bit             |  |

|                 |                         | units                                          | units                                      |  |

|                 | I/O voltage<br>capacity | 15 V max.                                      | 15 V max.                                  |  |

|                 | Output current          | 10 mA typ. 20 mA max.                          | 10 mA typ. 20 mA max.                      |  |

|                 | I/O circuit type        | Open drain (N-channel) or                      | Open drain (N-channel)                     |  |

|                 |                         | pull-up resistor output option                 |                                            |  |

|                 |                         | can be specified in 1- bit unit.               |                                            |  |

|                 | Output level at reset   | High or low level output can be so on          | elected in port unit (ports C and D<br>ly) |  |

|                 | Square wave output      | Supported                                      | Supported                                  |  |

| Characteristics | Minimum cycle<br>time   | $0.92 \ \mu s \ (VDD \ge 2.5 \ V)$             | $0.92 \ \mu s \ (VDD \ge 3.0 \ V)$         |  |

|                 | Operating               | -40°C to +85°C                                 | $0^{\circ}$ C to +85°C (when writing)      |  |

|                 | temperature             |                                                | -20°C to +85°C (when reading)              |  |

|                 | Supply voltage          | 2.5 to 6 V                                     | 3.0 to 5.5 V                               |  |

|                 | Supply current          | 1.5 mA typ.                                    | 3 mA typ.                                  |  |

| Oscillator      | Oscillator              | RC (800 kHz typ.)                              | RC (800 kHz typ.)                          |  |

|                 |                         | Ceramic (400k, 800k,1MHz,                      | Ceramic (400k, 800k,1MHz,                  |  |

|                 |                         | 4MHz)                                          | 4MHz)                                      |  |

|                 | Divider circuit option  | 1/1, 1/3, 1/4                                  | 1/1, 1/3, 1/4                              |  |

| Other items     | Package                 | DIP24S MFP24S SSOP24                           | DIP24S MFP24S                              |  |

|                 | Watchdog timer          | Supported                                      | Supported                                  |  |

|                 | OTP                     | Only DIP24S MFP24S                             | -                                          |  |

Note: The above oscillator and oscillator circuit constants are tentative. They will be announced as the recommended circuits for these microcontrollers are determined. Please confirm the progress of these developments periodically.

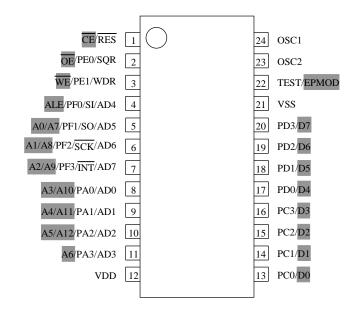

### Pin Assignment

DIP24S, MFP24S

Pin function names used when writing data to on-chip Flash ROM with the PROM writer

#### **Pin Functions**

| $\frac{OSC}{RES}$       | :           | Ceramic Oscillator for OSC, RC<br>Reset                              | TEST<br>AD0-AD7   | :           | Test<br>AD converter analog input                                      |

|-------------------------|-------------|----------------------------------------------------------------------|-------------------|-------------|------------------------------------------------------------------------|

| PA0-3<br>PC0-3<br>PD0-3 | :<br>:<br>: | Common I/O port A0-3<br>Common I/O port C0-3<br>Common I/O port D0-3 | SQR<br>WDR<br>INT | :<br>:<br>: | Square wave output<br>Watch Dog Reset pin<br>Interrupt Request pin     |

| PE0-1<br>PF0-3          | :           | Common I/O port E0-1<br>Common I/O port F0-3                         | SI<br>SO<br>SCK   | :<br>:<br>: | Serial Input pin<br>Serial Output pin<br>Serial Clock input/output pin |

Notes: • SQR and WDR are common with PE0 and PE1 respectively.

• SI, SO,  $\overline{\text{SCK}}$ , and  $\overline{\text{INT}}$  are common with PF0 to PF3 respectively.

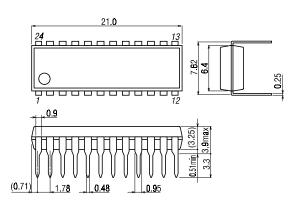

# Package Dimension

(unit : mm) 3067A

SANYO : DIP24S(300mil)

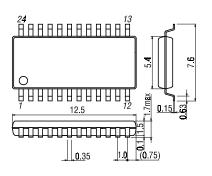

# Package Dimension

(unit : mm) 3112A

SANYO : MFP24S(300mil)

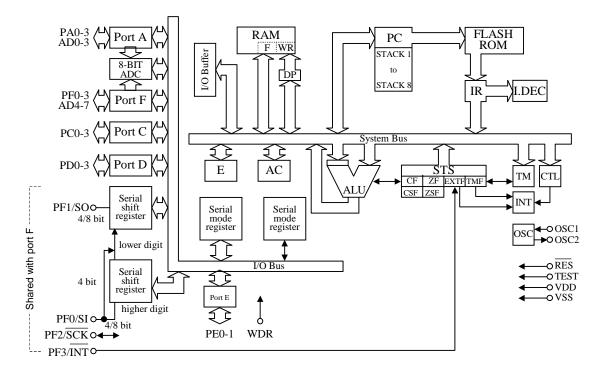

# System Block Diagram

LC65F1306A

| RAM | : | Data Memory               | FLASH ROM | : | Program Memory                  |

|-----|---|---------------------------|-----------|---|---------------------------------|

| F   | : | Flag                      | PC        | : | Program Counter                 |

| WR  | : | Working Register          | INT       | : | Interrupt control               |

| AC  | : | Accumulator               | IR        | : | Instruction Register            |

| ALU | : | Arithmetic and Logic Unit | I.DEC     | : | Instruction Decoder             |

| DP  | : | Data Pointer              | CF, CSF   | : | Carry Flag, Carry Save Flag     |

| E   | : | E register                | ZF, ZSF   | : | Zero Flag, Zero Save Flag       |

| CTL | : | Control register          | EXTF      | : | External Interrupt Request Flag |

| OSC | : | Oscillation Circuit       | TMF       | : | Internal Interrupt Request Flag |

| TM  | : | Timer                     |           |   |                                 |

| STS | : | Status register           |           |   |                                 |

#### **Development Support**

The following are currently in the development stage and will soon be available to the user for the development of the LC65F1306A.

1. User's manual

Refer to the "LC65F1306A/LC651300 series user's manual."

- 2. Development tool manual

- Refer to the "EVA86000 Development Tool Manual for 4-bit microcontrollers."

- Software manual "LC65/66 Series Software Manual"

- 4. Development tool

a. For program development (EVA86000 system)

b. For program evaluation

Microcontroller with Flash ROM (LC65F1306)

### **Pin Functions**

| Symbol              | Number<br>of pins | I/O             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Option                                                                                                                                                                                  | At reset                                                                                                              | Handling when unused                                                   |

|---------------------|-------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| VDD<br>VSS          | 1<br>1            | -               | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                       | -                                                                                                                     | -                                                                      |

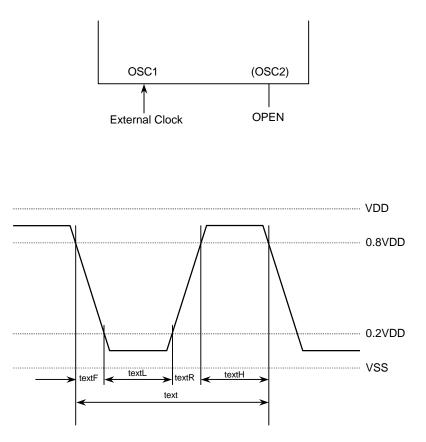

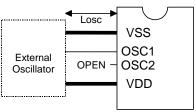

| OSC1<br>OSC2        | 1                 | Input<br>Output | <ul> <li>Pins for connecting system clock<br/>oscillation RC or ceramic resonator.</li> <li>Leave OSC2 open when OSC1 is<br/>used for an external clock input</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     | <ol> <li>Two-pin RC oscillator,<br/>external clock</li> <li>Two-pin ceramic oscillator</li> <li>Divider option</li> </ol>                                                               | -                                                                                                                     | -                                                                      |

|                     |                   |                 | used for an external clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1. No divider<br>2. Divide by 3<br>3. Divide by 4                                                                                                                                       |                                                                                                                       |                                                                        |

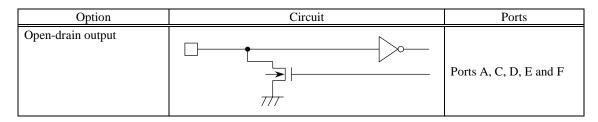

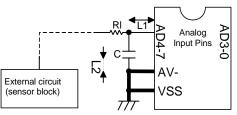

| PA0-PA3/<br>AD0-AD3 | 4                 | ΙΟ              | <ul> <li>I/O port A0 to A3<br/>Input in 4-bit unit (IP instruction)<br/>Output in 4-bit unit<br/>(OP instruction)<br/>Testing in 1-bit unit<br/>(BP, BNP instructions)<br/>Set and reset in 1-bit unit<br/>(SPB, RPB instructions)</li> <li>PA3 is used for standby mode<br/>control.</li> <li>Chattering should not be occurred<br/>on the PA3 during HALT<br/>instruction execution.</li> <li>All four pins have shared<br/>function.<br/>PA0/AD0:AD converter input AD0<br/>PA1/AD1:AD converter input AD1<br/>PA2/AD2:AD converter input AD2<br/>PA3/AD3: converter input AD3</li> </ul> | Open-drain output only                                                                                                                                                                  | High-level<br>output (The<br>output<br>N-channel<br>transistors in<br>the off state.)                                 | Select the<br>open-drain<br>output<br>option and<br>connect to<br>VSS. |

| PC0-PC3             | 4                 | I/O             | <ul> <li>•I/O port C0 to C3<br/>The port functions are identical to<br/>those of PA0 to PA3 (See note).</li> <li>• The output during a reset can be<br/>selected to be either high or low as<br/>an option.</li> <li>Note: This port has no standby<br/>mode control function.</li> </ul>                                                                                                                                                                                                                                                                                                    | <ul> <li>Open-drain output only</li> <li>(1) High level output during reset.</li> <li>(2) Low level output during reset.</li> <li>(1) and (2) are specified 4 bits at a time</li> </ul> | <ul> <li>High-level<br/>output.</li> <li>Low-level<br/>output.<br/>(Depending<br/>on options<br/>selected)</li> </ul> | Same as PA0 to<br>PA3.                                                 |

| PD0-PD3             | 4                 | I/O             | •I/O port D0 to D3<br>The port functions and options are<br>identical to those of PC0 to PC3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Same as PC0 to PC3.                                                                                                                                                                     | Same as PC0 to<br>PC3.                                                                                                | Same as PA0 to<br>PA3.                                                 |

| Symbol                                                                   | Number<br>of pins | I/O   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Option                                                                                                                      | At reset                                                                                                                               | Handling<br>when<br>unused                  |

|--------------------------------------------------------------------------|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| PE0-PE1<br>/WDR                                                          | 2                 | I/O   | <ul> <li>I/O port E0 to E1<br/>Input in 4-bit unit (IP instruction)<br/>Output in 4-bit unit (OP instruction)<br/>Set and reset in 1-bit unit<br/>(SPB and PRB instructions)<br/>Testing in 1-bit unit<br/>(BP and BNP instructions)</li> <li>PE0 also has a continuous pulse (64<br/>Tcyc) output function.</li> <li>PE1 becomes the watchdog reset pin<br/>WDR when selected as an option.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Open -drain output only<br>(1) Normal port PE1<br>(2) Watchdog reset WDR<br>• Either options (1) or<br>(2) can be selected. | High level<br>output (The<br>output<br>N-channel<br>transistors in<br>the off state)                                                   | Identical to<br>those for<br>PA0 to<br>PA3. |

| PF0/SI/A<br>D4<br>PF1/SO/<br>AD5<br>PF2/ SCK<br>/AD6<br>PF3/ INT<br>/AD7 | 4                 | VO    | <ul> <li>I/O port F0 to F3         The port functions and options are identical to those of PE0 to PE1 (See note).     </li> <li>PF0 to PF3 have shared functions with the serial interface pins and the INT input.         The function can be selected under program control.         SL Serial input pin         SOSerial output pin         SCKInput and output of the serial clock signal.         INTInterrupt request signal         The serial I/O function can be switched between 4-bit and 8-bit transfers under program control.         Note: There is no continuous pulse output function.         All four pins have shared function.         PF0/AD4: AD converter input AD4         PF1/AD5: AD converter input AD6         PF3/AD7: AD converter input AD7         Output AD7         Description:         Output AD7         Description:         Descripting:         Description</li></ul> | PA3.                                                                                                                        | Identical to<br>those for PA0<br>to PA3.<br>The serial port<br>functions are<br>disabled.<br>The interrupt<br>source is set to<br>INT. | Identical to<br>those for<br>PA0 to<br>PA3. |

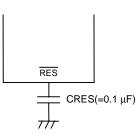

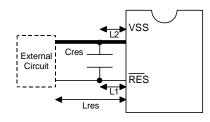

| RES                                                                      | 1                 | Input | <ul> <li>System reset input</li> <li>Provide an external capacitor for the power-on reset.</li> <li>Apply low level to this pin for 4 or more clock cycles to reset and restart the program.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                           | -                                                                                                                                      | -                                           |

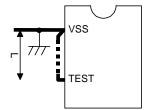

| TEST                                                                     | 1                 | Input | • Test pin for LSI.<br>This pin must be connected to VSS<br>during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                           | -                                                                                                                                      | This pin<br>must be<br>connected<br>to VSS. |

#### **User Option**

User option is selected according to the information written to the user option area on the on-chip Flash ROM.

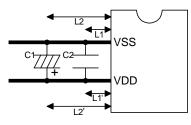

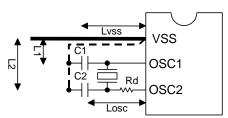

#### **Oscillator Circuit Options**

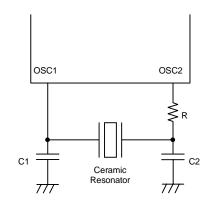

| Option                | Circuit                          | Conditions and notes              |

|-----------------------|----------------------------------|-----------------------------------|

| External clock        |                                  | The OSC2 pin should be left open. |

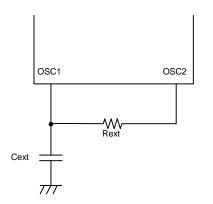

| Two-pin RC oscillator | Cext OSC1                        |                                   |

| Ceramic oscillator    | Ceramic<br>Resonator<br>777 C2 R |                                   |

#### **Divider Circuit Options**

Note: The following table summarizes the oscillator and divider circuit options. When selecting the divider option, the relationship between frequency and cycle time must be taken into account.

# LC65F1306A Oscillator Options

| Circuit type                                                     | Frequency                                                                                                                    | Divider option<br>(Cycle time)                                       | VDD<br>range                        | Notes                                                                |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|

| Ceramic resonator                                                | 400 kHz                                                                                                                      | 1/1 (10µs)                                                           | 3 to 5.5V                           | Can not be used with the divide-by-three and divide-by-four options. |

|                                                                  | 800 kHz                                                                                                                      | 1/1 (5µs)                                                            | 3 to 5.5V                           |                                                                      |

|                                                                  | 1 MHz                                                                                                                        | 1/1 (4µs)                                                            | 3 to 5.5V                           |                                                                      |

|                                                                  | 4 MHz                                                                                                                        | 1/1 (1μs)<br>1/3 (3μs)<br>1/4 (4μs)                                  | 3 to 5.5V<br>3 to 5.5V<br>3 to 5.5V |                                                                      |

| External clock (used<br>with the 2-pin RC<br>oscillator circuit) | 384 k to 4330 kHz<br>1152 k to 4330 kHz<br>1536 k to 4330 kHz                                                                | 1/1 (10.4 to 0.92µs)<br>1/3 (10.4 to 2.77µs)<br>1/4 (10.4 to 3.70µs) | 3 to 5.5V<br>3 to 5.5V<br>3 to 5.5V |                                                                      |

| Two-pin RC                                                       | Use the no divider circui<br>recommended circuit cor<br>other constants by neces<br>and VDD range identica<br>written above. | nstants. When using sity, use the frequency                          | 3 to 5.5V                           | -                                                                    |

| External clock used with<br>the ceramic oscillator<br>option     | External clock drive is n                                                                                                    | ot possible. To use extern                                           | al clock drive, s                   | elect the 2-pin RC oscillator option.                                |

# Port C and D Output level Option During Reset

The Output level of the C and D ports at reset can be selected from the following two options in 4-bit unit.

| Option                     | Conditions and notes        |

|----------------------------|-----------------------------|

| High level output at reset | Ports C and D in 4-bit unit |

| Low level output at reset  | Ports C and D in 4-bit unit |

### Port Output Type

The I/O port type is open-drain output.

#### Watchdog Reset Option

This option allows the user to select how the PE1/WDR pin is to be used. It can be used as the normal port PE1, or used as the watchdog reset pin WDR.

| Parameter                 | Symbol          | Conditions                                                     | Applicable pins<br>and notes                                       | Ratings                                                                        | unit |

|---------------------------|-----------------|----------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------|------|

| Maximum<br>supply voltage | VDD max         |                                                                | VDD                                                                | -0.3 to +6.5                                                                   | V    |

| Output voltage            | VO              |                                                                | OSC2                                                               | Output voltage<br>generated can be<br>over the<br>maximum limit<br>of the VDD. |      |

| Input voltage             | VI (1)          |                                                                | OSC1 (Note 1)                                                      | -0.3 to VDD+0.3                                                                |      |

|                           | VI (2)          |                                                                | TEST, $\overline{\text{RES}}$<br>AV <sub>+</sub> , AV <sub>-</sub> | -0.3 to VDD+0.3                                                                |      |

| I/O voltage               | VIO (1)         | PC0 to 3, PD0 to 3                                             | Open-drain<br>specification<br>ports                               | -0.3 to +15                                                                    |      |

|                           | VIO (2)         | PC0 to 3, PD0 to 3                                             | Pull-up resistor<br>specification<br>ports                         | -0.3 to VDD+0.3                                                                |      |

|                           | VIO (3)         | PA0 to 3, PE0, 1, PF0 to 3                                     |                                                                    | -0.3 to VDD+0.3                                                                |      |

| Peak output current       | IOP             |                                                                | I/O Port                                                           | -2 to +20                                                                      | mA   |

| Average<br>output current | IOA             | Average current applied to a pin for 100 ms                    | I/O Port                                                           | -2 to +20                                                                      |      |

| *                         | $\Sigma$ IOA(1) | The total current of PC0 to 3, PD0 to 3 and PE0 to 1. (Note 2) | PC0 to 3<br>PD0 to 3<br>PE0 to 1                                   | -15 to +100                                                                    |      |

|                           | $\Sigma IOA(2)$ | The total current of PF0 to 3 and PA0 to 3. (Note 2)           | PF0 to 3<br>PA0 to 3                                               | -15 to +100                                                                    |      |

| Maximum                   | Pd max (1)      | Ta=-20 to +85°C (DIP package)                                  |                                                                    | 310                                                                            | mW   |

| power<br>consumption      | Pd max (2)      | Ta=-20 to +85°C (MFP package)                                  |                                                                    | 220                                                                            |      |

| Operating temperature     | Topr            |                                                                |                                                                    | -20 to +85                                                                     | °C   |

| Storage<br>temperature    | Tstg            |                                                                |                                                                    | -55 to +125                                                                    |      |

### 1. Absolute Maximum Ratings at Ta=25°C, VSS=0V

| Parameter                                                        | Symbol          | Conditions                      |                                   | Applicable pins                                                   |               | unit             |                |             |

|------------------------------------------------------------------|-----------------|---------------------------------|-----------------------------------|-------------------------------------------------------------------|---------------|------------------|----------------|-------------|

| Farameter                                                        | Symbol          | Conc                            | intions                           | and notes                                                         | min.          | typ.             | max.           | uiiit       |

| Operating supply voltage                                         | VDD             |                                 |                                   | VDD                                                               | 3.0           |                  | 5.5            | v           |

| Standby supply<br>voltage                                        | VST             | RAM and registe<br>(Note 3)     | RAM and register values retained. |                                                                   | 1.8           |                  | 5.5            |             |

| High level input<br>voltage                                      | VIH(1)          | Output Nch Tr. o                | ff                                | Port C, D with open-drain specifications.                         | 0.7VDD        |                  | 13.5           |             |

|                                                                  | VIH(2)          | Output Nch Tr. o                | ff                                | Port A, E, F                                                      | 0.7VDD        |                  | VDD            |             |

|                                                                  | VIH(3)          | Output Nch Tr. o                |                                   | The INT, SCK,<br>and SI pin with<br>open-drain<br>specifications. | 0.8VDD        |                  | VDD            |             |

|                                                                  | VIH(4)          |                                 | D=1.8 to 5.5 V                    | RES                                                               | 0.8VDD        |                  | VDD            |             |

|                                                                  | VIH(5)          | External clock sp               |                                   | OSC1                                                              | 0.8VDD        |                  | VDD            |             |

| Low level                                                        | VIL(1)          | Output Nch Tr. off              |                                   | Port                                                              | VSS           |                  | 0.3VDD         |             |

| input voltage                                                    | VIL(2)          | Output Nch Tr. off              |                                   | Port                                                              | VSS           |                  | 0.25VDD        |             |

|                                                                  | VIL(3)          | Output Nch Tr. off              |                                   | INT, SCK, SI                                                      | VSS           |                  | 0.25VDD        |             |

|                                                                  | VIL(4)          | Output Nch Tr. off              |                                   | INT, SCK, SI                                                      | VSS           |                  | 0.2VDD         |             |

|                                                                  | VIL(5)          | External clock<br>specification | VDD=4 to 5.5V                     | OSC1                                                              | VSS           |                  | 0.25VDD        |             |

|                                                                  | VIL(6)          | External clock specification    | 3 to 5.5V                         | OSC1                                                              | VSS           |                  | 0.2VDD         |             |

|                                                                  | VIL(7)          | <sup>•</sup>                    | VDD=4 to 5.5V                     | TEST                                                              | VSS           |                  | 0.3VDD         |             |

|                                                                  | VIL(8)          |                                 | 3 to 5.5V                         | TEST                                                              | VSS           |                  | 0.25VDD        |             |

|                                                                  | VIL(9)          |                                 | VDD=4 to 5.5V                     | RES                                                               | VSS           |                  | 0.25VDD        |             |

|                                                                  | VIL(10)         |                                 | 3 to 5.5V                         | RES                                                               | VSS           |                  | 0.2VDD         |             |

| Operating frequency<br>(cycle time)                              | fop<br>(Tcyc)   |                                 | VDD=3 to 5.5V                     |                                                                   | 384<br>(10.4) |                  | 4330<br>(0.92) | kHz<br>(µs) |

| External clock<br>conditions<br>Frequency                        | text            | Fig. 1                          | VDD=3 to 5.5V                     | OSC1                                                              | 384           |                  | 4330           | kHz         |

| Pulse width                                                      | textH,<br>textL |                                 | VDD=3 to 5.5V                     | OSC1                                                              | 69            |                  |                | ns          |

| Rising/falling time                                              | textR,<br>textF | 1                               | VDD=3 to 5.5V                     | OSC1                                                              |               |                  | 50             |             |

| Recommended<br>oscillation constants<br>Two-pin RC<br>oscillator | Cext<br>Rext    | Fig. 2                          | VDD=3 to 5.5V                     | OSC1, OSC2                                                        |               | 270±5%<br>5.6±1% |                | pF<br>kΩ    |

| Ceramic oscillator<br>(Note 4)                                   |                 | Fig. 3                          |                                   |                                                                   |               | See Table        |                |             |

# 2. Recommended Operating Range at Ta=-20 to +85°C, VSS=0V, VDD=3.0 to 5.5V (Unless otherwise specified)

# 3. Electrical Characteristics at Ta=-20 to +85°C, VSS=0V, VDD=3.0 to 5.5V (Unless otherwise specified)

|                             | Parameter                              | Symbol    | Symbol Conditions                                                                                    |                                                             |         |        | unit   |    |

|-----------------------------|----------------------------------------|-----------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------|--------|--------|----|

|                             |                                        | 5911001   |                                                                                                      | and notes                                                   | min.    | max.   | max.   |    |

| Input High level<br>current |                                        | IIH(1)    | Output Nch Tr. OFF<br>(including OFF leak current<br>of Nch Tr.)<br>VIN=+13.5V                       | Port C and D with<br>the open-drain<br>specifications       |         |        | 5.0    | μΑ |

|                             |                                        | IIH (2)   | Output Nch Tr. OFF<br>(including OFF leak current<br>of Nch Tr.)<br>VIN=VDD                          | Port A, E and G<br>with the<br>open-drain<br>specifications |         |        | 1.0    |    |

|                             |                                        | IIH (3)   | When external clock is used,<br>VIN=VDD                                                              | OSC1                                                        |         |        | 1.0    |    |

|                             | ut Low level<br>rent                   | IIL(1)    | Output Nch Tr. OFF<br>VIN=VSS                                                                        | Ports with the open-drain specifications                    | -1.0    |        |        |    |

|                             |                                        | IIL(2)    | Output Nch Tr. OFF<br>VIN=VSS                                                                        | Ports with the<br>pull-up resistor<br>specifications        | -1.3    | -0.35  |        | mA |

|                             |                                        | IIL(3)    | VIN=VSS                                                                                              | RES                                                         | -45     | -10    |        | μA |

|                             |                                        | IIL(4)    | When external clock is used,<br>VIN=VSS                                                              | OSC1                                                        | -1.0    |        |        |    |

|                             | tput High level<br>tage                | VOH (1)   | IOH=-50 μA<br>VDD=4.0 to 6.0V                                                                        | Ports with the<br>pull-up resistor<br>specifications        | VDD-1.2 |        |        | V  |

|                             |                                        | VOH (2)   | ΙΟΗ=-10 μΑ                                                                                           | Ports with the<br>pull-up resistor<br>specifications        | VDD-0.5 |        |        |    |

| Output Low level voltage    |                                        | VOL(1)    | IOL=10 mA<br>VDD=4.0 to 6.0 V                                                                        | Port                                                        |         |        | 1.5    |    |

|                             | -                                      | VOL(2)    | IOL=1 mA,<br>IOL of each Port : 1 mA or less                                                         | Port                                                        |         |        | 0.5    |    |

| eristics                    | Hysteresis<br>Voltage                  | VHIS      |                                                                                                      | RES, INT, SCK,<br>SI, and schmitt<br>specification          |         | 0.1VDD |        |    |

| Schmitt characteristics     | High level<br>threshold<br>voltage     | VtH       |                                                                                                      | OSC1<br>(Note 5)                                            | 0.4VDD  |        | 0.8VDD |    |

| Schmit                      | Low level<br>threshold<br>voltage      | VtL       | -                                                                                                    |                                                             | 0.2VDD  |        | 0.6VDD |    |

|                             | ent consumption<br>o-pin RC oscillator |           | <ul> <li>Output N-channel transistors are<br/>off when operating</li> <li>Port = VDD</li> </ul>      | VDD                                                         |         | 3.0    | 6      | mA |

| 1                           | o più ree oscinator                    | IDDOP (1) | • Fig. 2, fosc=800 kHz (typical)                                                                     |                                                             |         | 5.0    | 0      |    |

| Cer                         | ramic oscillator                       | IDDOP (2) | • Fig. 3, 4 MHz, no divider                                                                          | VDD                                                         |         | 4.0    | 10     |    |

|                             |                                        | IDDOP (3) | • Fig. 3, 4 MHz, divide-by-three circuit                                                             | VDD                                                         |         | 3.0    | 8      |    |

|                             |                                        | IDDOP (4) | • Fig. 3, 4 MHz, divide-by-four circuit                                                              | VDD                                                         |         | 3.0    | 6      |    |

|                             |                                        | IDDOP (5) | • Fig. 3, 400 kHz                                                                                    | VDD                                                         |         | 2.0    | 5      |    |

|                             |                                        | IDDOP (6) | • Fig. 3, 800 kHz                                                                                    | VDD                                                         |         | 3.0    | 6      |    |

| Ext                         | ternal clock                           | IDDOP (7) | • 384 kHz to 4330 kHz, no divider                                                                    | VDD                                                         |         | 4.0    | 10     |    |

|                             |                                        | IDDOP (8) | <ul> <li>1152 kHz to 4330 kHz,<br/>divide-by-three circuit</li> <li>1536 kHz to 4330 kHz,</li> </ul> | VDD                                                         |         | 3.0    | 8      |    |

|                             | ndby mode                              | IDDst     | divide-by-four circuit<br>Output N-channel, VDD=6V                                                   | VDD                                                         |         | 0.05   | 10     | μΑ |

| Sta                         |                                        |           | transistor off                                                                                       |                                                             |         |        |        |    |

| Parameter                                           | Symbol   | Conditions                                                                                                                                             | Pin                                 |                    | Ratings             |                     |      |

|-----------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|---------------------|---------------------|------|

| 1 arameter                                          |          | Conditions                                                                                                                                             | 1 m                                 | min.               | typ.                | max.                | unit |

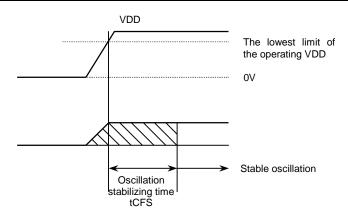

| Oscillation<br>characteristics<br>Ceramic resonator | fCFOSC   | • Fig. 3 fo=400kHz                                                                                                                                     | OSC1,OSC2                           | 392                | 400                 | 408                 | kHz  |

| Frequency                                           | (Note 7) | <ul> <li>Fig. 3 fo=800kHz</li> <li>Fig. 3 fo=1MHz</li> <li>Fig. 3 fo=4MHz, with no divider, divide-by-three, or divide-by-four circuit</li> </ul>      | OSC1,OSC2<br>OSC1,OSC2<br>OSC1,OSC2 | 784<br>980<br>3920 | 800<br>1000<br>4000 | 816<br>1020<br>4080 |      |

| Oscillation<br>stabilizing time<br>(Note 8)         | tCFS     | <ul> <li>Fig. 4 fo=400kHz</li> <li>Fig. 4 fo=800kHz, 1MHz, or<br/>4MHz, with no divider,<br/>divide-by-three, or divide-by-four<br/>circuit</li> </ul> |                                     |                    |                     | 10<br>10            | ms   |

| Two-pin RC oscillator frequency                     | fMOSC    | <ul> <li>Fig. 2 Cext=270pF±5%</li> <li>Fig. 2 Rext=5.6kΩ±1%</li> </ul>                                                                                 | OSC1, OSC2                          | 587                | 800                 | 1298                | kHz  |

| Pull-up resistance<br>RES                           | Ru       | VIN=VSS VDD=5V                                                                                                                                         | RES                                 | 200                | 500                 | 800                 | kΩ   |

| External reset<br>characteristics                   |          |                                                                                                                                                        |                                     |                    |                     |                     |      |

| Reset time                                          | tRST     |                                                                                                                                                        |                                     |                    | See Fig.5           |                     |      |

| Pin capacitance                                     | Ср       | f=1MHz,<br>Pins except for tested pins,<br>VIN=VSS                                                                                                     |                                     |                    | 10                  |                     | pF   |

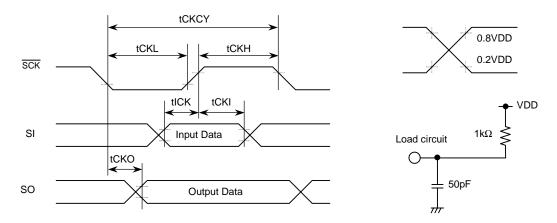

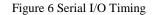

| Serial clock<br>Input clock Cycle<br>time           | tCKCY(1) | Fig. 6                                                                                                                                                 | SCK                                 | 2.0                |                     |                     | μs   |

| Output clock Cycle time                             | tCKCY(2) | Fig. 6                                                                                                                                                 | SCK                                 |                    | 64×tCYC<br>(Note 9) |                     |      |

| Input clock low<br>level pulse width                | tCKL(1)  | Fig. 6                                                                                                                                                 | SCK                                 | 0.6                |                     |                     |      |

| Output clock low<br>level pulse width               | tCKL(2)  | Fig. 6                                                                                                                                                 | SCK                                 |                    | 32×tCYC             |                     |      |

| Input clock high<br>level pulse width               | tCKH(1)  | Fig. 6                                                                                                                                                 | SCK                                 | 0.6                |                     |                     |      |

| Output clock high<br>level pulse width              | tCKH(2)  | Fig. 6                                                                                                                                                 | SCK                                 |                    | 32×tCYC             |                     |      |

| Serial input<br>Data setup time                     | tICK     | Specified for the rising edge of                                                                                                                       | SI                                  | 0.2                |                     |                     |      |

| Data hold time                                      | tCKI     | SCK<br>Fig. 6                                                                                                                                          | SI                                  | 0.2                |                     |                     |      |

| Serial output<br>Output delay time                  | tCKO     | • <u>Specified</u> for the falling edge of <u>SCK</u>                                                                                                  | SO                                  |                    |                     | 0.4                 |      |

|                                                     |          | <ul> <li>Select only Nch OD option, and<br/>add external 1kΩ resistor and<br/>external 50pF capacitor.</li> <li>Fig. 6</li> </ul>                      |                                     |                    |                     |                     |      |

| Parameter                                                                       |                                     | Symbol      | Conditions                                                                                                 |                | Applicable                                                                              |                         | Ratings                 |                        | unit       |

|---------------------------------------------------------------------------------|-------------------------------------|-------------|------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------|-------------------------|-------------------------|------------------------|------------|

| Parameter                                                                       | VDD[V]                              |             |                                                                                                            | pins and notes | min.                                                                                    | typ.                    | max.                    | uiiit                  |            |

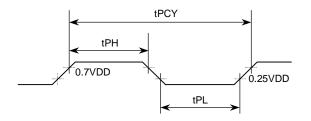

| Pulse output<br>Period<br>High level pulse<br>width<br>Low level pulse<br>width |                                     | tPCY<br>tPH | <ul> <li>Fig.7</li> <li>TCYC=4 × system clock</li> </ul>                                                   |                | PE0<br>PE0                                                                              |                         | 64×TCYC<br>32×TCYC      |                        | μs         |

|                                                                                 |                                     | tPL         | <ul> <li>Select only Nch OD<br/>option,<br/>and add external 1kΩ<br/>resistor and external 50pF</li> </ul> |                | PE0                                                                                     |                         | ±10%<br>32×TCYC<br>±10% |                        |            |

|                                                                                 |                                     |             | capacitor.                                                                                                 |                |                                                                                         |                         |                         |                        |            |

| A/D converter characteristics                                                   | Resolution<br>Absolute<br>precision |             | AV.=VDD<br>AV.=VSS                                                                                         | 3 to 5.5       |                                                                                         |                         | 8<br>±1                 | ±2                     | bit<br>LSB |

|                                                                                 | Conversion<br>time                  | TCAD        | When AD speed is<br>1/1=26*TCYC                                                                            |                |                                                                                         | 24<br>(TCYC=<br>0.92µs) |                         | 260<br>(TCYC=<br>10μs) | μs         |

|                                                                                 |                                     |             | When AD speed is<br>1/2=51*TCYC                                                                            |                |                                                                                         | 47<br>(TCYC=<br>0.92µs) |                         | 510<br>(TCYC=<br>10μs) |            |

| verte                                                                           | Analog input voltage range          | VAIN        |                                                                                                            |                | AD0 to AD7                                                                              | VSS                     |                         | VDD                    | v          |

| A/D con                                                                         | Analog port<br>input current        | IAIN        | Including the output off<br>leakage current.<br>VAIN=VDD<br>VAIN=VSS                                       |                | AD0 to AD7<br>(The shared<br>I/O function<br>ports have<br>open-drain<br>specification) | -1                      |                         | 1                      | μΑ         |

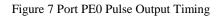

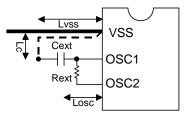

|                                                                                 | Recommended constants               | Cw          | When PE1 is using open-drain                                                                               | 3 to 5.5       | WDR                                                                                     |                         | 0.1±5%                  |                        | μF         |

|                                                                                 | (Note 10)                           | Rw          | When PE1 is using open-drain                                                                               |                | WDR                                                                                     |                         | 680±1%                  |                        | kΩ         |

|                                                                                 |                                     | R1          | When PE1 is using open-drain                                                                               |                | WDR                                                                                     |                         | 100±1%                  |                        | Ω          |

| I                                                                               | Clear time<br>(discharge)           | tWCT        | Fig.8                                                                                                      |                | WDR                                                                                     | 100                     |                         |                        | μs         |

| Watch dog timer                                                                 | Clear period<br>(charge)            | tWCCY       | Fig.8                                                                                                      |                | WDR                                                                                     | 36                      |                         |                        | ms         |

|                                                                                 | Recommended constants               | Cw          | When PE1 is using open-drain                                                                               | 3 to 5.5       | WDR                                                                                     |                         | 0.01±5%                 |                        | μF         |

|                                                                                 | (Note 10)                           | Rw          | When PE1 is using<br>open-drain                                                                            |                | WDR                                                                                     |                         | 680±1%                  |                        | kΩ         |

|                                                                                 |                                     | Rl          | When PE1 is using open-drain                                                                               |                | WDR                                                                                     |                         | 100±1%                  |                        | Ω          |

|                                                                                 | Clear time<br>(discharge)           | tWCT        | Fig.8                                                                                                      |                | WDR                                                                                     | 10                      |                         |                        | μs         |

|                                                                                 | Clear period<br>(charge)            | tWCCY       | Fig.8                                                                                                      | 1              | WDR                                                                                     | 4.2                     |                         |                        | ms         |

Notes:

- (1) When oscillated internally under the oscillating conditions in Fig.3, generated voltage can be over the maximum limit of the VDD.

- (2) Average for 100 ms period.

- (3) Operating supply voltage VDD must be held until the microcontroller enters in the standby mode after the execution of the HALT instruction. Any chattering should not be generated at the PA3 pin during the HALT instruction execution cycle.

- (4) Recommended circuit constants that are verified by the oscillator manufacturer, using oscillator characteristic evaluation board selected by SANYO.

- (5) The OSC1 pin will have schmitt characteristics when external clock oscillator or the two-pin RC oscillator is selected as an oscillation option.