**TDA8453A**

#### **GENERAL DESCRIPTION**

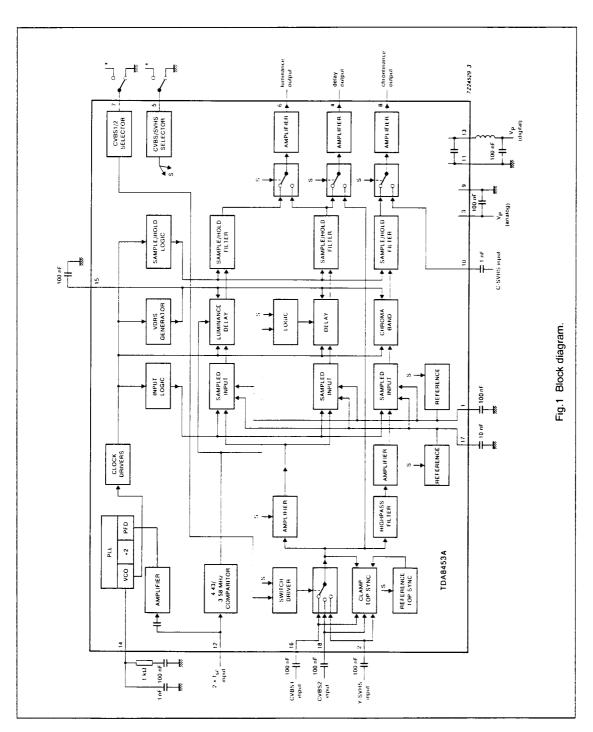

The TDA8453A is an integrated P2CCD (Profiled Peristaltic Charge Coupled Device) filter combination which can accommodate CVBS and S-VHS input signals. The device has been designed to be used in conjunction with various colour decoders and incorporates a luminance delay with chrominance trap, a chrominance bandpass filter, a wideband delay line, clock drivers for the filters which are driven from an internal VCO locked to the 2 x  $\rm f_{sc}$ signal (obtained from the decoder oscillator), a video switch for three different input signals (2 x CVBS and 1 luminance S-SVHS) and a switch for the chrominance S-VHS. This IC replaces TDA8453.

#### **ORDERING INFORMATION**

| EXTENDED    |      | PACKAGE      |          |            |  |  |

|-------------|------|--------------|----------|------------|--|--|

| TYPE NUMBER | PINS | PIN POSITION | MATERIAL | CODE       |  |  |

| TDA8453A    | 18   | DIL          | plastic  | SOT102RG.4 |  |  |

#### **QUICK REFERENCE DATA**

| SYMBOL               | PARAMETER                                                 | CONDITIONS          | MIN. | TYP. | MAX. | UNIT |

|----------------------|-----------------------------------------------------------|---------------------|------|------|------|------|

|                      | supply voltage                                            |                     |      |      |      |      |

| $V_{p(a)}$           | analog (pin 3)                                            | 1                   | 10.8 | 12.0 | 13.2 | v    |

| V <sub>o(d)</sub>    | digital (pin 13)                                          |                     | 10.8 | 12.0 | 13.2 | V    |

|                      | supply current                                            |                     |      |      |      |      |

| I <sub>p(a)</sub>    | analog (pin 3)                                            | 1                   | 12   | 22   | 30   | mA   |

| p(d)                 | digital (pin 13)                                          |                     | 20   | 50   | 70   | mA   |

| $V_{i(p-p)}$         | CVBS input (pins 16 and 18) (peak-to-peak value)          |                     | _    | 0.7  | 1.0  | ٧    |

| $V_{l(p-p)}$         | Y-SVHS input (pin 2) (peak-to-peak value)                 |                     | -    | 1.0  | 1.42 | V    |

| $V_{I(p-p)}$         | C-SVHS input (pin 10) (peak-to-peak value)                |                     | _    | 660  | 935  | mV   |

| V <sub>6(p-p)</sub>  | luminance output for CVBS (pin 6) (peak-to-peak value)    |                     | _    | 0.45 | -    | V    |

| V <sub>6(p-p)</sub>  | luminance output for S-VHS (pin 6) (peak-to-peak value)   |                     | -    | 0.45 | -    | V    |

| V <sub>8(p-p)</sub>  | chrominance output for CVBS (pin 8) (peak-to-peak value)  |                     | 425  | 600  | 850  | mV   |

| V <sub>8(p-p)</sub>  | chrominance output for S-VHS (pin 8) (peak-to-peak value) |                     | 525  | 594  | 660  | mV   |

| V <sub>4(p-p)</sub>  | delayed CVBS output (pin 4) (peak-to-peak value)          |                     | _    | 1.0  |      | ٧    |

| V <sub>4(p-p)</sub>  | delayed S-VHS output (pin 4) (peak-to-peak value)         |                     | -    | 0.9  | _    | ٧    |

| Ro                   | output resistance (pins 4, 6 and 8)                       |                     | 300  | 500  | 800  | Ω    |

| V <sub>12(p-p)</sub> | oscillator input signal (peak-to-peak value)              | 2 x f <sub>sc</sub> | 200  | -    | -    | mV   |

TDA8453A

#### **FUNCTIONAL DESCRIPTION**

The device has four AC-coupled video inputs; CVBS1 (pin 16), CVBS2 (pin 18), luminance S-VHS (Y-SVHS pin 2) and chrominance S-VHS (C-SVHS pin 10).

#### CVBS1, CVBS2 and S-VHS selectors (pins 5 and 7)

The device can accommodate three different video input signals:

CVBS1 pins 5 and 7 LOW CVBS2 pin 5 LOW, pin 7

HIGH

S-VHS contains Y-SVHS

and C-SVHS; pin 5

HIGH

The slicing level of the CVBS/S-VHS selector and of the CVBS1/CVBS2 selector are different. This means. therefore, that the selectors can be controlled with one signal wire that has three different levels (e.g. by the TDA8466).

#### CVBS inputs (pins 16 and 18)

When either input is selected by the input switch the signal is routed through three separate paths before being applied to the sample-and-hold filter stages. The paths are via:

- A delay line used to drive the sync separator circuit, teletext and SECAM decoders etc.

- A luminance delay line with chrominance trap

- A chrominance bandpass filter.

The sample-and-hold lowpass filter stages are used to reduce the clock signals. For the 3.58 MHz TV systems the luminance signal will 'skip' part of the delay line to ensure equal delay times in the chrominance and luminance paths.

#### **PINNING**

| PIN | DESCRIPTION                                           |

|-----|-------------------------------------------------------|

| 1   | reference decoupling                                  |

| 2   | luminance S-VHS input                                 |

| 3   | analog supply voltage input                           |

| 4   | delayed CVBS output or undelayed Y-SVHS output        |

| 5   | CVBS/S-VHS input selector                             |

| 6   | luminance output                                      |

| 7   | CVBS1/CVBS2 input selector                            |

| 8   | chrominance output                                    |

| 9   | analog ground                                         |

| 10  | chrominance S-VHS input                               |

| 11  | digital ground                                        |

| 12  | 2 x f <sub>sc</sub> plus 4.43/3.58 MHz selector input |

| 13  | digital supply voltage input                          |

| 14  | PLL filter                                            |

| 15  | voltage drain reset generator decoupling              |

| 16  | CVBS1 input                                           |

| 17  | reference decoupling                                  |

| 18  | CVBS2 input                                           |

#### S-VHS inputs (pins 2 and 10)

If the CVBS/S-VHS selector is in the S-VHS position (pin 5 HIGH), the luminance signal will be routed through two separate paths. The paths are:

- · Directly through the input switch to the output switch (pin 4). This signal is used to drive the sync separator circuit

- Via a luminance delay without chrominance trap.

The chrominance S-VHS signal is routed directly to the chrominance output switch (pin 8). To ensure that the delay of the luminance signal in both the 4.43 MHz and 3.58 MHz TV systems are equal to the total delay of the chrominance S-VHS signal (which is the sum of the delays in the decoder and the delay line IC), the delay line incorporates more

stages in the 4.43 MHz TV system than the 3.58 MHz TV system.

#### Luminance, chrominance and delayed outputs (pins 6, 8 and 4)

The position of the three output switches depends on the selected input (CVBS or S-VHS). The device also incorporates three output amplifiers:

Luminance output (pin 6)

CVBS luminance delay

with chrominance

trap

S-VHS delayed Y-SVHS

without

chrominance trap

TDA8453A

#### Delay output (pin 4)

CVBS delayed CVBS signal

S-VHS undelayed Y-SVHS

signal

Chrominance output (pin 8)

CVBS chrominance

bandpass filter with delay

S-VHS undelayed C-SVHS

signal without bandpass filter

Because the amplitude of the CVBS and S-VHS input signals are different, the gain of the input amplifiers and the level of top sync are varied to obtain optimal biasing if S-VHS is selected.

#### Oscillator (pins 12 and 14)

The reference for the PLL is obtained from the decoder IC which derives the 2 x  $f_{sc}$  signal from its reference oscillator (the amplitude of this signal may be small, minimum 200 mV(p-p)). The VCO operates at 4 x  $f_{sc}$ , the delay lines and filters are 4 phase clocked at 4 x  $f_{sc}$ . The information whether the incoming signal is 2 x 3.58 MHz or 2 x 4.43 MHz is generated in the decoder IC and fed to the TDA 8453A via the DC level of the 2 x  $f_{sc}$  oscillator signal (pin 12). The filter for the PLL is connected to pin 14.

### Voltage drain reset generator decoupling (pin 15)

The TDA8453A requires a supply voltage of 12 V. The output stages require a higher voltage (approximately 15 V). This voltage is

generated internally with a decoupling capacitor connected to pin 15.

### Decoupling reference (pins 1 and 17)

The reference for the sampled inputs of the delay lines and filters are decoupled externally. When S-VHS is selected the reference will vary to give an optimum bias for the sampled input to enable it to adapt to the change in amplification.

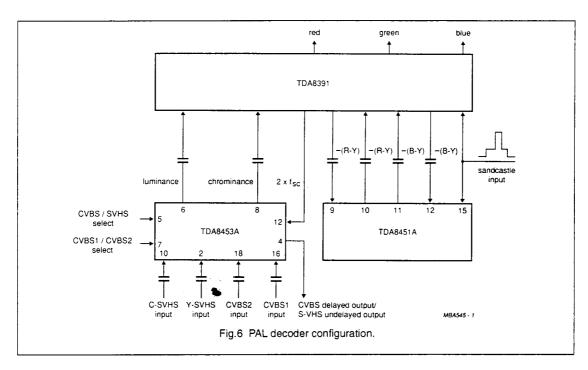

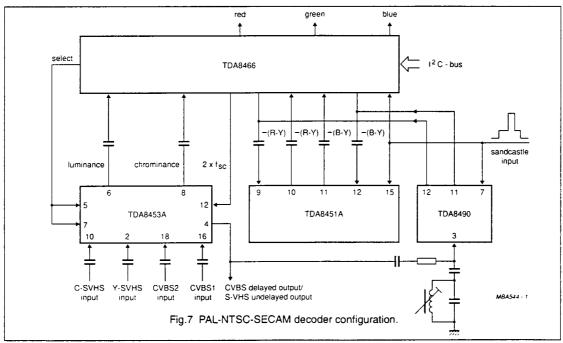

A circuit for the TDA8453A together with a PAL decoder (TDA8391) is illustrated in Fig.6. A circuit for the TDA8453A together with a PAL/NTSC decoder (TDA8466) and a SECAM decoder (TDA8490) is illustrated in Fig.7. The TDA8490 can also be used in combination with the TDA8391.

#### LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL            | PARAMETER                           | MIN. | MAX. | UNIT |

|-------------------|-------------------------------------|------|------|------|

| V <sub>p(a)</sub> | analog supply voltage               | -    | 13.2 | V    |

| V <sub>p(d)</sub> | digital supply voltage              | -    | 13.2 | V    |

| P <sub>tot</sub>  | total power dissipation             | -    | 1.45 | W    |

| T <sub>amb</sub>  | operating ambient temperature range | -25  | +70  | °C   |

| T <sub>stg</sub>  | storage temperature range           | -55  | +150 | °C   |

#### THERMAL RESISTANCE

| SYMBOL              | PARAMETER                            | TYP. | MAX. | UNIT |

|---------------------|--------------------------------------|------|------|------|

| R <sub>th j-a</sub> | from junction to ambient in free air | 55   | -    | K/W  |

### P2CCD filter combination for CVBS and S-VHS

TDA8453A

CHARACTERISTICS  $V_p = 12 \text{ V; } T_{amb} = 25 \,^{\circ}\text{C; } unless otherwise specified}$

| SYMBOL              | PARAMETER                                                                          | CONDITIONS            | MIN. | TYP. | MAX. | UNIT |

|---------------------|------------------------------------------------------------------------------------|-----------------------|------|------|------|------|

| Supplies (          | note 1)                                                                            |                       |      |      |      |      |

| $V_{p(a)}$          | analog supply voltage (pin 3)                                                      |                       | 10.8 | 12.0 | 13.2 | ٧    |

| I <sub>p(a)</sub>   | analog supply current (pin 3)                                                      |                       | 12   | 22   | 30   | mA   |

| SVRR                | supply voltage ripple rejection at 100 mVeff (pin 3)                               | f = 100 Hz            | -    | 7    | -    | db   |

| $V_{p(d)}$          | supply voltage digital (pin 13)                                                    |                       | 10.8 | 12.0 | 13.2 | ٧    |

| I <sub>p(d)</sub>   | supply current digital (pin 13)                                                    |                       | 20   | 50   | 70   | mA   |

| SVRR                | supply voltage ripple rejection at 100 mVeff (pin 13)                              | f = 100 Hz            | _    | 7    | -    | dB   |

| P <sub>tot</sub>    | total power dissipation                                                            |                       | -    | 0.86 | 1.3  | W    |

|                     | e video inputs (pins 16 and 18)                                                    |                       |      |      |      |      |

| AC COUPLE           | D AND CLAMPED ON TOP SYNC (NOTE 2)                                                 |                       |      |      |      |      |

| $V_{I(p-p)}$        | input signal (peak-to-peak value)                                                  |                       | -    | 0.7  | 1.0  | V    |

| 1,                  | input current                                                                      | non-selected input    | -    | -    | 0.1  | μА   |

| l <sub>1</sub>      | input current during non-clamping period of selected input                         |                       | 1.0  | 3.0  | 5.0  | μА   |

| C,                  | input capacitance                                                                  |                       | -    | 5    | _    | pF   |

| α                   | suppression of any other input signal when CVBS1 or CVBS2 is selected (0 to 5 MHz) | R; = 75 Ω             | -    | 50   | -    | dB   |

| Y-SVHS in           | put (pin 2)                                                                        |                       |      |      |      |      |

| AC COUPLE           | D AND CAMPLED ON TOP SYNC; NOTE 3                                                  |                       |      |      |      |      |

| $V_{I(p-p)}$        | input signal (peak-to-peak value)                                                  |                       | -    | 1.0  | 1.42 | ٧    |

| l <sub>i</sub>      | input current                                                                      | non-selected input    |      |      | 0.1  | μА   |

| I,                  | input current during non-clamping period of selected input                         |                       | 1.0  | 3.0  | 5.0  | μА   |

| Cı                  | input capacitance                                                                  |                       | -    | 5    | -    | pF   |

| α                   | suppression of any other input signal when Y-SVHS is selected (0 to 5 MHz)         | $R_i = 75 \Omega$     | -    | 50   | -    | dB   |

| C-SVHS in           | nput (pin 10); note 4                                                              |                       |      |      |      |      |

| V <sub>I(p-p)</sub> | input signal (peak-to-peak value)                                                  |                       | -    | 660  | 935  | mV   |

| R                   | input resistance                                                                   |                       | 4    | 6    | 12   | kΩ   |

| C,                  | input capacitance                                                                  |                       |      | 4    |      | pF   |

| α                   | suppression of any other input signal when C-SVHS is selected (3.8 to 4.9 MHz)     | R <sub>i</sub> = 75 Ω | -    | 50   |      | dB   |

| CVBS sw             | itch control (pin 7)                                                               |                       |      |      |      |      |

| V,                  | CVBS1 input (pin 16)                                                               | pin 5 LOW             | 0    |      | 1.5  | V    |

| V <sub>7</sub>      | CVBS2 input (pin 18)                                                               | pin 5 LOW             | 4    | -    | Vp   | V    |

TDA8453A

| SYMBOL               | PARAMETER                                                                                                                                            | CONDITIONS                                                 | MIN.                                            | TYP.                                            | MAX.                                           | UNIT           |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|------------------------------------------------|----------------|

| CVBS/S-V             | HS switch control (pin 5)                                                                                                                            |                                                            |                                                 |                                                 |                                                |                |

| V <sub>5</sub>       | CVBS1 or CVBS2 input                                                                                                                                 |                                                            | 0                                               | <b> </b> -                                      | 6.8                                            | ٧              |

| V <sub>5</sub>       | S-VHS input (pins 2 and 10)                                                                                                                          |                                                            | 8.2                                             | 1-                                              | V <sub>P</sub>                                 | ٧              |

| PLL refere           | nce input signal (pin 12)                                                                                                                            |                                                            |                                                 | •                                               | •                                              |                |

| V <sub>12(p-p)</sub> | input signal (peak-to-peak value)                                                                                                                    | 2 x f <sub>sc</sub>                                        | 200                                             | -                                               | T-                                             | mV             |

| C <sub>1</sub>       | input capacitance                                                                                                                                    |                                                            | -                                               | 6                                               | -                                              | pF             |

| R,                   | input resistance                                                                                                                                     |                                                            | 1                                               | 1-                                              | -                                              | ΜΩ             |

| V <sub>12</sub>      | DC level for:<br>4.43 MHz signal<br>3.58 MHz signal                                                                                                  |                                                            | 0<br>6.7                                        | -                                               | 5.3<br>V <sub>P</sub>                          | v<br>v         |

| Luminanc             | e signal output (pin 6)                                                                                                                              |                                                            |                                                 |                                                 |                                                |                |

| Ro                   | output resistance                                                                                                                                    |                                                            | 300                                             | 500                                             | 800                                            | Ω              |

| V <sub>6</sub>       | output level for top sync                                                                                                                            |                                                            | 3                                               | _                                               | 7                                              | V              |

| I <sub>6</sub>       | luminance output internal load                                                                                                                       |                                                            | 0.4                                             | -                                               | 1.5                                            | mA             |

| S/N                  | signal-to-noise ratio                                                                                                                                |                                                            | -                                               | 60                                              | _                                              | dB             |

| Luminanc             | e signal output for CVBS (pin 5 LOW); note 2                                                                                                         | 2                                                          |                                                 |                                                 |                                                |                |

| V <sub>6(p-p)</sub>  | output signal (peak-to-peak value)                                                                                                                   | CVBS input signal = 0.7 V                                  | -                                               | 0.45                                            | -                                              | ٧              |

| V <sub>6(p-p)</sub>  | black-to-white output signal (peak-to-peak value)                                                                                                    | note 2                                                     | 225                                             | 320                                             | 450                                            | m∨             |

| V <sub>6(rms)</sub>  | rest clock signals (RMS value)<br>at 4.43 MHz<br>at 8.87 MHz<br>at 17.73 MHz                                                                         | note 6                                                     | -                                               | -<br>-<br>-                                     | 1<br>10<br>12                                  | mV<br>mV       |

| L <sub>6(p-p)</sub>  | linearity black-to-white (peak-to peak-value)                                                                                                        | note 7 CVBS input signal = 0.7 V CVBS input signal = 1.0 V | 0.95                                            | -                                               | -                                              |                |

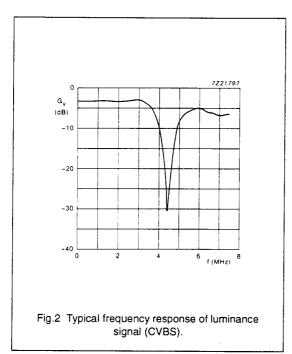

| В                    | bandwidth                                                                                                                                            | at -3 dB                                                   | 3.7                                             | 3.8                                             | -                                              | MHz            |

| Δf                   | frequency response with regard to 0 MHz (Fig.2)<br>at 2.2 MHz<br>at 3.0 MHz<br>at 3.8 MHz<br>at 4.26 MHz<br>at 4.43 MHz<br>at 4.64 MHz<br>at 5.5 MHz |                                                            | -1.0<br>-0.5<br>-4.0<br>-20<br>-<br>-18<br>-5.0 | 0.5<br>1.0<br>-2.5<br>-15<br>-25<br>-12<br>-2.0 | 2.0<br>2.5<br>-1.0<br>-12<br>-20<br>-10<br>1.0 | 68 68 68 68 68 |

| t <sub>d</sub>       | luminance signal delay<br>at 8.87 MHz reference input<br>at 7.16 MHz reference input                                                                 |                                                            | 2060<br>2270                                    | 2090<br>2300                                    | 2120<br>2330                                   | ns<br>ns       |

3052

TDA8453A

| SYMBOL              | PARAMETER                                                                                                                        | CONDITIONS                                                                          | MIN.                        | TYP.                                            | MAX.                                     | UNIT                             |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------|------------------------------------------|----------------------------------|

| Luminance           | e signal output for S-VHS (pin 5 HIGH); not                                                                                      | e 3                                                                                 |                             |                                                 |                                          | _                                |

| V <sub>6(p-p)</sub> | output signal                                                                                                                    | $V_2 = 1 V(p-p)$                                                                    | -                           | 0.45                                            | -                                        | V                                |

| V <sub>6(p-p)</sub> | black-to-white output signal (peak-to-peak value)                                                                                | note 3                                                                              | 225                         | 320                                             | 450                                      | mV                               |

| V <sub>6(rms)</sub> | rest clock signals (RMS value)<br>at 4.43 MHz<br>at 8.87 MHz<br>at 17.73 MHz                                                     | note 6                                                                              | _<br>_<br>_                 | -<br>-<br>-                                     | 1<br>10<br>12                            | mV<br>mV<br>mV                   |

| L <sub>6(p-p)</sub> | linearity black-to-white                                                                                                         | note 7<br>$V_2 = 1 V(p-p)$<br>$V_2 = 1.42 V(p-p)$                                   | 0.95<br>0.94                | -<br> -                                         | -                                        |                                  |

| В                   | bandwidth                                                                                                                        | at –3 dB                                                                            | 5.5                         | 6.5                                             | -                                        | MHz                              |

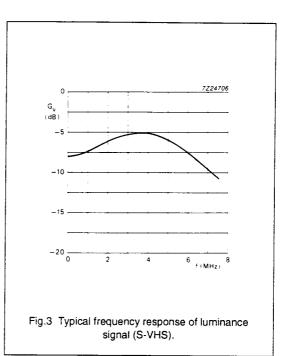

| Δf                  | frequency response with regard to 0 MHz (Fig.3)<br>at 2.2 MHz<br>at 3.0 MHz<br>at 4.43 MHz<br>at 5.5 MHz                         |                                                                                     | 0<br>0.5<br>1.0<br>–1.0     | 1.0<br>1.5<br>2.0<br>0.5                        | 2.5<br>3.0<br>3.5<br>+2.0                | dB<br>dB<br>dB<br>dB             |

| t <sub>u</sub>      | luminance signal delay<br>at 8.87 MHz reference input<br>at 7.16 MHz                                                             |                                                                                     | 1045<br>1010                | 1075<br>1040                                    | 1105<br>1070                             | ns<br>ns                         |

| Chromina            | nce signal output (pin 8)                                                                                                        |                                                                                     |                             |                                                 |                                          |                                  |

| R <sub>o</sub>      | output resistance                                                                                                                |                                                                                     | 300                         | 500                                             | 800                                      | Ω                                |

| V <sub>8</sub>      | DC output level                                                                                                                  |                                                                                     | 3.0                         | -                                               | 7.5                                      | V                                |

| l <sub>8</sub>      | chrominance output internal load                                                                                                 |                                                                                     | 0.4                         | -                                               | 1.5                                      | mA                               |

| S/N                 | signal-to-noise ratio                                                                                                            | note 5                                                                              | <u> </u>                    | 65                                              | -                                        | dB                               |

| Chromina            | nce signal output for CVBS                                                                                                       |                                                                                     |                             |                                                 |                                          |                                  |

| V <sub>8(p-p)</sub> | output signal (peak-to-peak value)                                                                                               | $V_{16.18} = 0.465 \text{ V(p-p)}$                                                  | 425                         | 600                                             | 850                                      | mV                               |

| V <sub>8(rms)</sub> | rest clock signals (RMS value)<br>at 4.43 MHz<br>at 8.87 MHz<br>at 17.73 MHz                                                     | note 6                                                                              | -<br>-<br>-                 | _<br>_<br>_                                     | 0.2<br>10<br>12                          | mV<br>mV                         |

| L <sub>8(p-p)</sub> | linearity of output signals                                                                                                      | note 7<br>$V_{16. 18} = 0.465 \text{ V(p-p)}$<br>$V_{16. 18} = 0.66 \text{ V(p-p)}$ | -                           | 0.97<br>0.95                                    | <br> -                                   |                                  |

| В                   | bandwidth                                                                                                                        | at -3 dB                                                                            | -                           | 1.15                                            | _                                        | MHz                              |

| Δf                  | frequency response with regard to 4.43 MHz (Fig.4) at 0.9 MHz at 1.9 MHz at 2.5 MHz at 3.0 MHz at 3.8 MHz at 4.93 MHz at 5.6 MHz |                                                                                     | -<br>-<br>-<br>-3.5<br>-4.0 | -20<br>-35<br>-30<br>-20<br>-2.5<br>-3.0<br>-16 | -15<br>-30<br>-25<br>-16<br>-1.5<br>-2.0 | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

June 1991 3053

### TDA8453A

| SYMBOL              | PARAMETER                                                                               | CONDITIONS                                                                          | MIN.                 | TYP.         | MAX.                 | UNIT           |

|---------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------|--------------|----------------------|----------------|

| Chrominan           | ce signal output for CVBS                                                               |                                                                                     |                      |              |                      |                |

| t <sub>d</sub>      | chrominance filter delay<br>at 8.87 MHz reference input<br>at 7.16 MHz reference input  |                                                                                     | 990<br>1220          | 1020<br>1250 | 1050<br>1280         | ns<br>ns       |

| Chrominan           | ce signal output for S-VHS (pin 5 h                                                     | HIGH); note 4                                                                       |                      |              |                      |                |

| V <sub>8(p-p)</sub> | output signal (peak-to-peak value)                                                      | $V_8 = 0.66 \text{ V(p-p)}$                                                         | 525                  | 594          | 660                  | mV             |

| V <sub>B(rms)</sub> | rest clock signals (RMS value)<br>at 4.43 MHz<br>at 8.87 MHz<br>at 17.73 MHz            | note 6                                                                              | -<br>-<br>-          | -            | 0.2<br>10<br>12      | mV<br>mV<br>mV |

| L <sub>8(p·p)</sub> | linearity of the output signal                                                          | note 7<br>$V_{16. 18} = 0.66 \text{ V(p-p)}$<br>$V_{16. 18} = 0.935 \text{ V(p-p)}$ | 0.97<br>0.95         | -            | -                    |                |

| В                   | bandwidth                                                                               | at -3 dB                                                                            | 6.0                  | _            |                      | MHz            |

| Δf                  | frequency response with regard to<br>4.43 MHz<br>at 0.9 MHz<br>at 3.0 MHz<br>at 5.6 MHz |                                                                                     | -0.5<br>-0.5<br>-1.0 | 0<br>0<br>0  | +0.5<br>+0.5<br>+0.5 | dB<br>dB<br>dB |

| t <sub>d</sub>      | chrominance signal delay                                                                |                                                                                     |                      | 30           |                      | ns             |

| Delayed sig         | gnal output (pin 4)                                                                     |                                                                                     |                      |              |                      |                |

| R <sub>o</sub>      | output resistance                                                                       |                                                                                     | 300                  | 500          | 800                  | Ω              |

| V <sub>4</sub>      | output level for top sync                                                               |                                                                                     | 2.5                  |              | 7.0                  | V              |

| 14                  | delayed output internal load                                                            |                                                                                     | 0.4                  |              | 1.5                  | .mA            |

| S/N                 | signal-to-noise ratio                                                                   | note 5                                                                              |                      | 65           |                      | dB             |

| Delayed sig         | gnal output for CVBS                                                                    |                                                                                     |                      |              |                      |                |

| V <sub>4(p-p)</sub> | output signal (peak-to-peak value)                                                      | input signal =<br>0.7 V CVBS(p-p)                                                   | -                    | 1.0          | -                    | V              |

| V <sub>4(p-p)</sub> | black-to-white output signal (peak-to-peak value)                                       | note 2                                                                              | 0.49                 | 0.70         | 0.98                 | V              |

| V <sub>4(p-p)</sub> | output sync pulse (peak-to-peak value)                                                  | input sync pulse = 210 mV(p-p)                                                      | 210                  |              | -                    | mV             |

| V <sub>4(rms)</sub> | rest clock signals (RMS value)<br>at 4.43 MHz<br>at 8.87 MHz<br>at 17.73 MHz            | note 4                                                                              | -<br>-<br>-          | -<br>-<br>-  | 1<br>10<br>12        | mV<br>mV<br>mV |

| L <sub>4(p-p)</sub> | linearity black-to-white                                                                | note 7<br>$V_{16, 18} = 0.7 \text{ V(p-p)}$<br>$V_{16, 18} = 1 \text{ V(p-p)}$      | 0.95<br>0.94         | -            | -                    |                |

| В                   | bandwidth                                                                               | at -3 dB                                                                            | 5.5                  | 6.5          |                      | MHz            |

June 1991 3054

TDA8453A

| SYMBOL              | PARAMETER                                                                                    | CONDITIONS                                        | MIN.               | TYP.               | MAX.              | UNIT           |

|---------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------|--------------------|-------------------|----------------|

| Delayed sig         | gnal output for CVBS                                                                         | 1                                                 | <u>-</u>           |                    |                   |                |

| Δf                  | frequency response with regard to<br>0 MHz (Fig.5)<br>at 0.9 MHz<br>at 2.2 MHz<br>at 3.1 MHz |                                                   | -0.5<br>0<br>0     | 0.5<br>1.0<br>1.5  | 1.5<br>2.5<br>2.5 | dB<br>dB<br>dB |

| t <sub>a</sub>      | at 5.5 MHz  CVBS signal delay at 8.87 MHzreference input at 7.16 MHz reference input         |                                                   | -3.0<br>595<br>730 | -1.5<br>695<br>760 | 0.5<br>655<br>790 | ns<br>ns       |

| Delayed sig         | gnal output for S-VHS (pin 5 HIGH)                                                           | ; note 3                                          |                    |                    |                   |                |

| V <sub>4(p-p)</sub> | output signal (peak-to-peak value)                                                           | $V_2 = 1 \ V(p-p)$                                | -                  | 0.9                | -                 | ٧              |

| V <sub>4(p-p)</sub> | black-to-white output signal (peak-to-peak value)                                            | note 3                                            | 0.55               | 0.63               | 0.70              | V              |

| V <sub>4(p-p)</sub> | output sync pulse (peak-to-peak value)                                                       | input sync pulse = 300 mV(p-p)                    | 210                | -                  | -                 | mV             |

| V <sub>4(rms)</sub> | rest clock signals (RMS value)<br>at 4.43 MHz<br>at 8.87 MHz<br>at 17.73 MHz                 | note 4                                            | -                  | -<br> -<br> -      | 1<br>10<br>12     | mV<br>mV<br>mV |

| L <sub>4(p-p)</sub> | linearity black-to-white                                                                     | note 7<br>$V_2 = 1 V(p-p)$<br>$V_2 = 1.42 V(p-p)$ | 0.95<br>0.94       | <br> -<br> -       | -<br> -           |                |

| В                   | bandwidth                                                                                    | at -3 dB                                          | 6.0                | -                  | -                 | MHz            |

| Δf                  | frequency response with regard to 0 MHz at 2.2 MHz at 5.5 MHz                                |                                                   | -0.5<br>-1.0       | 0                  | 0.5<br>0.5        | dB<br>dB       |

| t <sub>a</sub>      | Y-SVHS signal delay                                                                          |                                                   | -                  | 40                 | -                 | ns             |

### Notes to the characteristics

- 1. To prevent linearities and rest clock signals from deteriorating, it is recommended that the difference between the supply voltages at pins 3 and 13 should be less than 500 mV.

- 2. Unless otherwise specified all figures are related to a CVBS input signal of 0.7 V(p-p); 100% contrast; 75% saturation.

In this condition the input signal is formed by the following components:

- 210 mV(p-p) sync pulse

- 490 mV(p-p) black-to-white

- 465 mV(p-p) chrominance

- 3. The figures are related to a Y-SVHS input signal of 1 V(p-p), 100% contrast. In this condition the input signal is formed by the following components:

- 300 mV(p-p) sync pulse

- 700 mV(p-p) luminance

TDA8453A

#### Notes to the characteristics

- The figures are related to a C-SVHS input signal of 660 mV(p-p). This amplitude corresponds to a video signal of 1 V(p-p). 100% contrast and 75% saturation.

- 5. The signal-to-noise ratio is specified as nominal  $V_{out(p-p)}/V_{noise(rms)}$  (0 to 5 MHz).

- 6. The rest clock signals are measured with an FET probe (3.5 pF in parallel with a 1 M $\Omega$  resistor) connected directly to pins 4 and 9, pins 6 and 9 or pins 8 and 9.

- 7. The linearity is defined as the amplification at the given input voltage swing, divided by the amplification when the input voltage swing is decreased to 70%.

TDA8453A

10 G<sub>V</sub> (dB)

Fig.4 Typical frequency response of chrominance signal (CVBS).

f (MHz)

Fig.5 Typical frequency response of delayed signal (CVBS).

-20

-30

### TDA8453A