## MC6840

## **Programmable Timer Module (PTM)**

The MC6840 is a programmable subsystem component of the M6800 Family designed to provide variable system time intervals.

The MC6840 has three 16-bit binary counters, three corresponding control registers, and a status register. These counters are under software control and may be used to cause system interrupts and or generate output signals. The MC6840 may be utilized for such tasks as frequency measurements, event counting, interval measuring, and similar tasks. The device may be used for square wave generation, gated delay signals, single pulses of controlled duration, and pulse width modulation as well as system interrupts.

- Operates from a Single 5-Volt Power Supply

- Fully TTL Compatible

- Single System Clock Required (Enable)

- Selectable Prescaler on Timer 3 Capable of 4 MHz for the MC6840, 6 MHz for the MC68A40 and 8 MHz for the MC68B40

- Programmable Interrupts (IRQ) Output to MPU

- Readable Down Counter Indicates Counts to Go Until Time-Out

- Selectable Gating for Frequency or Pulse-Width Comparison

- RESET Input

- Three Asynchronous External Clock and Gate Trigger Inputs Internally Synchronized

- Three Maskable Outputs

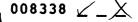

#### **BLOCK DIAGRAM**

## **POWER CONSIDERATIONS**

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \cdot \theta_{JA}) \tag{1}$$

where:

$\mathsf{T}_\mathsf{A}$ = Ambient Temperature, °C

$H_{JA}$ = Package Thermal Resistance, Junction-to-Ambient, °C/W

$= P_{INT} + P_{PORT}$   $= I_{CC} \times V_{CC}, Watts - Chip Internal Power$

= Port Power Dissipation, Watts — User Determined

$For most applications \ P_{\mbox{\footnotesize{PORT}}} < P_{\mbox{\footnotesize{INT}}} \ \ and \ can \ be \ neglected. \ P_{\mbox{\footnotesize{PORT}}} \ \ may \ become \ significant \ if \ the \ device \ is \ configured \ \ device \ is \ configured \ \ \ device \ \ device \ \ device \ \ \ device \ \ device$ to drive Darlington bases or sink LED loads.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{PORT}$  is neglected) is:

$$P_D = K \div (T_J + 273^{\circ}C)$$

(2)

Solving equations (1) and (2) for K gives:

$$K = P_D \cdot (T_A + 273^{\circ}C) + \theta_{JA} \cdot P_D^2$$

(3)

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring PD (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of  $T_A$

#### **MAXIMUM RATINGS**

| Rating                                                                                                          | Symbol           | Value                  | Unit |

|-----------------------------------------------------------------------------------------------------------------|------------------|------------------------|------|

| Supply Voltage                                                                                                  | VCC              | -0.3 to $+7.0$         | V    |

| Input Voltage                                                                                                   | V <sub>in</sub>  | -0.3 to $+7.0$         | V    |

| Operating Temperature Range — T <sub>L</sub> to T <sub>H</sub><br>MC6840, MC68A40, MC68B40<br>MC6840C, MC68A40C | TA               | 0 to +70<br>-40 to +85 | °C   |

| Storage Temperature Range                                                                                       | T <sub>stg</sub> | - 55 to + 150          | °C   |

#### THERMAL CHARACTERISTICS

| Characteristic     | Symbol | Value | Unit |

|--------------------|--------|-------|------|

| Thermal Resistance | θЈД    |       | °C:W |

| Cerdip             |        | 65    |      |

| Plastic            |        | 100   |      |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields, however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{CC}$  Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{CC}$ ).

DC ELECTRICAL CHARACTERISTICS (VCC = 5.0 Vdc +5%, Vcc = 0. TA = TL to TH unless otherwise noted)

| Characteristic                                                  |               | Symbol           | Min                   | Тур | Max                   | Unit        |

|-----------------------------------------------------------------|---------------|------------------|-----------------------|-----|-----------------------|-------------|

| Input High Voltage                                              |               | VIH              | V <sub>SS</sub> + 2.0 |     | Vcc                   | V           |

| Input Low Voltage                                               |               | VIL              | V <sub>SS</sub> -0.3  | _   | V <sub>SS</sub> + 0.8 | V           |

| Input Leakage Current (V <sub>in</sub> = 0 to 5.25 V)           |               | lin              | -                     | 1.0 | 2.5                   | μА          |

| Hi-Z (Off State) Input Current (V <sub>in</sub> = 0.5 to 2.4 V) | D0-D7         | <sup>I</sup> TSI | _                     | 2.0 | 10                    | μА          |

| Output High Voltage                                             |               |                  |                       |     |                       | <u> </u>    |

| $(I_{Load} = -205 \mu\text{A})$                                 | D0-D7         | Vон              | VSS + 2.4             |     | _                     | V           |

| $( L_{\text{oad}} = -200 \mu\text{A})$                          | Other Outputs |                  | VSS + 2.4             |     | _                     |             |

| Output Low Voltage                                              |               |                  |                       |     |                       | <b></b>     |

| $(1_{Load} = 1.6 \mathrm{mA})$                                  | ĪRQ, D0-D7    | Vol              | 1 – 1                 | _   | Vss+0.4               | V           |

| $(I_{Load} = 3.2 \text{ mA})$                                   | 01-03         |                  |                       | _   | VSS+0.4               |             |

| Output Leakage Current (Off State) (VOH = 2.4 V)                | IRQ           | LOH              | _                     | 1.0 | 10                    | μA          |

| Internal Power Dissipation (Measured at $T_A = T_L$ )           | *****         | PINT             | _                     | 470 | 700                   | mW          |

| Input Capacitance                                               |               |                  |                       |     |                       | · · · · · · |

| $(V_{in} = 0, T_A = 25 {}^{\circ}\text{C}, f = 1.0 \text{MHz})$ | D0-D7         | Cin              | _                     | _   | 12.5                  | ρF          |

|                                                                 | All Others    | ,,,,             | -                     | _   | 7.5                   | '           |

| Output Capacitance                                              |               |                  |                       |     |                       |             |

| $(V_{in} = 0, T_A = 25 ^{\circ}C, f = 1.0 MHz)$                 | ĪRQ           | Cout             | _                     | _   | 5.0                   | pF          |

|                                                                 | 01, 02, 03    |                  | _                     | ±   | 10                    | ŀ           |

#### AC OPERATING CHARACTERISTICS (See Figures 2-7)

| Characteristic                                                                                                           | Symbol                            | MC6840        |                   | MC68A40       | )                  | MC68B40          | )                 | Unit           |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------|-------------------|---------------|--------------------|------------------|-------------------|----------------|

| Characteristic                                                                                                           | Symbol                            | Min           | Max               | Min           | Max                | Min              | Max               | Unit           |

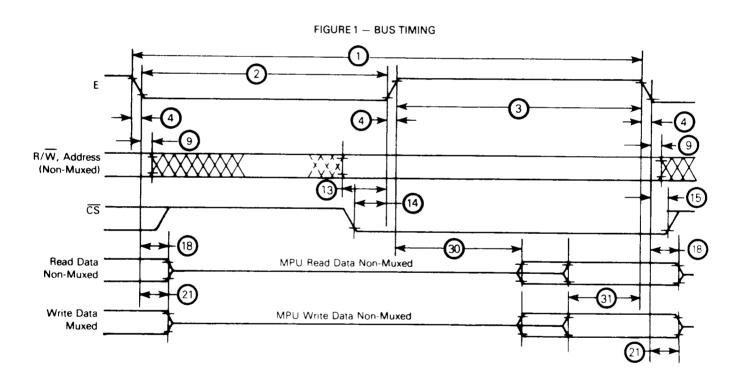

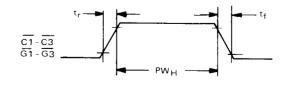

| Input Rise and Fall Times<br>(Figures 4 and 5) Ĉ, Ĝ, and RESET                                                           | t <sub>r</sub> , t <sub>f</sub>   | ***           | 1.0*              | _             | 0.666*             |                  | 0.500*            | μS             |

| Input Pulse Width Low (Figure 2)<br>(Asynchronous Input)<br>C, G, and RESET                                              | PWL                               | tcycE+tsu+thd | -                 | tcycE+tsu+thd | _                  | tcycE+tsu+thd    | ***               | ns             |

| Input Pulse Width High (Figure 3) (Asynchronous Input) C, G                                                              | PWH                               | tcycE+tsu+thd | _                 | tcycE+tsu+thd | -                  | tcycE+tsu+thd    | -                 | ns             |

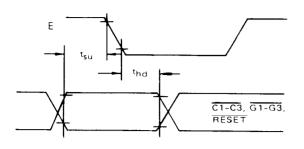

| Input Setup Time (Figure 4) (Synchronous Input) C, G, and RESET                                                          | <sup>t</sup> su                   | 200           |                   | 120           | _                  | 75               | _                 | ns             |

| Input Hold Time (Figure 4) (Synchronous Input) C. G. and RESET                                                           | <sup>t</sup> hd                   | 50            | _                 | 50            | _                  | 50               |                   | ns             |

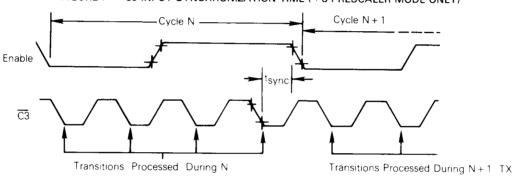

| Input Synchronization Time (Figure 7)  C3 (+8 Prescaler Mode Only)                                                       | <sup>t</sup> sync                 | 250           |                   | 200           | -                  | 175              |                   | ns             |

| Input Pulse Width C3 (-8 Prescaler Mode Only)                                                                            | PW <sub>L</sub> , PW <sub>H</sub> | 120           |                   | 80            | _                  | 60               | -                 | ns             |

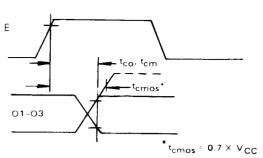

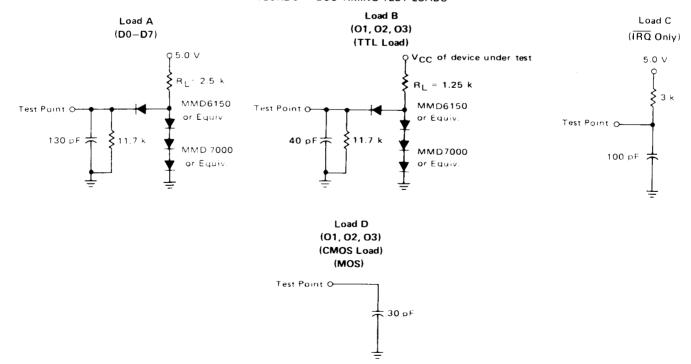

| Output Delay, 01-03 (Figure 5)<br>(VOH = 2.4 V, Load B) TTL<br>(VOH = 2.4 V, Load D) MOS<br>(VOH = 0.7 VDD, Load D) CMOS | tco<br>tcm<br>tcmos               | -<br>-<br>-   | 700<br>450<br>2.0 | -<br>-        | 460<br>450<br>1.35 | _<br>_<br>_<br>_ | 340<br>340<br>1.0 | ns<br>ns<br>µs |

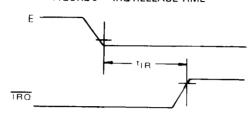

| Interrupt Release Time (Figure 6)                                                                                        | tiR                               | -             | 1.2               | _             | 0.9                | -                | 0.7               | μS             |

<sup>\*</sup>t<sub>r</sub> and t<sub>f</sub>≤t<sub>CycE</sub>

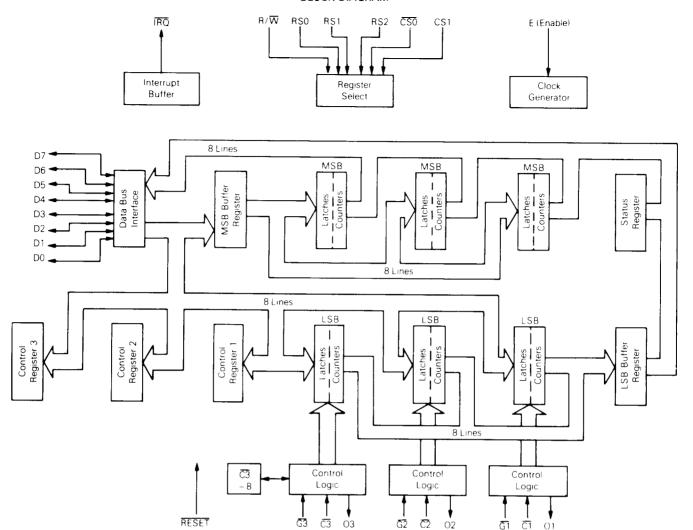

## BUS TIMING CHARACTERISTICS (See Notes 1, 2, and 3)

| ldent. | Characteristic                    | C b l                           | MC6840 |      | MC68A40 |      | MC68B40 |          |          |

|--------|-----------------------------------|---------------------------------|--------|------|---------|------|---------|----------|----------|

| Number |                                   | Symbol                          |        | Max  | Min     | Max  | Min     | Max      | Unit     |

| 11     | Cycle Time                        | t <sub>cyc</sub>                | 1.0    | 10   | 0.67    | 10   | 0.5     | 10       | μS       |

| 2      | Pulse Width, E Low                | PWFI                            | 430    | 9500 | 280     | 9500 | 210     | 9500     | ns       |

| 3      | Pulse Width, E High               | PWEH                            | 450    | 9500 | 280     | 9500 | 220     | 9500     | ns       |

| 4      | Clock Rise and Fall Time          | t <sub>r</sub> , t <sub>f</sub> | _      | 25   | 200     | 25   |         | 20       | ns       |

| 9      | Address Hold Time                 | t <sub>AH</sub>                 | 10     | _    | 10      |      | 10      |          |          |

| 13     | Address Setup Time Before E       | t <sub>AS</sub>                 | 80     |      | 60      |      | 40      |          | ns<br>ns |

| 14     | Chip Select Setup Time Before E   | tCS                             | 80     | _    | 60      |      | 40      |          | ns<br>ns |

| 15     | Chip Select Hold Time             | t <sub>CH</sub>                 | 10     |      | 10      |      | 10      | -        |          |

| 18     | Read Data Hold Time               | t <sub>DHR</sub>                | 20     | 50*  | 20      | 50*  | 20      | -<br>50* | ns       |

| 21     | Write Data Hold Time              |                                 | 10     |      | 10      |      |         |          | ns       |

| 30     | Peripheral Output Data Delay Time | WHQt                            |        | -    |         | 100  | 10      |          | ns       |

| 31     | Peripheral Input Data Setup Time  | †DDR                            | 105    | 290  | -       | 180  | -       | 150      | ns       |

|        | Tomphoral hipat bata betap fillie | tDSW                            | 165    | -    | 80      | _    | 60      | -        | ns       |

<sup>\*</sup>The data bus output buffers are no longer sourcing or sinking current by tDHR max (High Impedance)

#### NOTES:

- 1. Not all signals are applicable to every part.

- 2. Voltage levels shown are V<sub>L</sub>≤0.4 V, V<sub>H</sub>≥2.4 V, unless otherwise specified.

- 3. Measurement points shown are 0.8 V and 2.0 V, unless otherwise specified.

FIGURE 2 - INPUT PULSE WIDTH LOW

${\bf FIGURE 3-INPUT\ PULSE\ WIDTH\ HIGH}$

## FIGURE 4 — INPUT SETUP AND HOLD TIMES

#### FIGURE 5 - OUTPUT DELAY

#### FIGURE 6 - IRQ RELEASE TIME

FIGURE 7  $-\overline{\text{C3}}$  INPUT SYNCHRONIZATION TIME (  $\div$  8 PRESCALER MODE ONLY)

FIGURE 8 - BUS TIMING TEST LOADS

NOTE: Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

#### **DEVICE OPERATION**

The MC6840 is part of the M6800 microprocessor family and is fully bus compatible with M6800 systems. The three timers in the MC6840 operate independently and in several distinct modes to fit a wide variety of measurement and synthesis applications.

The MC6840 is an integrated set of three distinct counter/timers. It consists of three 16-bit data latches, three 16-bit counters (clocked independently), and the comparison and enable circuitry necessary to implement various measurement and synthesis functions. In addition, it contains interrupt drivers to alert the processor that a particular function has been completed.

In a typical application, a timer will be loaded by first storing two bytes of data into an associated Counter Latch. This data is then transferred into the counter via a Counter Initialization cycle. If the counter is enabled, the counter decrements on each subsequent clock period which may be an external clock, or Enable (E) until one of several predetermined conditions causes it to halt or recycle. The timers are thus programmable, cyclic in nature, controllable by external inputs or the MPU program, and accessible by the MPU at any time.

#### **BUS INTERFACE**

The Programmable Timer Module (PTM) interfaces to the M6800 Bus with an 8-bit bidirectional data bus, two Chip Select lines, a Read/Write line, a clock (Enable) line, and Interrupt Request line, an external Reset line, and three Register select lines. VMA should be utilized in conjunction with an MPU address line into a Chip Select of the PTM when using the MC6800/6802/6808.

**BIDIRECTIONAL DATA (D0-D7)** — The bidirectional data lines (D0-D7) allow the transfer of data between the MPU and PTM. The data bus output drivers are three-state devices which remain in the high-impedance (off) state except when the MPU performs a PTM read operation (Read/Write and Enable lines high and PTM Chip Selects activated).

**CHIP SELECT** (CSO, CS1) — These two signals are used to activate the Data Bus interface and allow transfer of data from the PTM. With CS0=0 and CS1=1, the device is selected and data transfer will occur.

**READ/WRITE** (R/ $\overline{\mathbf{W}}$ ) — This signal is generated by the MPU to control the direction of data transfer on the Data Bus. With the PTM selected, a low state on the PTM R/ $\overline{\mathbf{W}}$  line enables the input buffers and data is transferred from the MPU to the PTM on the trailing edge of the E (Enable) clock. Alternately, (under the same conditions) R/ $\overline{\mathbf{W}}$ =1 and Enable high allows data in the PTM to be read by the MPU.

**ENABLE (E CLOCK)** — The E clock signal synchronizes data transfer between the MPU and the PTM. It also performs an equivalent synchronization function on the external clock, reset, and gate inputs of the PTM.

**INTERRUPT REQUEST (IRQ)** — The active low Interrupt Request signal is normally tied directly (or through priority interrupt circuitry) to the IRQ input of the MPU. This is an

"open drain" output (no load device on the chip) which permits other similar interrupt request lines to be tied together in a wire-OR configuration.

The IRQ line is activated if, and only if, the Composite Interrupt Flag (Bit 7 of the Internal Status Register) is asserted. The conditions under which the IRQ line is activated are discussed in conjunction with the Status Register.

**RESET** — A low level at this input is clocked into the PTM by the E (Enable) input. Two Enable pulses are required to synchronize and process the signal. The PTM then recognizes the active "low" or inactive "high" on the third Enable pulse. If the RESET signal is asynchronous, an additional Enable period is required if setup times are not met. The RESET input must be stable High/Low for the minimum time stated in the AC Operating Characteristics.

Recognition of a low level at this input by the PTM causes the following action to occur:

- a. All counter latches are preset to their maximum count values.

- All Control Register bits are cleared with the exception of CR10 (internal reset bit) which is set.

- c. All counters are preset to the contents of the latches.

- All counter outputs are reset and all counter clocks are disabled.

- e. All Status Register bits (interrupt flags) are cleared.

**REGISTER SELECT LINES (RS0, RS1, RS2)** — These inputs are used in conjunction with the R/W line to select the internal registers, counters and latches as shown in Table 1.

#### NOTE

The PTM is accessed via MPU Load and Store operations in much the same manner as a memory device. The instructions available with the M6800 family of MPUs which perform read-modify-write operations on memory should not be used when the PTM is accessed. These instructions actually fetch a byte from memory, perform an operation, then restore it to the same address location. Since the PTM uses the  $R/\overline{W}$  line as an additional register select input, the modified data will not be restored to the same register if these instructions are used.

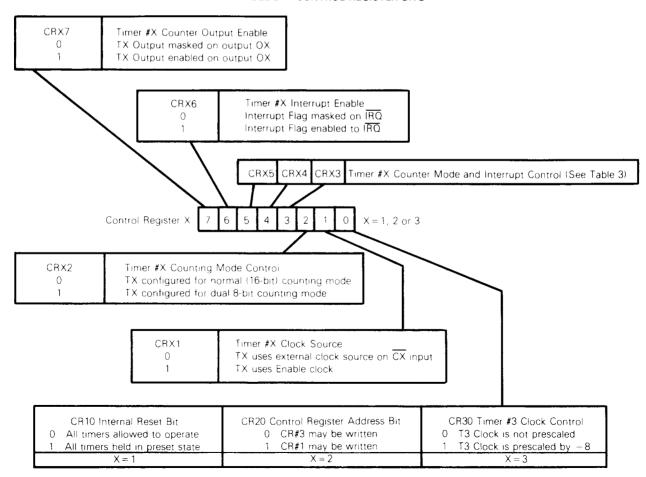

#### CONTROL REGISTER

Each timer in the MC6840 has a corresponding write-only Control Register. Control Register #2 has a unique address space (RS0=1, RS=0, RS2=0) and therefore may be written into at any time. The remaining Control Registers (#1 and #3) share the Address Space selected by a logic zero on all Register Select inputs.

CR20 — The least significant bit of Control Register #2 (CR20) is used as an additional addressing bit for Control Registers #1 and #3. Thus, with all Register selects and R/W inputs at logic zero, Control Register #1 will be written into if CR20 is a logic one. Under the same conditions, Control Register #3 can also be written into after a RESET low condition has occurred, since all control register bits (except CR10) are cleared. Therefore, one may write in the sequence CR3, CR2, CR1.

TABLE 1 - REGISTER SELECTION

| Register<br>Select Inputs |     |     | Operations                         |                          |  |  |  |

|---------------------------|-----|-----|------------------------------------|--------------------------|--|--|--|

| RS2                       | RS1 | RS0 | $R/\overline{W} = 0$               | R/W = 1                  |  |  |  |

| 0                         | 0   | 0   | CR20 = 0 Write Control Register #3 | No Operation             |  |  |  |

|                           |     |     | CR20 = 1 Write Control Register #1 | No operation             |  |  |  |

| 0                         | 0   | 1   | Write Control Register #2          | Read Status Register     |  |  |  |

| 0                         | 1   | 0   | Write MSB Buffer Register          | Read Timer #1 Counter    |  |  |  |

| 0                         | 1   | 1   | Write Timer #1 Latches             | Read LSB Buffer Register |  |  |  |

| 1                         | 0   | 0   | Write MSB Buffer Register          | Read Timer #2 Counter    |  |  |  |

| 1                         | 0   | 1   | Write Timer #2 Latches             | Read LSB Buffer Register |  |  |  |

| 1                         | 1   | 0   | Write MSB Buffer Register          | Read Timer #3 Counter    |  |  |  |

| 1                         | 1   | 1   | Write Timer #3 Latches             | Read LSB Buffer Register |  |  |  |

CR10 — The least significant bit of Control Register #1 is used as an Internal Reset bit. When this bit is a logic zero, all timers are allowed to operate in the modes prescribed by the remaining bits of the control registers. Writing a "one" into CR10 causes all counters to be preset with the contents of the corresponding counter latches, all counter clocks to be disabled, and the timer outputs and interrupt flags (Status Register) to be reset. Counter Latches and Control Registers are undisturbed by an Internal Reset and may be written into regardless of the state of CR10.

The least significant bit of Control Register #3 is used as a selector for a +8 prescaler which is available with Timer #3 only. The prescaler, if selected, is effectively placed between

the clock input circuitry and the input to Counter #3. It can therefore be used with either the internal clock (Enable) or an external clock source.

#### NOTE

When initializing Timer 3 into the divide-by-eight mode on consecutive E-cycles (i.e., with DMA), Control Register 3 must be initialized before Timer Latch #3 to insure proper timer initialization.

**CR30** — The functions depicted in the foregoing discussions are tabulated in Table 2 for ease of reference.

TABLE 2 - CONTROL REGISTER BITS

Control Register Bits CR10, CR20, and CR30 are unique in that each selects a different function. The remaining bits (1 through 7) of each Control Register select common functions, with a particular Control Register affecting only its corresponding timer.

**CRX1** — Bit 1 of Control Register #1 (CR11) selects whether an internal or external clock source is to be used with Timer #1. Similarly, CR21 selects the clock source for Timer #2, and CR31 performs this function for Timer #3. The function of each bit of Control Register "X" can therefore be defined as shown in the remaining section of Table 2.

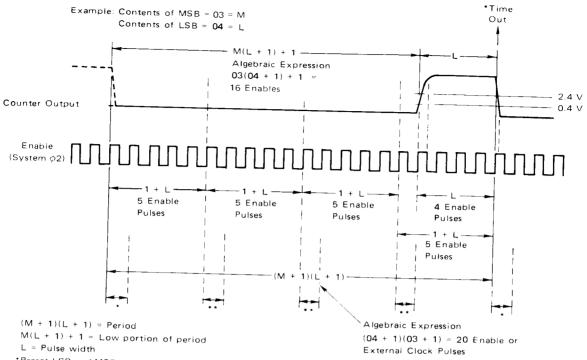

**CRX2** — Control Register Bit 2 selects whether the binary information contained in the Counter Latches (and subsequently loaded into the counter) is to be treated as a single 16-bit word or two 8-bit bytes. In the single 16-bit Counter Mode (CRX2=0) the counter will decrement to zero after N+1 enabled (G=0) clock periods, where N is defined as the 16-bit number in the Counter Latches. With CRX2=1, a similar Time Out will occur after (L+1)  $\cdot$  (M+1) enabled clock periods, where L and M, respectively, refer to the LSB and MSB bytes in the Counter Latches.

**CRX3-CRX7** — Control Register Bits 3, 4, and 5 are explained in detail in the Timer Operating Mode section. Bit 6 is an interrupt mask bit which will be explained more fully in conjunction with the Status Register, and bit 7 is used to enable the corresponding Timer Output. A summary of the control register programming modes is shown in Table 3.

#### STATUS REGISTER/INTERRUPT FLAGS

The MC6840 has an internal Read-Only Status Register which contains four Interrupt Flags. (The remaining four bits of the register are not used, and defaults to zeros when being read.) Bits 0, 1, and 2 are assigned to Timers 1, 2, and 3, respectively, as individual flag bits, while Bit 7 is a Composite Interrupt Flag. This flag bit will be asserted if any of the individual flag bits is set while Bit 6 of the corresponding Control Register is at a logic one. The conditions for asserting the composite Interrupt Flag bit can therefore be expressed as:

INT = I1 • CR16 + I2 • CR26 + I3 • CR36

where INT = Composite Interrupt Flag (Bit 7)

I1 = Timer #1 Interrupt Flag (Bit 0)

I2 = Timer #2 Interrupt Flag (Bit 1)

I3 = Timer #3 Interrupt Flag (Bit 2)

An interrupt flag is cleared by a Timer Reset condition, i.e., External RESET = 0 or Internal Reset Bit (CR10) = 1. It will also be cleared by a Read Timer Counter Command provided that the Status Register has previously been read while the interrupt flag was set. This condition on the Read Status Register-Read Timer Counter (RS-RT) sequence is designed to prevent missing interrupts which might occur after the status register is read, but prior to reading the Timer Counter.

An Individual Interrupt Flag is also cleared by a Write Timer Latches (W) command or a Counter Initialization (CI) sequence, provided that W or CI affects the Timer corresponding to the individual Interrupt Flag.

#### **COUNTER LATCH INITIALIZATION**

Each of the three independent timers consists of a 16-bit addressable counter and a 16-bit addressable latch. The counters are preset to the binary numbers stored in the latches. Counter initialization results in the transfer of the latch contents to the counter. See notes in Table 4 regarding the binary number N, L, or M placed into the Latches and their relationship to the output waveforms and counter Time-Outs.

Since the PTM data bus is 8-bits wide and the counters are 16-bits wide, a temporary register (MSB Buffer Register) is provided. This "write only" register is for the Most-Significant Byte of the desired latch data. Three addresses are provided for the MSB Buffer Register (as indicated in Table 1), but they all lead to the same Buffer. Data from the MSB Buffer will automatically be transferred into the Most-Significant Byte of Timer #X when a Write Timer #X Latches Command is performed. So it can be seen that the MC6840 has been designed to allow transfer of two bytes of data into the counter latches provided that the MSB is transferred first. The storage order must be observed to ensure proper latch operation.

In many applications, the source of the data will be an M6800 Family MPU. It should be noted that the 16-bit store operations of the M6800 family microprocessors (STS and STX) transfer data in the order required by the PTM. A Store Index Register Instruction, for example, results in the MSB of the X register being transferred to the selected address, then the LSB of the X register being written into the next higher location. Thus, either the index register or stack pointer may be transferred directly into a selected counter latch with a single instruction.

A logic zero at the RESET input also initializes the counter latches. In this case, all latches will assume a maximum count of 65,535<sub>10</sub>. It is important to note that an Internal

| CRX3 |   | RX4 |   | CRX5 TABLE 3 — PTM OPERATING MODE SELECTION                                                  |

|------|---|-----|---|----------------------------------------------------------------------------------------------|

|      | 0 | 0   | 0 | Continuous Operating Mode: Gate I or Write to Latches or Reset Causes Counter Initialization |

|      | 1 | 0   | 0 | Frequency Comparison Mode: Interrupt If Gate 🚩 🕌 is< Counter Time Out                        |

|      | 0 | 1   | 0 | Continuous Operating Mode: Gate I or Reset Causes Counter Initialization                     |

|      | 1 | 1   | 0 | Pulse Width Comparison Mode: Interrupt if Gate 🚩 📝 is< Counter Time Out                      |

|      | 0 | 0   | 1 | Single Shot Mode: Gate ↓ or Write to Latches or Reset Causes Counter Initialization          |

|      | 1 | 0   | 1 | Frequency Comparison Mode: Interrupt If Gate 🚩 🦵 is>Counter Time Out                         |

|      | 0 | 1   | 1 | Single Shot Mode: Gate I or Reset Causes Counter Initialization                              |

|      | 1 | 1   | 1 | Pulse Width Comparison Mode: Interrupt If Gate                                               |

Reset (Bit zero of Control Register 1 Set) has no effect on the counter latches.

#### COUNTER INITIALIZATION

Counter Initialization is defined as the transfer of data from the latches to the counter with subsequent clearing of the Individual Interrupt Flag associated with the counter. Counter Initialization always occurs when a reset condition (RESET = 0 or CR10 = 1) is recognized. It can also occur — depending on Timer Mode — with a Write Timer Latches command or recognition of a negative transition of the Gate input.

Counter recycling or re-initialization occurs when a negative transition of the clock input is recognized after the counter has reached an all-zero state. In this case, data is transferred from the Latches to the Counter.

#### ASYNCHRONOUS INPUT/OUTPUT LINES

Each of the three timers within the PTM has external clock and gate inputs as well as a counter output line. The inputs are high-impedance, TTL-compatible lines and ouputs are capable of driving two standard TTL loads.

CLOCK INPUTS (C1, C2, and C3) — Input pins C1, C2, and  $\overline{C3}$  will accept asynchronous TTL voltage level signals to decrement Timers 1, 2, and 3, respectively. The high and low levels of the external clocks must each be stable for at least one system clock period plus the sum of the setup and hold times for the clock inputs. The asynchronous clock rate can vary from dc to the limit imposed by the Enable Clock Setup, and Hold times.

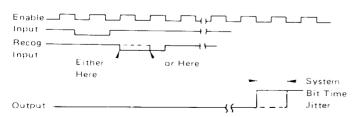

The external clock inputs are clocked in by Enable pulses. Three Enable periods are used to synchronize and process the external clock. The fourth Enable pulse decrements the internal counter. This does not affect the input frequency, it merely creates a delay between a clock input transition and internal recognition of that transition by the PTM. All references to C inputs in this document relate to internal recognition of the input transition. Note that a clock high or low level which does not meet setup and hold time specifications may require an additional Enable pulse for recognition. When observing recurring events, a lack of synchronization will result in "jitter" being observed on the output of the PTM when using asynchronous clocks and gate input signals. There are two types of jitter. "System jitter" is the result of the input signals being out of synchronization with Enable, permitting signals with marginal setup and hold time to be recognized by either the bit time nearest the input transition or the subsequent bit time.

"Input jitter" can be as great as the time between input signal negative going transitions plus the system jitter, if the first transition is recognized during one system cycle, and not recognized the next cycle, or vice versa. See Figure 9.

FIGURE 9 - INPUT JITTER

**CLOCK INPUT \overline{C3} (+8 PRESCALER MODE)** — External clock input  $\overline{C3}$  represents a special case when Timer #3 is programmed to utilize its optional +8 prescaler mode.

The divide-by-8 prescaler contains an asynchronous ripple counter; thus, input setup ( $t_{SU}$ ) and hold times ( $t_{hd}$ ) do not apply. As long as minimum input pulse widths are maintained, the counter will recognize and process all input clock ( $\overline{C3}$ ) transitions. However, in order to guarantee that a clock transition is processed during the current E cycle, a certain amount of synchronization time ( $t_{SYNC}$ ) is required between the  $\overline{C3}$  transition and the falling edge of Enable (see Figure 9). If the synchronization time requirement is not met, it is possible that the  $\overline{C3}$  transition will not be processed until the following E cycle.

The maximum input frequency and allowable duty cycles for the  $\pm 8$  prescaler mode are specified under the AC Operating Characteristics. Internally, the  $\pm 8$  prescaler output is treated in the same manner as the previously discussed clock inputs.

GATE INPUTS (G1, G2, G3) — Input pins G1, G2, and G3 accept asynchronous TTL-compatible signals which are used as triggers or clock gating functions to Timers 1, 2, and 3, respectively. The gating inputs are clocked into the PTM by the E (enable) clock in the same manner as the previously discussed clock inputs. That is, a Gate transition is recognized by the PTM on the fourth Enable pulse (provided setup and hold time requirements are met), and the high or low levels of the Gate input must be stable for at least one system clock period plus the sum of setup and hold times. All references to G transition in this document relate to internal recognition of the input transition.

The Gate inputs of all timers directly affect the internal 16-bit counter. The operation of  $\overline{G3}$  is therefore independent of the  $\pm 8$  prescaler selection.

TIMER OUTPUTS (01, 02, 03) — Timer outputs 01, 02, and 03 are capable of driving up to two TTL loads and produce a defined output waveform for either Continuous or Single-Shot Timer modes. Output waveform definition is accomplished by selecting either Single 16-bit or Dual 8-bit operating modes. The Single 16-bit mode will produce a square-wave output in the continuous mode and a single pulse in the single-shot mode. The Dual 8-bit mode will produce a variable duty cycle pulse in both the continuous and single-shot timer modes. One bit of each Control Register (CRX7) is used to enable the corresponding output. If this bit is cleared, the output will remain low (VOL) regardless of the operating mode. If it is cleared while the output is high the output will go low during the first enable cycle following a write to the Control Register.

The Continuous and Single-Shot Timer Modes are the only ones for which output response is defined in this data sheet. Refer to the Programmable Timer Fundamentals and Applications manual for a discussion of the output signals in other modes. Signals appear at the outputs (unless CRX7=0) during Frequency and Pulse Width comparison modes, but the actual waveform is not predictable in typical applications.

#### TIMER OPERATING MODES

The MC6840 has been designed to operate effectively in a wide variety of applications. This is accomplished by using three bits of each control register (CRX3, CRX4, and CRX5) to define different operating modes of the Timers. These modes are divided into WAVE SYNTHESIS and WAVE MEASUREMENT modes, and are outlined in Table 4.

TABLE 4 - OPERATING MODES

| Con  | troi Regi | ster                 | T 0                    |             |

|------|-----------|----------------------|------------------------|-------------|

| CRX3 | CRX4      | CRX5                 | Timer Operating Mode   |             |

| 0    | •         | 0                    | Continuous             | 0 .         |

| 0    | •         | 1                    | Single-Shot            | Synthesizer |

| 1    | 0         | Frequency Comparison |                        |             |

| 1    | 1         | •                    | Pulse Width Comparison | Measurement |

<sup>\*</sup>Defines Additional Timer Function Selection

One of the WAVE SYNTHESIS modes is the Continuous Operating mode, which is useful for cyclic wave generation. Either symmetrical or variable duty-cycle waves can be generated in this mode. The other wave synthesis mode, the Single-Shot mode, is similar in use to the Continuous operating mode, however, a single pulse is generated, with a programmable preset width.

The WAVE MEASUREMENT modes include the Frequency Comparison and Pulse Width Comparison modes which are used to measure cyclic and singular pulse widths, respectively.

In addition to the four timer modes in Table 4, the remaining control register bit is used to modify counter initialization and enabling or interrupt conditions.

#### WAVE SYNTHESIS MODES

**CONTINUOUS OPERATING MODE (TABLE 5)** — The continuous mode will synthesize a continuous wave with a period proportional to the preset number in the particular timer latches. Any of the timers in the PTM may be programmed to operate in a continuous mode by writing zeroes into bits 3 and 5 of the corresponding control register. Assuming

that the timer output is enabled (CRX7 = 1), either a square wave or a variable duty cycle waveform will be generated at the Timer Output, OX. The type of output is selected via Control Register Bit 2.

Either a Timer Reset (CR10=1 or External Reset = 0) condition or internal recognition of a negative transition of the Gate input results in Counter Initialization. A Write Timer latches command can be selected as a Counter Initialization signal by clearing CRX4.

The counter is enabled by an absence of a Timer Reset condition and a logic zero at the Gate input. In the 16-bit mode, the counter will decrement on the first clock cycle during or after the counter initialization cycle. It continues to decrement on each clock signal so long as G remains low and no reset condition exists. A Counter Time Out (the first clock after all counter bits = 0) results in the Individual Interrupt Flag being set and reinitialization of the counter.

In the Dual 8-bit mode (CRX2 = 1) (refer to the example in Figure 10 and Tables 5 and 6) the MSB decrements once for every full countdown of the LSB + 1. When the LSB = 0, the MSB is unchanged; on the next clock pulse the LSB is reset to the count in the LSB Latches, and the MSB is decremented by 1 (one). The output, if enabled, remains low during and after initialization and will remain low until the counter MSB is all zeroes. The output will go high at the beginning of the next clock pulse. The output remains high until both the LSB and MSB of the counter are all zeroes. At the beginning of the next clock pulse the defined Time Out (TO) will occur and the output will go low. In the Dual 8-bit mode the period of the output of the example in Figure 10 would span 20 clock pulses as opposed to 1546 clock pulses using the normal 16-bit mode.

A special time-out condition exists for the dual 8-bit mode (CRX2=1) if L=0. In this case, the counter will revert to a mode similar to the single 16-bit mode, except Time Out occurs after  $M+1^{\bullet}$  clock pulses. The output, if enabled, goes low during the Counter Initialization cycle and reverses state at each Time Out. The counter remains cyclical (is reinitialized at each Time Out) and the Individual Interrupt Flag is set when Time Out occurs. If M=L=0, the internal counters do not change, but the output toggles at a rate of ½ the clock frequency.

TABLE 5 - CONTINUOUS OPERATING MODES

| Synthesis | s Modes  |                        | NTINUOUS MODE<br>RX3 = 0, CRX5 = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|----------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control   | Register |                        | Initialization/Output Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CRX2      | CRX4     | Counter Initialization | *Timer Output (OX) (CRX7 = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0         | 0        | G.+W+R                 | -(N+1)(T) + (N+1)(T) - (N+1)(T) |

| 0         | 1        | G,+R                   | 10 TO TO TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1         | 0        | G.+W+R                 | (L+1)(M+1)(T) (L+1)(M+1)(T) V <sub>OH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1         | 1        | G:+R                   | (L)(T) - V <sub>OL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## TABLE 8 - FREQUENCY COMPARISON MODE

| Mode        | Bit 3        | Bit 4          | Control Reg.<br>Bit 5 | Counter<br>Initialization | Counter Enable<br>Flip-Flop Set (CE) | Counter Enable       | Interrupt Flag |

|-------------|--------------|----------------|-----------------------|---------------------------|--------------------------------------|----------------------|----------------|

| Frequency   | 1            | 0              | 0                     | GI . (CE+TO)+R            | GI•W•B•I                             | Flip-Flop Reset (CE) | Set (I)        |

| Comparison  | 1            | 0              | 1                     | GI•T+R                    |                                      | W+R+1                | GI Before TO   |

| Pulse Width | 1            | <del>-</del> - | <u> </u>              |                           | GI•W•R•Ī                             | W + R + I            | TO Before GI   |

| Comparison  | <del>-</del> | 1              | - 0                   | GI•T+R                    | GIW•R•T                              | W + R + I + G        | G1 Before TO   |

| Companson   |              |                | 11                    | GI•Ī+R                    | GI•W•R•T                             | W + R + I + G        | TO Before Gt   |

$\overline{\mathsf{GI}}$  = Negative transition of Gate input.

W = Write Timer Latches Command.

R = Timer Reset (CR10 = 1 or External RESET = 0)

N = 16-Bit Number in Counter Latch.

TO = Counter Time Out (All Zero Condition)

! = Interrupt for a given timer

\*All time intervals shown above assume the Gate  $(\overline{G})$  and Clock  $(\overline{C})$  signals are sycnhronized to the system clock (E) with the specified setup and hold time requirements.

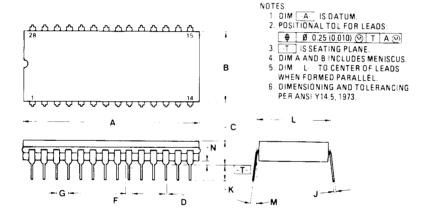

#### **MECHANICAL DATA**

#### ORDERING INFORMATION

| Package Type        | Frequency                                           | Temperature<br>Range                                                            | Order Number                                             |

|---------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------|

| Plastic<br>P Suffix | 1.0 MHz<br>1.0 MHz<br>1.5 MHz<br>1.5 MHz<br>2.0 MHz | 0°C to 70°C<br>-40°C to +85°C<br>0°C to 70°C<br>-40°C to +85°C<br>0°C to 70°C   | MC6840P<br>MC6840CP<br>MC68A40P<br>MC68A40CP<br>MC68B40P |

| Cerdip<br>S Suffix  | 1.0 MHz<br>1.0 MHz<br>1.5 MHz<br>1.5 MHz<br>2.0 MHz | 0°C to 70°C<br>- 40°C to +85°C<br>0°C to 70°C<br>- 40°C to +85°C<br>0°C to 70°C | MC6840S<br>MC6840CS<br>MC68A40S<br>MC68A40CS<br>MC68B40S |

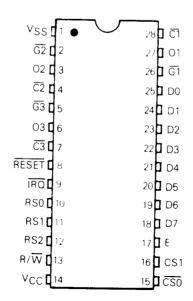

## **PIN ASSIGNMENT**

The three differences between Single-Shot and Continous Timer Mode can be summarized as attributes of the Single-Shot mode:

- Output is enabled for only one pulse until it is reinitialized.

- 2. Counter Enable is independent of Gate.

- 3. L = M = 0 or N = 0 disables output.

Aside from these differences, the two modes are identical.

#### WAVE MEASUREMENT MODES

**TIME INTERVAL MODES** — The Time Interval Modes are the Frequency (period) Measurement and Pulse Width Comparison Modes, and are provided for those applications which require more flexibility of interrupt generation and Counter Initialization. Individual Interrupt Flags are set in these modes as a function of both Counter Time Out and transitions of the Gate input. Counter Initialization is also affected by Interrupt Flag status.

A timer's output is normally not used in a Wave Measurement mode, but it is defined. If the output is enabled, it will operate as follows. During the period between reinitialization of the timer and the first Time Out, the output will be a logical zero. If the first Time Out is completed (regardless of its method of generation), the output will go high. If further TO's occur, the output will change state at each completion of a Time-Out.

The counter does operate in either Single 16-bit or Dual 8-bit modes as programmed by CRX2. Other features of the Wave Measurement Modes are outlined in Table 7.

Frequency Comparison Or Period Measurement Mode (CRX3=1, CRX4=0) — The Frequency Comparison Mode with CRX5=1 is straightforward. If Time Out occurs prior to the first negative transition of the Gate input after a Counter Initialization cycle, an Individual Interrupt Flag is set. The counter is disabled, and a Counter Initialization cycle cannot begin until the interrupt flag is cleared and a negative transition on  $\overline{G}$  is detected.

If CRX5=0, as shown in Tables 7 and 8, an interrupt is generated if Gate input returns low prior to a Time Out. If a Counter Time Out occurs first, the counter is recycled and continues to decrement. A bit is set within the timer on the initial Time Out which precludes further individual interrupt

generation until a new Counter Initialization cycle has been completed. When this internal bit is set, a negative transition of the Gate input starts a new Counter Initialization cycle. (The condition of G1-1-TO is satisfied, since a Time Out has occurred and no individual Interrupt has been generated.)

Any of the timers within the PTM may be programmed to compare the period of a pulse (giving the frequency after calculations) at the Gate input with the time period requested for Counter Time Out. A negative transition of the Gate Input enables the counter and starts a Counter Initialization cycle — provided that other conditions, as noted in Table 8, are satisfied. The counter decrements on each clock signal recognized during or after Counter Initialization until an Interrupt is generated, a Write Timer Latches command is issued, or a Timer Reset condition occurs. It can be seen from Table 8 that an interrupt condition will be generated if CRX5=0 and the period of the pulse (single pulse or measured separately repetitive pulses) at the Gate input is less than the Counter Time Out period. If CRX5=1, an interrupt is generated if the reverse is true.

Assume now with CRX5=1 that a Counter Initialization has occurred and that the Gate input has returned low prior to Counter Time Out. Since there is no Individual Interrupt Flag generated, this automatically starts a new Counter Initialization Cycle. The process will continue with frequency comparison being performed on each Gate input cycle until the mode is changed, or a cycle is determined to be above the predetermined limit.

Pulse Width Comparison Mode (CRX3=1, CRX4=1) — This mode is similar to the Frequency Comparison Mode except for a positive, rather than negative, transition of the Gate input terminates the count. With CRX5=0, an Individual Interrupt Flag will be generated if the zero level pulse applied to the Gate input is less than the time period required for Counter Time Out. With CRX5=1, the interrupt is generated when the reverse condition is true.

As can be seen in Table 8, a positive transition of the Gate input disables the counter. With CRX5=0, it is therefore possible to directly obtain the width of any pulse causing an interrupt. Similar data for other Time Interval Modes and conditions can be obtained, if two sections of the PTM are dedicated to the purpose.

FIGURE 7 - OUTPUT DELAY

|      | CRX3 = 1 |                        |                                                                                      |  |  |  |  |

|------|----------|------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| CRX4 | CRX5     | Application            | Condition for Setting Individual Interrupt Flag                                      |  |  |  |  |

| 0    | 0        | Frequency Comparison   | Interrupt Generated if Gate Input Period (1/F) is less than Counter Time Out (TO)    |  |  |  |  |

| 0    | 1        | Frequency Comparison   | Interrupt Generated if Gate Input Period (1/F) is greater than Counter Time Out (TO) |  |  |  |  |

| 1    | 0        | Pulse Width Comparison | Interrupt Generated if Gate Input "Down Time" is less than Counter Time Out (TO)     |  |  |  |  |

| 1    | 1        | Pulse Width Comparison | Interrupt Generated if Gate Input "Down Time" is greater than Counter Time Out (TO)  |  |  |  |  |

## FIGURE 10 — TIMER OUTPUT WAVEFORM EXAMPLE (Continuous Dual 8-Bit Mode Using Internal Enable)

\*Preset LSB and MSB to Respective Latches on the negative transition of the Enable

\*\*Preset LSB to LSB Latches and Decrement MSB by one on the negative transition of the Enable

The discussion of the Continuous Mode has assumed that the application requires an output signal. It should be noted that the Timer operates in the same manner with the output disabled (CRX7=0). A Read Timer Counter command is valid regardless of the state of CRX7

${f SINGLE-SHOT\ TIMER\ MODE}-{f This\ mode\ is\ identical\ to}$ the Continuous Mode with three exceptions. The first of these is obvious from the name - the output returns to a low level after the initial Time Out and remains low until another Counter Initialization cycle occurs

As indicated in Table 6, the internal counting mechanism remains cyclical in the Single-Shot Mode. Each Time Out of the counter results in the setting of an Individual Interrupt Flag and re-initialization of the counter.

The second major difference between the Single-Shot and Continuous modes is that the internal counter enable is not dependent on the Gate input level remaining in the low state for the Single-Shot mode.

Another special condition is introduced in the Single-Shot mode. If L = M = 0 (Dual 8-bit) or N = 0 (Single 16-bit), the output goes low on the first clock received during or after Counter Initialization. The output remains low until the Operating Mode is changed or nonzero data is written into the Counter Latches. Time Outs continue to occur at the end of each clock period.

TABLE 6 - SINGLE-SHOT OPERATING MODES

| Synthe           | cic Modes |                                 |                            |  |  |  |

|------------------|-----------|---------------------------------|----------------------------|--|--|--|

| Synthesis Modes  |           | SINGLE-SHOT MODE                |                            |  |  |  |

|                  |           |                                 | CRX7 = 1, CRX5 = 1)        |  |  |  |

| Control Register |           | Initialization/Output Waveforms |                            |  |  |  |

| CRX2             | CRX4      | Counter Initialization          | Timer Output (OX)          |  |  |  |

| 0                | 0         | G.+W+R                          | (N+1)(T) (N+1)(T) (N+1)(T) |  |  |  |

| 0                | 1         | Ğı+R                            | 10 10                      |  |  |  |

| 1                | 0         | G.+W+R                          | (L+1)(M+1)(T)              |  |  |  |

| 1                | 1         | Gı+R                            | TO TO                      |  |  |  |

Symbols are as defined in Table 5.

#

#### NOTES:

- 1. POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25mm(0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

- 2. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- DIMENSION B DOES NOT INCLUDE MOLD FLASH.

P SUFFIX

PLASTIC PACKAGE

CASE 710-02

|     | MILLIN   | ETERS | INCHES    |                 |

|-----|----------|-------|-----------|-----------------|

| DIM | MIN      | MAX   | MIN       | MAX             |

| Α   | 36.45    | 37.21 | 1.435     | 1.465           |

| В   | 13.72    | 14.22 | 0.540     | 0.560           |

| C   | 3.94     | 5.08  | 0.155     | 0.200           |

| D   | 0.36     | 0.56  | 0.014     | 0.022           |

| F   | 1.02     | 1.52  | 0.040     | 0.060           |

| G   | 2.54 BSC |       | 0.100 BSC |                 |

| Н   | 1.65     | 2.16  | 0.065     | 0.085           |

| J   | 0.20     | 0.38  | 0.008     | 0.015           |

| K   | 2.92     | 3.43  | 0.115     | 0.135           |

| L   | 15.24    | BSC   | 0.600     | BSC             |

| М   | 00       | 150   | 00        | 15 <sup>0</sup> |

| N   | 0.51     | 1.02  | 0.020     | 0.040           |

#### S SUFFIX CERDIP PACKAGE CASE 733-01

|     | MILLIN    | ETERS | INCHES    |                 |  |

|-----|-----------|-------|-----------|-----------------|--|

| DIM | MIN       | MAX   | MIN       | MAX             |  |

| Α   | 36.45     | 37.85 | 1.435     | 1.490           |  |

| В   | 12.70     | 15.37 | 0.500     | 0.605           |  |

| С   | 4.06      | 5.84  | 0.160     | 0.230           |  |

| D   | 0.38      | 0.56  | 0.015     | 0.022           |  |

| F   | 1.27      | 1.65  | 0.050     | 0.065           |  |

| G   | 2.54      | BSC   | 0.100 BSC |                 |  |

| J   | 0.20      | 0.30  | 0.008     | 0.012           |  |

| K   | 2.54      | 4.06  | 0.100     | 0.160           |  |

| L   | 15.24 BSC |       | 0.600 BSC |                 |  |

| М   | 50        | 150   | 50        | 15 <sup>0</sup> |  |

| N   | 0.51      | 1.27  | 0.020     | 0.050           |  |

|     |           |       |           |                 |  |

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/Affirmative Action Employer.

#### Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. EUROPE: Motorola Ltd.; European Literature Center; 88 Tanners Drive, Blakelands Milton Keynes, MK145BP, England. ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; P.O. Box 80300; Cheung Sha Wan Post Office; Kowloon Hong Kong.