## STV9211

# 150 MHz PIXEL VIDEO CONTROLLER FOR MONITORS IN DC-COUPLING MODE

#### **FEATURES**

- 150 MHz Pixel Rate

- 2.7 ns Rise and Fall Time

- I<sup>2</sup>C Bus Controlled

- Support DC Coupling Application only

- Brightness Selection (after or before Drive)

- Grey Scale Tracking Versus Brightness

- InfraBlack Range Selection 1.3 or 1.8V

(i.e: 26 or 36V in kit with STV95xx amplifier)

- InfraBlack Offset Selection 0.4 to 2.2V

(i.e: 115 to 80V in kit with STV95xx amplifiers)

- OSD Mixing

- Beam Current Attenuation (ABL)

- Pedestral Clamping on Output Stage

- Possibility of Light or Dark Grey OSD Background

- OSD Contrast Control

- Input Black Level Clamping with Built-in Clamping Pulse

- 5 V to 8 V Power Supply

- Perfectly matched with the STV95xx ST Amplifier Family

- Preamplifier Control (bandwidth and stand-by)

- Amplifier Control (bandwidth and stand-by), only applicable to amplifiers with CTL pin or STDBY pins.

#### **DESCRIPTION**

The STV9211 is an I<sup>2</sup>C Bus controlled RGB preamplifier designed for Monitor applications, able to mix the RGB signals coming from any OSD device. The usual Contrast, Brightness, Drive and Cut-Off (InfraBlack) Controls are provided.

In addition, it includes the following features:

- High resolution cut-off (InfraBlack) adjustment,

- OSD contrast.

- Bandwidth and stand-by control,

- Brightness before/after Drive Selection.

DIP20 (Plastic Package)

ORDER CODE:

The RGB incoming signals are amplified and shaped to drive in DC coupling the video amplifier without intermediate follower stages.

One of the main advantages of ST devices is their ability to sink and source currents.

These driving capabilities combined with an original output stage structure suppress any static current on the output pins and therefore reduce dramatically the power dissipation of the device.

Extensive integration combined with high performance and advanced features make the STV9211 one of the best choice for any CRT monitor.

Perfectly matched with the ST video amplifiers STV95xx, they offer a complete solution for high performance and cost-optimized Video Board Application.

February 2002 ADCS 7244743 Version 4.0 1/38

# **Table of contents**

| Chapter 1  | Pin connection, pin description                        | 6          |

|------------|--------------------------------------------------------|------------|

| 1.1        | Pin connection                                         | 6          |

| 1.2        | Pin description                                        | 6          |

| Chapter 2  | Functional description                                 | 8          |

| 2.1        | RGB input, clamping function                           | 8          |

| 2.2        | Fast blanking input                                    | 9          |

| 2.3        | Blanking input                                         | 9          |

| 2.4        | Contrast adjustment (8 bits)                           | 10         |

| 2.5        | Brightness/Drive selection (1 bit)                     | 11         |

| 2.6        | Drive adjustment (3 x 8 bits)                          | 11         |

| 2.7        | Brightness adjustment (8 bits)                         | 12         |

| 2.8        | Cut-off adjustment, Infra-black level (Vib) (3x8 bits) | 13         |

| 2.9        | ABL Control                                            | 15         |

| 2.10       | OSD                                                    |            |

| 2.11       | Output stage                                           | 17         |

| 2.12       | Preamplifier bandwidth adjustment (4 bits)             | 18         |

| 2.13       | Amplifier bandwidth adjustment (7 bits)                | 18         |

| 2.14       | CRT cathode, DC-coupling mode (Figure 14)              | 19         |

| 2.15       | Preamplifier stand-by mode                             | 19         |

| 2.16       | Amplifier stand-by mode                                | 19         |

| 2.17       | Serial interface                                       | 20         |

| 2.18       | Power-on reset                                         | 20         |

| 2.19       | Specific application conditions                        | 21         |

| Chapter 3  | Absolute maximum ratings                               | 22         |

| Chapter 4  | Thermal data                                           | 22         |

| Chapter 5  | DC electrical characteristics                          | 23         |

| Chapter 6  | AC electrical characteristics                          | 24         |

| Chapter 7  | I2C electrical characteristics                         | 26         |

| 2/38 STMid | croelectronics Confidential ADCS 7244743               | <b>577</b> |

### STV9211

| Chapter 8  | I2C interface timing requirements          |    |

|------------|--------------------------------------------|----|

| Chapter 9  | I2C register description                   | 27 |

| Chapter 10 | STV9211 + STV9556/55/53 applications hints | 30 |

| 10.1       | InfraBlack adjustment procedure (Cut-off)  | 30 |

| 10.2       | Preamplifier bandwidth register            | 32 |

| 10.3       | Preamplifier output network                | 32 |

| 10.4       | White balance adjustment                   | 32 |

| Chapter 11 | Internal schematics                        | 33 |

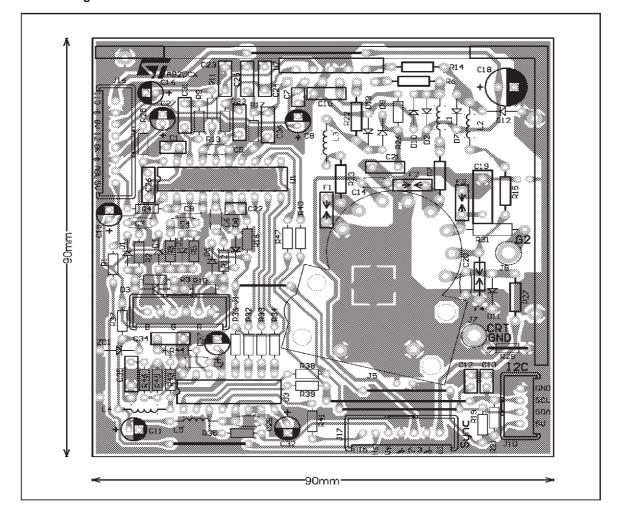

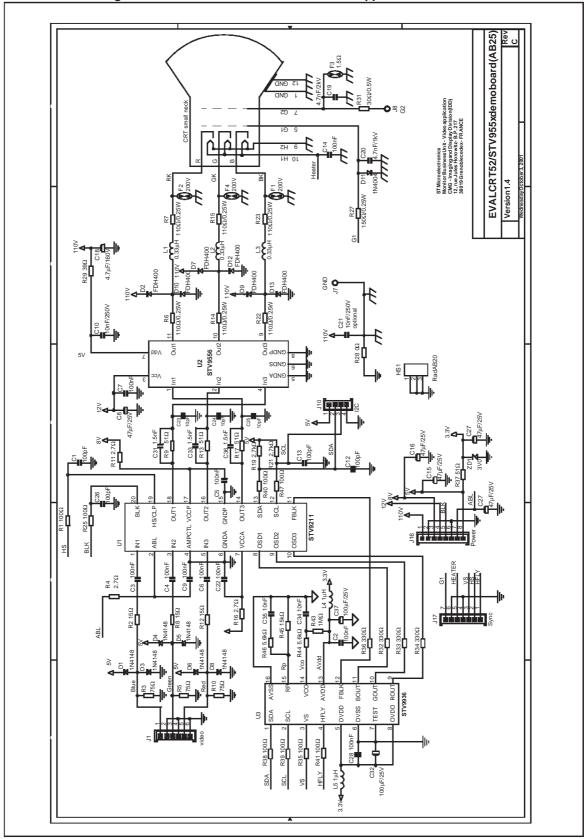

| Chapter 12 | Demonstration boards                       | 35 |

| Chapter 13 | Package mechanical data                    |    |

# **Revision follow-up**

#### **Target specification**

| December 2000    | version 1.0 | document created                                                                                                                                                                      |

|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 2001     | version 1.1 | reformatted with ST new corporate template                                                                                                                                            |

| January 2001     | version 1.2 | General update - replacement of some figures , - correction and addition of registers First ADCS release                                                                              |

| April 2001       | version 1.3 | General update - replacement of some figures , - correction of text, - addition of sections                                                                                           |

| June 2001        | version 1.4 | General update and addition of: - chapter 10: Application hints, - chapter 11: Internal, schematics, - chapter 12: application boards                                                 |

| Product preview  |             |                                                                                                                                                                                       |

| October 2001     | version 2.0 | General update: - replacement of some figures, - addition of sections : cut-off adjustment, - addition of figures (I2C, Cut-off adjustment) - TDA95xx salestype replaced with STV95xx |

| Preliminary data |             |                                                                                                                                                                                       |

| December 2001    | version 3.0 | General update                                                                                                                                                                        |

# Datasheet

January 2002 version 4.0

section 1.2: pin description modified for IN1, IN2, IN3, OSD1, OSD2, OSD3 and OUT1, OUT2, OUT3: replaced with video input, OSD input, Video output (channel 1, red), (channel 2, green), (channel 3, blue) respectively

Block diagram replaced

- figures replaced

section 2.3 Blanking input added

- Cut-off replaced with Infra-Black

Section 2.8 - Cut-off adjustment: Tables 1 and 2 gathered into table 1

Section 2.12 - preamplifier bandwidth adjustment (4 bits) instead of 3

bits previously

Chapter 10 - Application hints

tables 9 and 10 replaced with table 1

Cross reference to AN1445 replaced with AN1510

# 1 PIN CONNECTION, PIN DESCRIPTION

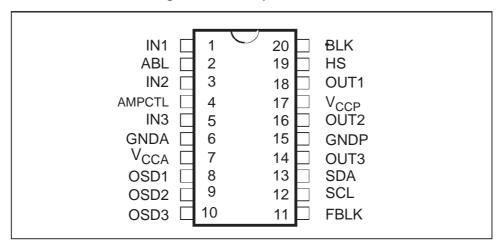

#### 1.1 Pin connection

Figure 1: STV9211 pin connection

### 1.2 Pin description

| Pin number | symbol           | description                                                                                             |

|------------|------------------|---------------------------------------------------------------------------------------------------------|

| 1          | IN1              | Video input (channel 1, red)                                                                            |

| 2          | ABL              | ABL input                                                                                               |

| 3          | IN2              | Video input (channel 2, green)                                                                          |

| 4          | AMPCTL           | Amplifier control (bandwidth and stand-by). Only applicable with amplifiers with the CTL or STDBY pins. |

|            |                  | To be connected to ground if not used.                                                                  |

| 5          | IN3              | Video input (channel 3, blue)                                                                           |

| 6          | GNDA             | Analog ground                                                                                           |

| 7          | V <sub>CCA</sub> | Analog supply (5V)                                                                                      |

| 8          | OSD1             | OSD input (channel 1, red)                                                                              |

| 9          | OSD2             | OSD input (channel 2, green)                                                                            |

| 10         | OSD3             | OSD input (channel 3, blue)                                                                             |

| 11         | FBLK             | Fast blanking                                                                                           |

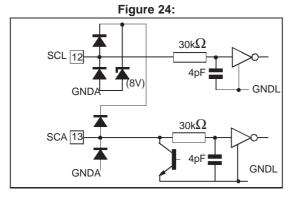

| 12         | SCL              | SCL                                                                                                     |

| 13         | SDA              | SDA                                                                                                     |

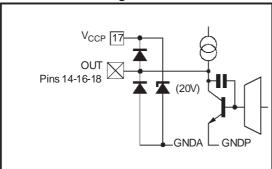

| 14         | OUT3             | Video output (channel 3, blue)                                                                          |

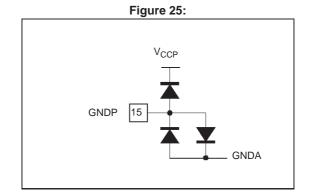

| 15         | GNDP             | Power ground                                                                                            |

| 16         | OUT2             | Video output (channel 2, green)                                                                         |

| 17         | V <sub>CCP</sub> | Output stage supply (5 V to 8 V)                                                                        |

| 18         | OUT1             | Video output (channel 1, red)                                                                           |

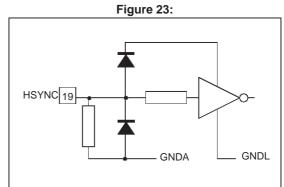

| 19         | HS               | Horizontal synchro or BPCP pulse                                                                        |

| 20         | BLK              | Blanking input                                                                                          |

CTL or STDBY TDA95xx Amplifier GND AMPCTL OUT2 OUT3 OCL Generator (\*) \* Stand-by: On/Off \* Bandwidth (3-bit) Amplifier control InfraBlack Adjustment (\*\*) (Cut-off) Output Stage VCCP 17 \* Range: 1.3 & 1.8V \* Offset (3-bit) \* Adjustment (8-bit) GND 9 0 3V (DC) OSD Contrast 4-bit OSD3 PreAmplifier Stand-by Drive 8-bit **Green Channel** Blue Channel OSD2 (\*\*) See Cut-off adjustment section for complete Cut-off register description Brightness 8-bit **Red Channel** V CCA (\*) See RGB input section for complete BPCP and OCL description OSD1 **O** R13-bit6 BLK H = 1 SCL I C Bus Decoder Contrast 8-bit SDA 20 RK TDA9211 BPCP (\*) 운 6 Ξ

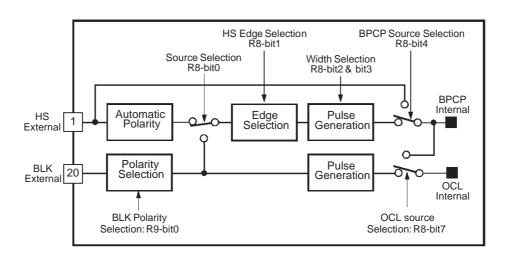

Figure 2: Block diagram

### 2 FUNCTIONAL DESCRIPTION

### 2.1 RGB input, clamping function

The three RGB inputs have to be supplied with a video signal (maximum peak-to-peak value = 1V) through coupling capacitors (100 nF typ.).

The RGB inputs include a clamping function using the input serial capacitor as "memory capacitor". To avoid the discharge of this capacitor during the line (due to leakage current), the input voltage is referenced to the ground.

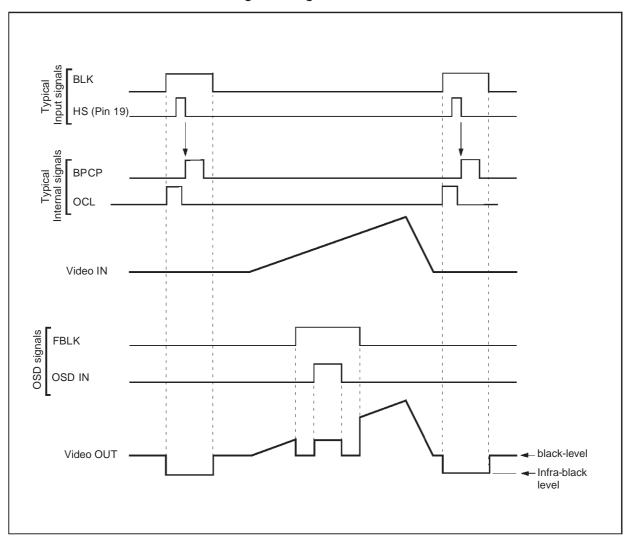

This clamping function is gated by the BPCP pulse (Black Porch Clamping Pulse) which is internally generated (see *Figure 4*). The Register 8 allows to choose the way to generate this BPCP (see *Figure 3* and *Figure 4*).

- Synchronization: HS or BLK signal (Register 8, bit0)

- Polarity: Positive or negative (Automatic detection) when synchronized by HS

Positive or negative (programmed via Register 9, bit 0) when

synchronized by BLK - see Note 1

- Edge: Trailing or Leading (Register 8, bit1)

- Width: From 0.33μs to 1.33μs (Register 8, bit2 and bit3)

- Direct BPCP: If the application provides the BPCP, one can program the direct

connection between Pin 19 and the internal BPCP (Register 8, bit4)

Note 1: When BPCP is synchronized by BLK, the leading edge of the BLK must be selected to get a proper synchronization.

Figure 3: BPCP selection of synchronization edge

| Synchronization source | Edge selection            | BPCP generation              |  |  |

|------------------------|---------------------------|------------------------------|--|--|

| нѕ                     | Trailing<br>(R8, bit 1=0) | HS (Pin 19) Internal BPCP    |  |  |

| (R8, bit 0=0)          | Leading<br>(R8, bit 1=1)  | HS (Pin 19) Internal BPCP    |  |  |

| BLK<br>(R8, bit 0=1)   | Leading (R8, bit 1=0)     | BLK (Pin 20) Internal BPCP   |  |  |

| HS<br>(R8, bit 4=1)    | _                         | HS (Pin 19) Internal BPCP=HS |  |  |

Figure 4: BPCP and OCL generation

### 2.2 Fast blanking input

The fast blanking pin (FBLK) is TTL compatible.

The blanking pulse can be:

- positive or negative

- line or Composite-type (but not Frame-type).

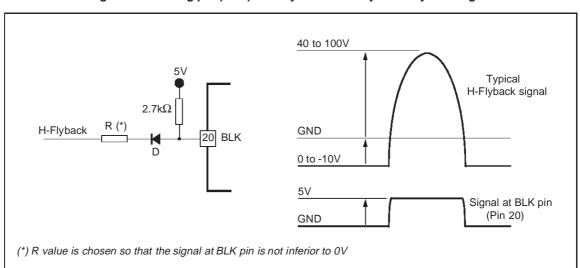

### 2.3 Blanking input

The blanking pin (BLK) is TTL compatible. A 5 V logical pulse generally supplies the BLK pin and defines the Infra-black level (see Signal waveform, *Figure 12*).

It is also possible to apply the H-Flyback signal directly to the BLK pin by using a simple circuitry, as shown in *Figure 5*.

Figure 5: Blanking pin (BLK) directly controlled by the H-flyback signal

### 2.4 Contrast adjustment (8 bits)

The contrast is adjusted simultaneously on, the 3 RGB channels via three internal amplifiers delivering a 48dB attenuation range (see Register 1,  $I^2C$  table 1 and *Figure 6*).

BLK Output Black level ← InfraBlack level Register name / address min / max Number step / resolution Adjustment Channel attenuation 3 channels 256 (8 bit) / 0,19 dB CRT / 01 0 / - 48 dB **Contrast** Simultaneously

Figure 6: Contrast adjustment

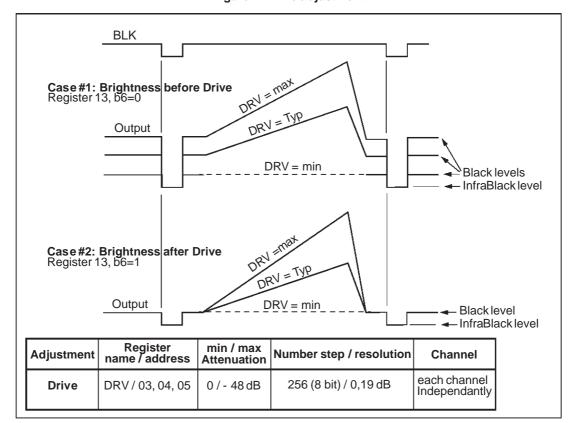

### 2.5 Brightness/Drive selection (1 bit)

The brightness position is selectable by I<sup>2</sup>C (Register 13, bit6. See I<sup>2</sup>C table 4).

There are 2 cases:

bit6=0 The brightness is located before the Drive (as for the TDA9210).

The advantage is to keep the "White balance" tracking when

changing the brightness level.

bit6=1 The brightness is located after the Drive.

The advantage is to perform the "White balance" tracking faster

(typically one adjustment less than in the previous case)

### **2.6 Drive adjustment** (3 x 8 bits)

In order to perform the "White balance" adjustment, the gain of the three RGB signals are adjustable separately via the three Drive amplifiers (Registers 3, 4 and 5, I<sup>2</sup>C table 1).

The very large range of the Drives (48 dB) allows different standards or custom color temperatures.

It can also be used to adjust the output voltages at the optimum amplitude to drive the CRT drivers, keeping the whole contrast control for the end-user only.

Figure 7: Drive adjustment

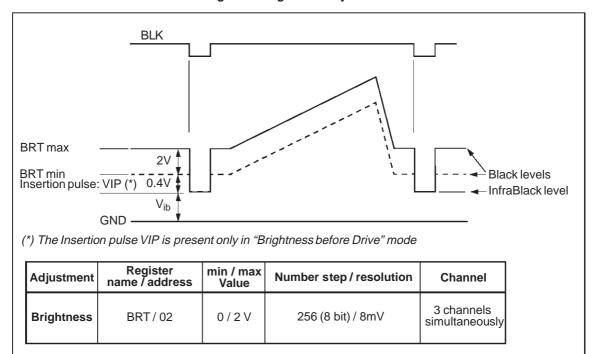

### 2.7 Brightness adjustment (8 bits)

Brightness adjustment is controlled by Register 2 (I<sup>2</sup>C table 1). It consists of adding the same DC voltage (BRT) to the three RGB signals. This DC voltage can be adjusted between 0 and 2V, outside the blanking pulse with 8mV adjustment steps (see *Figure 8*).

Inside the blanking pulse the DC output level is forced to the "Infra Black" level (Vib).

Figure 8: Brightness adjustment

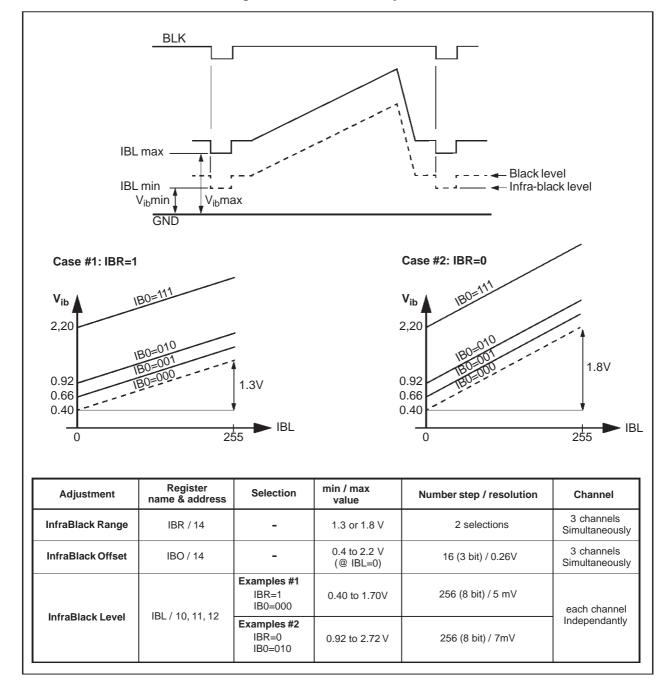

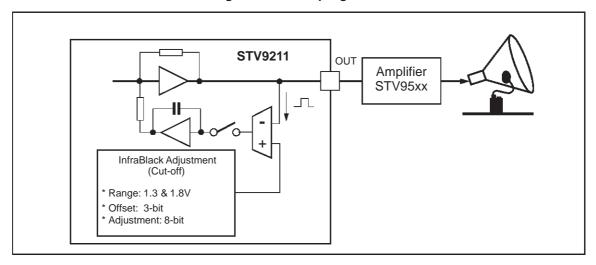

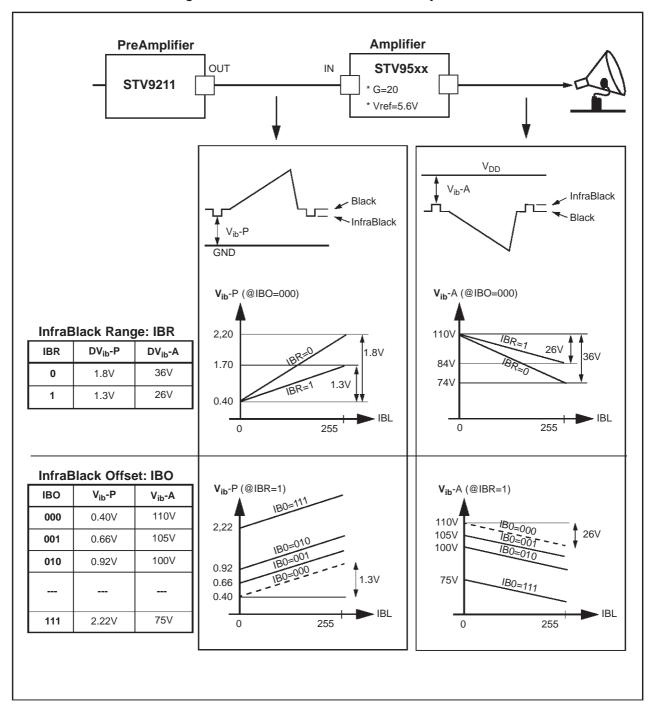

### 2.8 Cut-off adjustment, Infra-black level (Vib) (3x8 bits)

The Infra-black level (Vib) is the output voltage during the blanking time (BLK). This level is sampled after each line (sample - and - hold block) during an internal pulse (OCL) which is generated during the blanking pulse (see *Figure 4*).

The STV9211 allows to adjust independantly the cut-off levels of the 3 video outputs with a high resolution. This is done via 3 registers (IBR, IBO and IBL) programming respectively:

- the range: 1.3 or 1.8V (i.e: 26 or 36V in kit with the STV95xx amplifiers)

- the offset (to keep the video signal inside thelinear area)

- the level.

#### Infra-black range register (IBR: Register 14, bit 0. See I C table 6)

This register must be selected first, either to 1.3V to get a 26V Cut-off adjustment range with the STV95xx amplifier or to 1.8V to get a 36V range (see *Figure 9*)

#### Infra-black offset register (IBO: Register 14, bit 1, 2 & 3. See I C table 6)

This register select the Vib offset. It allows to keep the video signal inside the linearity area of the amplifier.

The value of this register depends on the amplifier high voltage supply (Vdd).

In kit with the STV95xx amplifier family, we recommend the following programming:

| Vdd (±5%)    | Case 1:<br>Brightness before Drive |         | Cas<br>Brightness | e 2:<br>after Drive |

|--------------|------------------------------------|---------|-------------------|---------------------|

|              | Binary                             | Decimal | Binary            | Decimal             |

| 112 to 115V  | 001                                | 1       | 011               | 3                   |

| 107 to 111V  | 010                                | 2       | 100               | 4                   |

| 102 to 106V  | 011                                | 3       | 101               | 5                   |

| 97 to 101V   | 100                                | 4       | 110               | 6                   |

| 92 to 96V    | 101                                | 5       | 111               | 7                   |

| 88 to 91     | 110                                | 6       | 111               | 7                   |

| 87 and below | 111                                | 7       | 111               | 7                   |

Table 1: Setting of the infra-black offset register (IBO)

#### Example:

For Vdd=101V +/-5% and Brightness before Drive, IBO must be set to 100.

#### Infra-black level register (IBL: Register 10, 11, 12. See I C table 1)

These three 8 bit- registers adjust independantly the infra-black level of the 3 outputs with a high resolution (typically 100mV at 26V range or 140mV at 36V range).

Figure 9: Infra-black level adjustment

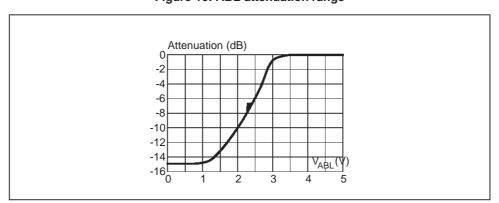

### 2.9 ABL Control

The STV9211 includes an ABL (automatic beam limitation) input to attenuate the RGB Video signals depending on the beam intensity.

The operating range is 2 V (from 3 V to 1 V). A typical 15 dB maximum attenuation is applied to the output signal whatever the contrast adjustment is. (See *Figure 10*).

When not used, the ABL input (Pin 2) must be connected to a 5 V supply voltage.

Figure 10: ABL attenuation range

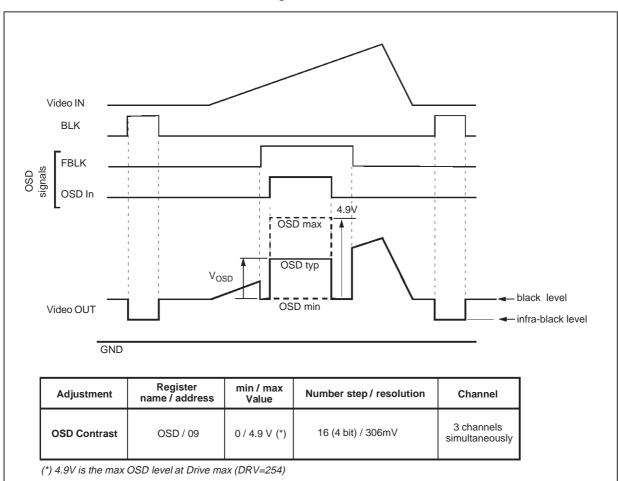

#### 2.10 OSD

#### **Principle**

The STV9211 allows to mix the OSD signals into the RGB main picture. The four pins dedicated to this function are the following:

- Three TTL RGB inputs (Pins 8, 9, 10) connected to the three outputs of the corresponding OSD processor.

- One TTL fast blanking input (Pin 11) also connected to the FBLK output of the OSD processor.

When a high level is present on the FBLK, the IC acts as follows:

- The three main picture RGB input signals (IN1, IN2, IN3) are internally switched to an internal clamp reference voltage.

- The three output signals (OUT1, OUT2, OUT3) are set to the voltage corresponding to the three OSD input logic states (0 or 1). (See Figure 2: Block diagram).

#### **Output level**

If the OSD input is set to 0, the output is set to the black level (see *Figure 11*).

If the OSD input is at high level, the output voltage is set to: black-level +  $V_{OSD}$ , where  $V_{OSD}$  is the  $I^2C$  bus-controlled voltage, adjustable between 0 V to 4.9 V by 306 mV steps via Register 7 (4 bits).

The same variation is applied simultaneously to the three channels providing the OSD contrast.

#### **Grey OSD**

The STV9211 allows the display of grey OSD by programming the following conditions:

- OSD1 = 1, OSD2 = 0 and OSD3 = 1,

- Register 9, bit 5 or 6 = 1.

If Register 9, bit 5 =1: a light grey OSD is displayed.

If Register 9, bit 6 = 1: a dark grey OSD is displayed.

If Register 9, bit 5=0 and bit 6=0: a standard OSD is displayed.

Figure 11: OSD

### 2.11 Output stage

The overall waveforms of the output signal are shown in *Figure 12*. The three output stages are large bandwidth output amplifiers able to deliver up to 4.4 V<sub>PP</sub> for 0.7 V<sub>PP</sub> video signal.

When a high level is applied on the BLK input (Pin 20), the three outputs are forced to "Infra Black" level (Vib) thanks to a sample and hold circuit (described below).

The black level is the output voltage outside the blanking pulse when no video input signal is available (see *Figure 12*).

Figure 12: Signal waveforms

### 2.12 Preamplifier bandwidth adjustment (4 bits)

An advanced feature: preamplifier bandwidth adjustment (BW: Register 13, see I<sup>2</sup>C table 5), is implemented on the STV9211.

The programming of this BW register is very important to get good video performances.

It must not be set its maximum value. With the following values, the optimum performances are obtained.

| t <sub>R</sub> /t <sub>F</sub> | Preamplifier bandwidth register: BW |         |  |  |

|--------------------------------|-------------------------------------|---------|--|--|

| , K, .t                        | Binary                              | Decimal |  |  |

| 5.5 ± 1 ns                     | 1000                                | 8       |  |  |

| 7.5 ± 1ns                      | 0101                                | 5       |  |  |

| 9.5 ± 1ns                      | 0010                                | 2       |  |  |

| 10 ns and below                | 0000                                | 0       |  |  |

For applications where rise/fall time <5.5ns, this feature offers several advantages:

- Slew-rate: depending on the external capacitive load and on the peak-to-peak output voltage, this adjustment avoids getting any slew-rate phenomenon.

- Electromagnetic radiation (EMI): slowing down the signal of rise/fall time will decrease the EMI without significantly deteriorating the rise/fall time of the CRT driver.

- Video signal response: using this adjustment will allow to optimize the high frequency transient phenomenons.

- Picture boost mode: when displaying still pictures or moving video, having high video swing can be of greater interest than rise/fall time. The preamplifier bandwidth adjustment can be used to avoid any slew-rate phenomenon at the CRT driver output.

#### 2.13 Amplifier bandwidth adjustment (7 bits)

The STV9211 can adjust the bandwidth of any ST video amplifier having a dedicated control pin (CTL). The adjustment is done by I<sup>2</sup>C via Register 6 (see I<sup>2</sup>C table 2).

If not used, the AMPCTL pin must be connected to ground.

### 2.14 CRT cathode, DC-coupling mode (Figure 13)

The STV9211 can be used in DC coupling mode only.

The cut-off (InfraBlack) adjustment is done by the preamplifier.

The infra-black level (Vib) is adjusted independently for each channel via the Registers 10, 11 and 12 (see the complete description in *Section 2.10*).

Figure 13: DC-coupling mode

### 2.15 Preamplifier stand-by mode

The STV9211 is set in stand-by mode either by I<sup>2</sup>C or by decreasing the V<sub>CCP</sub> supply voltage.

- I<sup>2</sup>C: the STV9211 is in stand-by mode when Register 13, bit 7=1

- V<sub>CCP</sub>: the STV9211 is in stand-by mode when V<sub>CCP</sub><3 V

In stand-by mode, the analog blocks are internally switched-off while the logic parts (I<sup>2</sup>C bus and power-on reset) are still supplied.

The power consumption is below 20mW.

### 2.16 Amplifier stand-by mode

The STV9211 can set in stand-by mode any ST video amplifier with the CTL control pin.

When Register 9, bit 7=1, the AMPCTL pin is switched to low level (<0.3V). The amplifier is set in stand-by mode when CTL<0.3V.

If not used, the AMPCTL pin must be connected to ground.

18/38

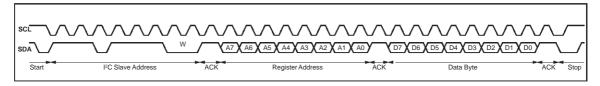

#### 2.17 Serial interface

The 2-wire serial interface is an I<sup>2</sup>C interface. The slave address of the STV9211 is DC hex.

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | W |

|----|----|----|----|----|----|----|---|

| 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0 |

The host MCU can write into the STV9211 Registers. Read mode is not available.

In order to write data into the STV9211, after the "start" message, the MCU must send the following data (see *Figure 14*):

- the I<sup>2</sup>C address slave byte with a low level for the R/W bit,

- the byte to the internal Register address where the MCU wants to write data,

- the data.

All bytes are sent with MSB bit first. The transfer of written data is ended with a "stop" message.

When transmitting several data, the Register addresses and data can be written with no need to repeat the start and slave addresses.

Figure 14: I<sup>2</sup>C write operation

#### 2.18 Power-on reset

A power-on reset function is implemented on the STV9211 so that the  $I^2C$  registers have a determined status after power-on. The Power-on reset threshold for a rising supply on  $V_{CCA}$  (Pin 7) is 3.8 V (typ.) and 3.2V when the  $V_{CC}$  decreases.

### 2.19 Specific application conditions

#### Functioning with V<sub>CCP</sub> below 8 V

To simplify the application, it is possible to supply the power  $V_{CCP}$  with 5 V (instead of 8 V nominal) at the expense of output swing voltage. The CRT Heater voltage (6.2V Typ.) is used very often to supply  $V_{CCP}$ .

#### • Functioning without blanking pulse

If no blanking pulse is applied to the STV9211, it is necessary to ensure the OCL pulse generation (which sets the infra-black level) by setting the Register 8, bit7=1 (OCL = BPCP).

To ensure the device correct behavior in the worst possible conditions, the brightness Register must be set to 0.

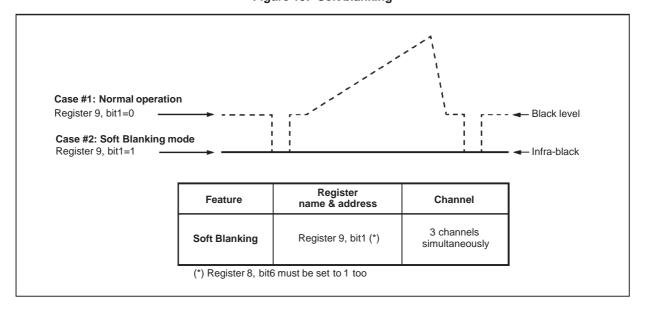

#### Soft blanking

It is possible to blank the video signal by setting the Register 9, bit1=1 and Register 8, bit 6=1.

In this mode the output voltage is set to Vib (see *Figure 15*). This mode is used for example when changing the timing resolution of the video, in order to suppress the video during this transient period.

Figure 15: Soft blanking

# 3 ABSOLUTE MAXIMUM RATINGS

| Symbol            | Parameter                                                             | Pin     | Value | Units |

|-------------------|-----------------------------------------------------------------------|---------|-------|-------|

| V <sub>CCA</sub>  | V <sub>CCA</sub> Supply Voltage on Analog V <sub>CC</sub>             |         | 5.5   | V     |

| V <sub>CCP</sub>  | V <sub>CCP</sub> Supply Voltage on Power V <sub>CC</sub>              |         | 8.8   | V     |

| V <sub>in</sub>   | Voltage at any Input Pins (except Video inputs) and Input/Output Pins | -       | 5.5   | V     |

| V <sub>I</sub>    | Voltage at Video Inputs                                               | 1, 3, 5 | 1.4   | V     |

| V <sub>ESD</sub>  | ESD susceptibility Human Body Model (100pF discharge through 1.5kΩ)   | All     | 2     | kV    |

| T <sub>stg</sub>  | Storage Temperature                                                   | -       | -     | °C    |

| T <sub>oper</sub> | Operating Junction Temperature                                        | -       | +150  | °C    |

# 4 THERMAL DATA

| Symbol               | Parameter                                            | Value | Units |  |

|----------------------|------------------------------------------------------|-------|-------|--|

| R <sub>th(j-a)</sub> | Max. Junction-ambient Thermal Resistance             | 69    | °C/W  |  |

| Tj                   | Typ. Junction Temperature at T <sub>amb</sub> = 25°C | 80    | °C    |  |

#### 5 DC ELECTRICAL CHARACTERISTICS

$T_{amb}$  = 25°C,  $V_{CCA}$  = 5V,  $V_{CCP}$  = 8V, unless otherwise specified.

| Symbol                             | Parameter                                           | Test conditions                                             | Min.          | Тур. | Max.                      | Units  |

|------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|---------------|------|---------------------------|--------|

| SUPPLY                             |                                                     |                                                             | 1             |      | 1                         | l      |

| V <sub>CCA</sub>                   | Analog Supply Voltage                               | Pin 7                                                       | 4.5           | 5    | 5.5                       | V      |

| V <sub>CCP</sub>                   | Power Supply Voltage                                | Pin 17                                                      | 4.5           | 8    | 8.8                       | V      |

| V <sub>CCPS</sub>                  | Power Supply Voltage stand-by threshold             | Pin 17                                                      | 2.5           | 3.0  | 3.5                       | V      |

| I <sub>CCA</sub>                   | Analog Supply Current                               | V <sub>CCA</sub> = 5V                                       |               | 70   |                           | mA     |

| I <sub>CCP</sub>                   | Power Supply Current                                | V <sub>CCP</sub> = 8V                                       |               | 55   |                           | mA     |

| Is                                 | Total Supply Current in stand-by mode               | Pin 17 and pin 7                                            | -             | -    | 5                         | mA     |

| INPUTS, OUT                        | PUTS                                                | 1                                                           | 1             |      | 1                         | ı      |

| V <sub>I</sub>                     | Video Input Voltage Amplitude                       |                                                             |               | 0.7  | 1                         | V      |

| Vo                                 | Output Voltage Range                                |                                                             | 0.5<br>Note 1 |      | V <sub>CCP</sub><br>-0.5V | V      |

| V <sub>IL</sub><br>V <sub>IH</sub> | Low Level Input Voltage<br>High Level Input Voltage | OSD, FBLK, BLK, HS                                          | 2.4           |      | 0.8                       | V<br>V |

| I <sub>IN</sub>                    | Input Current                                       | OSD, FBLK, BLK                                              | -1            |      | 1                         | μΑ     |

| R <sub>HS</sub>                    | Input Resistor                                      | HS                                                          |               | 40   |                           | kΩ     |

| AMPCTL1                            | Amplifier standby threshold                         | Pin 4 @ Register 9, bit 7 = 1 and $I_{4sink}$ = 200 $\mu$ A |               | 80   | 300                       | mV     |

| AMPCTL2                            | Amplifier operating range                           | Pin 4@Register 9,bit 7 = 0<br>and $I_{4sink}$ = 200 $\mu$ A |               |      |                           |        |

|                                    |                                                     | Register 6, bit 4 to bit 7=0000                             |               | 0.7  |                           | V      |

|                                    |                                                     | Register 6, bit 4 to bit 7=1111                             |               | 4.5  |                           | V      |

# **6 AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 25^{\circ}C$ ,  $V_{CCA} = 5V$ ,  $V_{CCP} = 8V$ ,  $V_{i} = 0.7$   $V_{PP}$ ,  $C_{LOAD} = 5pF$

$R_{S}$  = 1000, serial between output pin and  $C_{LOAD}\!,$  unless otherwise specified.

| Symbol                          | Parameter                                            | Test conditions                                                                                    | Min. | Тур.       | Max.    | Units      |

|---------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|------------|---------|------------|

| VIDEO OUT                       | PUT SIGNAL (pins 14, 16, 18) - CONT                  | RAST AND DRIVE                                                                                     |      |            |         |            |

| G                               | Maximum gain                                         | Max Contrast and Drive<br>(CRT = DRV = 254 dec)                                                    |      | 16         |         | dB         |

| VOM                             | Maximum video output voltage (Note 1)                | Max Contrast and Drive (CRT = DRV = 254 dec)                                                       |      | 4.4        |         | V          |

| VON                             | Nominal video output voltage                         | Contrast and Drive at POR (CRT = DRV = 180 dec)                                                    |      | 2.2        |         | V          |

| CAR                             | Contrast attenuation range                           | From max. Contrast (CRT=254 dec) to min. Contrast (CRT = 1 dec)                                    |      | 48         |         | dB         |

| DAR                             | Drive attenuation range                              | From Max. Drive (DRV = 254 dec) to min. Drive (DRV = 1 dec)                                        |      | 48         |         | dB         |

| GM                              | Gain matching (Note 3)                               | Contrast and Drive at POR                                                                          |      | ±0.1       |         | dB         |

| VIDEO OUT                       | PUT SIGNAL (pins 14, 16, 18) - BRIG                  | HTNESS                                                                                             |      | 1          |         |            |

| BRTmax                          | Maximum brightness level                             | Max. Brightness (BRT = 255 dec) and Max. Drive (DRV = 254 dec)                                     |      | 2          |         | V          |

| BRT min                         | Minimum brightness level                             | Min. Brightness (BRT = 0 dec)<br>and Max. Drive (DRV = 254 dec)                                    |      | 0          |         | V          |

| VIP                             | Insertion pulse                                      | (Note 4)                                                                                           |      | 0.4        |         | V          |

| BRTM                            | Brightness matching (Note 3)                         | Brightness and Drive at POR                                                                        |      | ±10        |         | mV         |

| VIDEO OUT                       | PUT SIGNAL - OSD                                     |                                                                                                    | l    | l          |         | l .        |

| VOSDmax                         | Maximum OSD output level                             | Max. Drive (DRV = 254 dec) Max. OSD (OSD = 15 dec)                                                 |      | 4.9        |         | V          |

| VOSD min                        | Minimum OSD output level                             | Min. OSD (OSD = 0 dec)                                                                             |      | 0          |         | V          |

| VIDEO OUT                       | PUT SIGNAL - INFRA BLACK LEVEL                       | (Figure 9)                                                                                         |      |            |         |            |

| Vib0 max<br>Vib0 min            | Maximum infrablack level<br>Minimum infrablack level | IBR=0 and IBL=0<br>Max. Vib (IBL = 255 dec)<br>Min. Vib (IBL = 0 dec)                              |      | 2.2<br>0.4 |         | V          |

| Vib1 max<br>Vib1 min.           | Maximum infrablack level<br>Minimum infrablack level | IBR=1 and IBL=0<br>Max. Vib (IBL = 255 dec)<br>Min. Vib (IBL = 0 dec)                              |      | 1.7<br>0.4 |         | V          |

| Vib step 0                      | Infrablack level step                                | IBR=0 (Note 5)                                                                                     |      | 7          |         | mV         |

| Vib step 1                      | Infrablack level step                                | IBR=1 (Note 5)                                                                                     |      | 5          |         | mV         |

| ABL (Pin 2)                     |                                                      |                                                                                                    |      |            |         |            |

| GABLmin<br>GABL max             | ABL mini attenuation ABL maxi attenuation            | V <sub>ABL</sub> ≥3.2 V<br>V <sub>ABL</sub> = 1 V                                                  |      |            | 0<br>15 | dB<br>dB   |

| V <sub>ABL</sub>                | ABL threshold voltage                                | For output attenuation                                                                             |      |            | 3       | V          |

| IABL high                       | High ABL input current Low ABL input current         | V <sub>ABL</sub> = 3.2V<br>V <sub>ABL</sub> = 1V                                                   |      |            | 0 -2    | μA<br>μA   |

| VIDEO OUT                       | <br> PUT SIGNAL - DYNAMIC PERFORM <i>a</i>           | I .                                                                                                |      |            |         |            |

|                                 | Rise Time, Fall Time (Note 6)                        | V <sub>OUT</sub> = 2 V <sub>PP</sub> (BW = 15 dec)                                                 |      | 2.7        | Ι       | ns         |

| t <sub>R</sub> , t <sub>F</sub> | , ,                                                  | $V_{OUT} = 2 V_{PP} (BW = 0 dec)$                                                                  |      | 5          |         |            |

| BW                              | Large Signal Bandwidth                               | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                               |      | 130        |         | MHz        |

| BW                              | Bandwidth Adjustment Range                           | V <sub>OUT</sub> = 2 V <sub>PP</sub> Minimum bandwidth (BW = 0 dec) Maximum bandwidth (BW =15 dec) |      | 70<br>130  |         | MHz<br>MHz |

| CT                              | Crosstalk between Video Outputs                      | $V_{OUT} = 2 V_{PP} @ f = 10 MHz$                                                                  |      | 60         |         | dB         |

|                                 | Orossiain between video Outputs                      | @ f = 50 MHz                                                                                       |      | 35         |         | dB         |

#### Notes about electrical characteristics

- Note: 1 The video on the preamplifier output must remain above 0.5V even for high frequency signals.

- 2 Assuming that the video output signal remains inside the linear area of the preamplifier output (between 0.5V and  $V_{CCP}$  0.5V)

- 3 Matching measured between the different outputs

- 4 The VIP insertion pulse is present only in "brightness before drive" mode (see Figure 8)

- 5 In kit with the STV95xx amplifier, this 7/5 mV step resolution offers a 100/140mV resolution at the amplifier output

- 6  $t_R$ ,  $t_F$  are calculated values, assuming an ideal input signal with rise/fall time = 0ns

# 7 I<sup>2</sup>C ELECTRICAL CHARACTERISTICS

$T_{amb} = 25$ °C,  $V_{CCA} = 5V$ ,  $V_{CCP} = 8V$ ,  $V_{i} = 0.7 V_{PP}$ ,  $C_{LOAD} = 5pF$

| Symbol                 | Parameter                     | Test conditions                        | Min. | Тур. | Max. | Units |

|------------------------|-------------------------------|----------------------------------------|------|------|------|-------|

| V <sub>IL</sub>        | Low Level Input Voltage       | On Pins SDA, SCL                       |      |      | 1.5  | V     |

| V <sub>IH</sub>        | High Level Input Voltage      |                                        | 3    |      |      | V     |

| I <sub>IN</sub>        | Input Current (Pins SDA, SCL) | 0.4 V < V <sub>IN</sub> < 4.5 V        | -10  |      | +10  | μΑ    |

| f <sub>SCL(Max.)</sub> | SCL Maximum Clock Frequency   |                                        | 0.25 |      | 200  | kHz   |

| V <sub>OL</sub>        | Low Level Output Voltage      | SDA Pin<br>when ACK Sink Current = 6mA |      |      | 0.6  | V     |

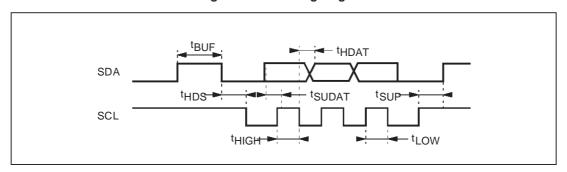

# 8 I<sup>2</sup>C INTERFACE TIMING REQUIREMENTS

| Symbol                          | Parameter                                      | Min. | Тур. | Max. | Units |

|---------------------------------|------------------------------------------------|------|------|------|-------|

| t <sub>BUF</sub>                | Time the bus must be free between two accesses |      |      | 1300 | ns    |

| t <sub>HDS</sub>                | Hold Time for Start Condition                  |      |      | 600  | ns    |

| t <sub>SUP</sub>                | Set-up Time for Stop Condition                 |      |      | 600  | ns    |

| t <sub>LOW</sub>                | The Low Period of Clock                        |      |      | 1300 | ns    |

| t <sub>HIGH</sub>               | The High Period of Clock                       |      |      | 600  | ns    |

| t <sub>HDAT</sub>               | Hold Time Data                                 |      |      | 300  | ns    |

| t <sub>SUDAT</sub>              | Set-up Time Data                               |      |      | 250  | ns    |

| t <sub>R</sub> , t <sub>F</sub> | Rise and Fall Time of both SDA and SCL         |      |      | 20   | ns    |

Figure 16: I<sup>2</sup>C timing diagram

#### I<sup>2</sup>C REGISTER DESCRIPTION 9

Table 2: Register sub-addressed - I2C table 1

| Sub-a | ddress | Register N                            | amas                              | POR | Value | Max. Value |     |

|-------|--------|---------------------------------------|-----------------------------------|-----|-------|------------|-----|

| Hex   | Dec    | - Register N                          | ailles                            | Hex | Dec   | Hex        | Dec |

| 01    | 01     | Contrast (CRT) - Note 1               | 8-bit DAC                         | B4  | 180   | FE         | 254 |

| 02    | 02     | Brightness (BRT)                      | 8-bit DAC                         | B4  | 180   | FF         | 255 |

| 03    | 03     | Drive 1 (DRV) - Note 1                | 8-bit DAC                         | B4  | 180   | FE         | 254 |

| 04    | 04     | Drive 2 (DRV) - Note 1                | 8-bit DAC                         | B4  | 180   | FE         | 254 |

| 05    | 05     | Drive 3 (DRV) - Note 1                | 8-bit DAC                         | B4  | 180   | FE         | 254 |

| 06    | 06     | Amplifier control                     | refer to I <sup>2</sup> C table 2 | 99  | 153   | -          | -   |

| 07    | 07     | OSD Contrast (OSD)                    | 4-bit DAC                         | 09  | 09    | 0F         | 15  |

| 08    | 08     | BPCP & OCL                            | Refer to I <sup>2</sup> C table 3 | 04  | 04    |            |     |

| 09    | 09     | Miscellaneous                         | Refer to I <sup>2</sup> C table 4 | 1C  | 28    |            |     |

| 0A    | 10     | Out 1- Infra-black level: IBL1        | 8-bit DAC                         | B4  | 180   | FF         | 255 |

| 0B    | 11     | Out 2- Infra-black level: IBL2        | 8-bit DAC                         | B4  | 180   | FF         | 255 |

| 0C    | 12     | Out 3- Infra-black level: IBL3        | 8-bit DAC                         | B4  | 180   | FF         | 255 |

| 0D    | 13     | Preamplifier Bandwidth                | 4-bit DAC -                       | 07  | 07    | 0F         | 15  |

|       |        | Adjustment (BW) - Note 2              | I <sup>2</sup> C table 5          |     |       |            |     |

| 0E    | 14     | InfraBlack range and offset selection | Refer to I <sup>2</sup> C table 6 |     |       |            |     |

Table 3: Amplifier bandwidth adjustment register (R6) - I2C table 2

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Function                 | POR<br>value |

|----|----|----|----|----|----|----|----|--------------------------|--------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Min. amplifier bandwidth |              |

| 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | Typ. amplifier bandwidth | х            |

| 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | Max. amplifier bandwidth |              |

Table 4: BPCP & OCL register (R8) - I2C table 3

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Function                                          | POR value |

|----|----|----|----|----|----|----|----|---------------------------------------------------|-----------|

|    |    |    | 0  |    |    | 0  | 0  | Internal BPCP triggered by HS (trailing edge)     | х         |

|    |    |    | 0  |    |    | 1  | 0  | Internal BPCP triggered by HS (leading edge)      |           |

|    |    |    | 0  |    |    | 0  | 1  | Internal BPCP synchronized by BLK (leading edge)  | х         |

|    |    |    | 0  |    |    | 1  | 1  | Internal BPCP synchronized by BLK (trailing edge) |           |

|    |    |    | 0  | 0  | 0  |    |    | Internal BPCP Width = 0.33 μs                     |           |

|    |    |    | 0  | 0  | 1  |    |    | Internal BPCP Width = 0.66 μs                     | Х         |

|    |    |    | 0  | 1  | 0  |    |    | Internal BPCP Width = 1 μs                        |           |

|    |    |    | 0  | 1  | 1  |    |    | Internal BPCP Width = 1.33 μs                     |           |

|    |    |    | 1  |    |    |    |    | Internal BPCP = BPCP input                        |           |

|    |    | 0  |    |    |    |    |    | Normal Operation                                  | х         |

|    |    | 1  |    |    |    |    |    | Reserved (Force BPCP to 1 in test)                |           |

|    | 0  |    |    |    |    |    |    | Normal Operation                                  | х         |

|    | 1  |    |    |    |    |    |    | Reserved (Force OCL to 1 in test)                 |           |

| 0  |    |    |    |    |    |    |    | Internal OCL pulse triggered by BLK               | х         |

| 1  |    |    |    |    |    |    |    | Internal OCL pulse = Internal BPCP                |           |

Table 5: Miscellaneous register (R9) - I<sup>2</sup>C table 4

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Function                                 | POR value |

|----|----|----|----|----|----|----|----|------------------------------------------|-----------|

|    |    |    |    |    |    |    | 0  | Positive Blanking Polarity               | Х         |

|    |    |    |    |    |    |    | 1  | Negative Blanking Polarity               |           |

|    |    |    |    |    |    | 0  |    | Soft Blanking = OFF                      | Х         |

|    |    |    |    |    |    | 1  |    | Soft Blanking = ON (Note 3)              |           |

|    |    |    | 0  |    |    |    |    | Reserved (Test mode, very low bandwidth) |           |

|    |    |    | 1  |    |    |    |    | Normal operation                         | Х         |

|    | 0  | 0  |    |    |    |    |    | Light Grey on OSD Outputs = OFF          | Х         |

|    | 0  | 1  |    |    |    |    |    | Light Grey on OSD Outputs = ON           |           |

|    | 0  | 0  |    |    |    |    |    | Dark Grey on OSD Outputs = OFF           | Х         |

|    | 1  | 0  |    |    |    |    |    | Dark Grey on OSD Outputs = ON            |           |

| 0  |    |    |    |    |    |    |    | Amplifier stand-by = OFF                 | х         |

| 1  |    |    |    |    |    |    |    | Amplifier stand-by = ON                  |           |

Table 6: Preamplifier bandwidth adjustment (R13) - I<sup>2</sup>C table 5

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Function                                                                  | POR<br>value |

|----|----|----|----|----|----|----|----|---------------------------------------------------------------------------|--------------|

|    |    |    |    | 1  | 1  | 1  | 1  | 130 MHz (Note 2)                                                          |              |

|    |    |    |    | 0  | 1  | 1  | 1  | 100 MHz (Note 2)                                                          | х            |

|    |    |    |    | 0  | 0  | 0  | 0  | 70 MHz(Note 2)                                                            |              |

|    |    | 0  | 0  |    |    |    |    | Normal operation                                                          | х            |

|    |    | 0  | 1  |    |    |    |    | Reserved (test mode - BW DAC output connected to BLK input)               |              |

|    |    | 1  | 0  |    |    |    |    | Reserved (test mode - BW DAC complementary output connected to BLK input) |              |

|    | 0  |    |    |    |    |    |    | Brightness before drive                                                   | х            |

|    | 1  |    |    |    |    |    |    | Brightness after drive                                                    |              |

| 0  |    |    |    |    |    |    |    | Preamplifier stand-by = OFF                                               | х            |

| 1  |    |    |    |    |    |    |    | Preamplifier stand-by = ON                                                |              |

Table 7: Cut-off range and offset selection (R14) - I<sup>2</sup>C table 6 - see Figure 9

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Function                                              | POR<br>value |

|----|----|----|----|----|----|----|----|-------------------------------------------------------|--------------|

| -  | -  | -  | -  | -  | -  | -  | 0  | Infra-black range (IBR) = 1.8V                        |              |

| -  | -  | -  | -  | -  | -  | -  | 1  | Infra-black range (IBR) = 1.3V                        | х            |

| -  | -  | -  | -  | 0  | 0  | 0  | -  | Infra-black offset (IB0)- Min. value = 0.4V @ IBL =0  |              |

| -  | -  | -  | -  | 1  | 0  | 0  | -  | Infra-black offset (IB0)- Typ. value = 1.3V @ IBL = 0 | х            |

| -  | -  | -  | -  | 1  | 1  | 1  | -  | Infra-black offset (IB0)- Max. value = 2.2V@ IBL = 0  |              |

# Notes about I<sup>2</sup>C register description

Note: 1 For contrast & drive adjustment, code 00 (dec) and 255 (dec) are not allowed.

2 This register has to be set with the following values:

| t <sub>R</sub> /t <sub>F</sub> | Preamplifier bandwidth register: BW |         |  |  |  |  |

|--------------------------------|-------------------------------------|---------|--|--|--|--|

| *K'*F                          | Binary                              | Decimal |  |  |  |  |

| 5.5 ± 1 ns                     | 1000                                | 8       |  |  |  |  |

| 7.5 ± 1ns                      | 0101                                | 5       |  |  |  |  |

| 9.5 ± 1ns                      | 0010                                | 2       |  |  |  |  |

| 10 ns and below                | 0000                                | 0       |  |  |  |  |

3 to set the device in soft blanking mode, it is necessary to program also Register 8, bit 6 = 1

### 10 STV9211 + STV9556/55/53 APPLICATIONS HINTS

### 10.1 InfraBlack adjustment procedure (Cut-off)

The STV9211 allows to adjust independantly the InfraBlack levels of the 3 video outputs with a high resolution. This ajustment is done via the 3 infra-black level registers (IBL1, IBL2 and IBL3). In order to have the optimum resolution, it is necessary, first, to set the video signal inside the linear area of the amplifier, by programing the infra-black range register IBR (26 or 36V) and the infra-black offset register IBO.

#### Step 1

Setting of the **infra-black range register IBR** (Register 14, bit 0. See I C table 6). This register must be selected, either to 1.3V to get a 26V Cut-off adjustment range with the STV95xx amplifier or to 1.8V to get a 36V range (see *Figure 17*)

#### Step 2

Setting of the **Infra-black offset register IBO** (Register 14, bit 1, 2 & 3. See I C table 6). This register selects the Vib Offset. It allows to keep the video signal inside the linearity area of the amplifier.

The register value depends on the amplifier high voltage supply (Vdd).

In kit with the STV95xx amplifier family, we recommend the following programming:

Case 1: Case 2: **Brightness before Drive Brightness after Drive** Vdd (±5%) **Binary Decimal Binary Decimal** 112 to 115V 001 1 011 3 107 to 111V 010 2 100 4 102 to 106V 011 3 101 5 97 to 101V 100 4 110 6 92 to 96V 7 101 5 111 7 88 to 91 110 6 111 87 and below 111 7 7 111

Table 8: Setting of the infra-black offset register (IBO)

#### Example:

For Vdd=101V +/-5% and Brightness before Drive, IBO must be set to 100.

#### Step 3

Adjustment of the InfraBlack level register IBL (Register 10, 11, 12. See I C table 1).

These three 8 bit- registers adjust separately the infra-black level of the 3 outputs with a high resolution (100mV at 26V range or 140mV at 36V range).

Figure 17: STV9211 and STV95xx - Cut-off adjustment

### 10.2 Preamplifier bandwidth register

The preamplifier bandwidth must not be set to maximum.

To get the optimum video performances and reduce the EMI, we recommend to use the values from *Section 2.12*.

### 10.3 Preamplifier output network

The choice of the network between the STV9211video outputs and the STV95XX amplifier is important. We recommend to use the network described in the application note AN1510.

### 10.4 White balance adjustment

The white balance adjustment on a DC-coupling video system and an AC-coupling video system differs.

Please, use our application note referenced AN1490 for the complete description of the white balance procedure.

Internal schematics STV9211

#### 11 **INTERNAL SCHEMATICS**

Figure 19: ABL GNDA

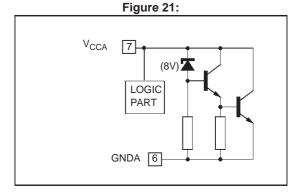

Figure 20: Pin 4 1k AMPCTL 4 GNDA

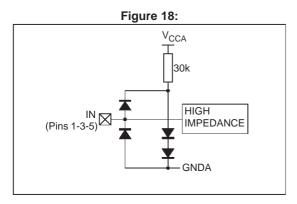

Figure 22:  $V_{CCA}$ OSD-FBLK-HS-BLK Pins 8-9-10 11-19-20 LGNDL \_ GNDA

STV9211 Internal schematics

Figure 26:

Demonstration boards STV9211

# 12 DEMONSTRATION BOARDS

Figure 27: STV9211 + STV9556/55/53 + STV9936S/P demonstration board schematic

STV9211 Demonstration boards

Figure 28: STV9211 - STV9556 - STV9936S/P application schematic

# 13 PACKAGE MECHANICAL DATA

Figure 29: 20 pins - plastic dip

| Dimensions |       | Millimetres |       |       | Inches |       |

|------------|-------|-------------|-------|-------|--------|-------|

| Dimensions | Min.  | Тур.        | Max.  | Min.  | Тур.   | Max.  |

| A          | 3.25  | 3.30        | 3.35  | 0.128 | 0.130  | 0.132 |

| a1         |       | 0.508       |       |       | 0.020  |       |

| В          | 1.39  |             | 1.65  | 0.055 |        | 0.065 |

| b          | 0.381 | 0.457       | 0.533 | 0.015 | 0.018  | 0.021 |

| b1         | 0.20  | 0.254       | 0.30  | 0.008 | 0.010  | 0.012 |

| С          | 5.20  | 5.33        | 5.46  | 0.205 | 0.210  | 0.215 |

| D          | 24.9  | 25.15       | 25.4  | 0.980 | 0.990  | 1.000 |

| E          | 7.8   | 8.5         | 9.1   | 0.307 | 0.335  | 0.358 |

| е          | 2.29  | 2.54        | 2.79  | 0.090 | 0.100  | 0.110 |

| e3         | 22.60 | 22.86       | 23.11 | 0.890 | 0.900  | 0.910 |

| e4         | 7.36  | 7.62        | 7.87  | 0.290 | 0.300  | 0.310 |

| F          | 6.22  | 6.35        | 6.50  | 0.245 | 0.250  | 0.255 |

| T          | 3.42  | 3.68        | 3.93  | 0.135 | 0.145  | 0.155 |

| L          | 3.17  | 3.30        | 3.42  | 0.125 | 0.130  | 0.135 |

| N          |       | 7d          |       |       | 7d     |       |

| R1         |       | 0.152       |       |       | 0.006  |       |

| R2         |       | 0.762       |       |       | 0.030  |       |

| K          |       | 1.524       |       |       | 0.060  |       |

| K1         |       | 0.762       |       |       | 0.030  |       |

| K2         |       | 0.762       |       |       | 0.030  |       |

| Z          |       | 1.27        | 1.34  |       | 0.050  | 0.053 |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2001 STMicroelectronics - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

www.st.com