# **Micropower Sampling 12-Bit A/D Converter**

#### Low Cost

- 12-Bit Serial Sampling ADC

- Guaranteed <u>+</u>1.0 LSB Max INL

- Guaranteed No Missing Codes

- 8-Pin NSOIC Plastic Package

- Low Power @ 250µA including Automatic Shutdown: 1nA(typ)

- Programmable Input Configuration: Full differential or 2 channel single-ended

- Single Supply 3.0V to 5.5V operation

- Half Duplex Digital Serial Interface

- Sample Rate: 40µS

- Pin Compatible Upgrade to LTC 1298

#### DESCRIPTION

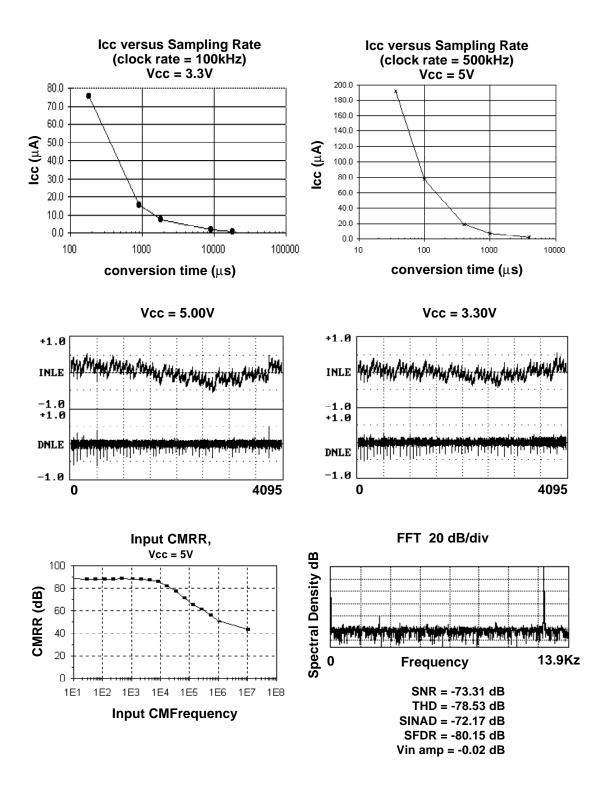

The **SP8538** is a very low power 12-Bit data acquisition chip. The **SP8538** typically draws  $250\mu$ A of supply current when sampling at 25 kHz. Supply current drops linearly as the sample rate is reduced. The ADC automatically powers down when not performing conversions, drawing only leakage current. The **SP8538** is available in 8-Pin NSOIC packages, specified over Commercial and Industrial temperature ranges. The **SP8538** is best suited for Battery-Operated Systems, Portable Data Acquisition Instrumentation, Battery Monitoring, and Remote Sensing applications. The serial port allows efficient data transfer to a wide range of microprocessors and microcontrollers over 3 or 4 wires.

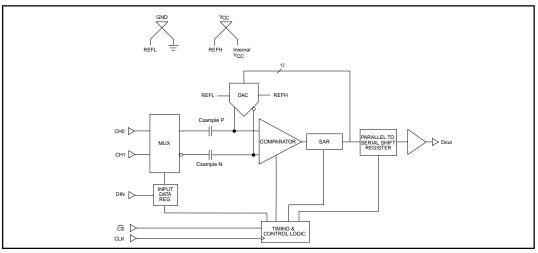

SP8538 Block Diagram

# **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| (TA=+25°C unless otherwise noted) |                  |

|-----------------------------------|------------------|

| VCC to GND                        |                  |

| Vin to GND                        | 0.3 to VCC +0.3V |

| Digital input to GND              | 0.3 to VCC +0.3V |

| Digital output to GND             | 0.3 to VCC +0.3V |

| Operating Temperature Range       |                  |

| Commercial (J, K Version)         | 0°C to 70°C      |

| Industrial (A, B Version)         | 40°C to +85°C    |

| Lead Temperature (Solder 10Sec)   | +300°C           |

| Storage Temperature               | 65°C to +150°C   |

| Power Dissipation to 70°C         | 500mW            |

CAUTION: ESD (ElectroStatic Discharge) sensitive device. Permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. Personnel should be properly grounded prior to handling this device. The protective foam should be discharged to the destination socket before devices are removed.

#### SPECIFICATIONS

Unless otherwise noted the following specifications apply for VCC=5V or 3.3V with limits applicable for Tmin to Tmax. Typical applies for Ta=25°C.

|                                                                                                                                   |                    | CC=5.                         | 0V                                          | V                  | CC=3.                         | 3V                                           |                                       |                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|---------------------------------------------|--------------------|-------------------------------|----------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------|

| PARAMETERS                                                                                                                        | MIN.               | TYP.                          | MAX.                                        | MIN.               | TYP.                          | MAX.                                         | UNITS                                 | CONDITIONS                                                                               |

| DC ACCURACY<br>Resolution<br>Integral Linearity<br>J,A<br>K,B                                                                     |                    | 12<br><u>+</u> 0.6<br>+0.6    | <u>+</u> 2.0<br>+1.0                        |                    |                               | <u>+</u> 2.0<br>+1.0                         | Bits<br>LSB<br>LSB                    |                                                                                          |

| Differential Linearity Error<br>J,A<br>K,B                                                                                        |                    |                               | <u>+</u> 2.0<br><u>+</u> 1.0                |                    |                               | <u>+</u> 2.0<br><u>+</u> 1.0                 | LSB<br>LSB                            | No Missing Codes                                                                         |

| Gain Error<br>J,A<br>K,B                                                                                                          |                    | <u>+</u> 2.0<br><u>+</u> 2.0  | <u>+</u> 10<br><u>+</u> 8                   |                    | <u>+</u> 2.0<br><u>+</u> 2.0  | <u>+</u> 10<br><u>+</u> 8                    | LSB<br>LSB                            |                                                                                          |

| Offset Error<br>J,A<br>K,B                                                                                                        |                    | <u>+</u> 1.5<br><u>+</u> 1.5  |                                             |                    | <u>+</u> 3.0<br><u>+</u> 3.0  | <u>+</u> 8<br><u>+</u> 5                     | LSB<br>LSB                            |                                                                                          |

| ANALOG INPUT<br>Input Signal FS Range<br>Input Impedance<br>On Channel<br>Off Channel<br>Input Bias Current<br>Analog Input Range | 0                  | 20<br>100<br>3<br>100<br>.001 | V <sub>cc</sub><br>1<br>V <sub>cc</sub> +.0 | 0                  | 20<br>100<br>3<br>100<br>.001 | V <sub>cc</sub><br>1<br>/ <sub>cc</sub> +.05 | pF<br>MΩ<br>pF<br>MΩ<br>μA<br>5 Volts | In Parallel with $100m\Omega$<br>In Parallel with $100m\Omega$                           |

| <b>MULTIPLEXER</b><br>Crosstalk ( $f_D$ = Nyquist)<br>Feedthrough ( $f_D$ = Nyquist)                                              |                    | -90<br>-90                    |                                             |                    | -90<br>-90                    |                                              | dB<br>dB                              | Off to On Channel<br>Off to On Channel<br>f <sub>D</sub> = Disturbance                   |

| CONVERSION SPEED<br>Sample Time<br>Conversion Time                                                                                |                    | 1.5<br>12                     |                                             |                    | 1.5<br>12                     |                                              | clock<br>cycles<br>clock              | See Timing Diagrams<br>See Timing Diagrams                                               |

| Complete Cycle<br>Clock Period<br>Clock High Time<br>Clock Low Time                                                               | 2.25<br>1.0<br>1.0 |                               | 25                                          | 10.0<br>4.5<br>4.5 |                               | 5.85                                         | cycles<br>kHz<br>μS<br>μS<br>μS       | See Timing Diagrams<br>See Timing Diagrams<br>See Timing Diagrams<br>See Timing Diagrams |

# **SPECIFICATIONS (cont.)**

Unless otherwise noted the following specifications apply for VCC=5V or 3.3V with limits applicable for Tmin to Tmax. Typical applies for Ta=25°C.

|                                                                                          | V    | CC=5.                          | 0V           | V    | CC=3.                          | 3V           |                       |                                                                                                                  |

|------------------------------------------------------------------------------------------|------|--------------------------------|--------------|------|--------------------------------|--------------|-----------------------|------------------------------------------------------------------------------------------------------------------|

| PARAMETERS                                                                               | MIN. | TYP.                           | MAX.         | MIN. | TYP.                           | MAX.         | UNITS                 | CONDITIONS                                                                                                       |

| DIGITAL INPUTS<br>Input Low Voltage, VIL<br>Input High Voltage, VIH                      | 2.0  |                                | 0.8          | 2.0  |                                | 0.8          | Volts<br>Volts        | V <sub>DD</sub> =5V <u>+</u> 5%<br>V <sub>DD</sub> =5V <u>+</u> 5%                                               |

| Input Current IIN<br>Input Capacitance                                                   | _    | 3.0                            | <u>+</u> 2.0 |      | 3.0                            | <u>+</u> 2.0 | μA<br>pF              |                                                                                                                  |

| DIGITAL OUTPUTS<br>Data Format<br>Data Coding<br>VOH<br>VOL                              | 4.0  |                                | 0.4          | 2.0  |                                | 0.4          | Volts<br>Volts        | See Timing Diagram<br>V <sub>DD</sub> =5V <u>+</u> 5%, IOH=-0.4mA<br>V <sub>DD</sub> =5V <u>+</u> 5%, IOH=+1.6mA |

| AC ACCURACY                                                                              |      |                                |              |      |                                |              |                       |                                                                                                                  |

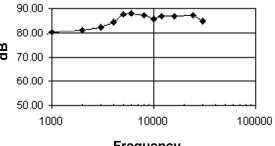

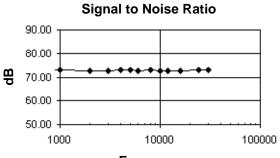

| Spurious free Dynamic<br>Range (SFDR)                                                    |      | 86                             |              |      | 86                             |              | dB                    | For all FFT's<br>(Full Differential Mode)<br>If $V_{CC} = 5V$<br>fsample = 25kHz<br>fin = 12kHz                  |

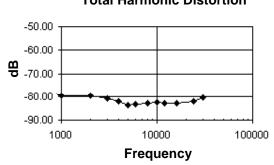

| Total Harmonic Distortion (THD)                                                          |      | -83                            |              |      | -80                            |              | dB                    |                                                                                                                  |

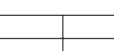

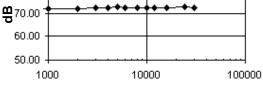

| Signal to Noise &<br>Distortion (SINAD)                                                  |      | 73                             |              |      | 72                             |              | dB                    | If V <sub>CC</sub> = 3.3V<br>fsample = 5.8kHz<br>fin = 2.8kHz                                                    |

| Signal to Noise (SNR)                                                                    |      | 73.5                           |              |      | 72.5                           |              | dB                    |                                                                                                                  |

| SAMPLING DYNAMICS                                                                        |      |                                |              |      |                                |              |                       |                                                                                                                  |

| Acquisition Time to 0.01%                                                                |      | 2                              | 3.38         |      | 3                              | 15.0         | μs                    |                                                                                                                  |

| -3dB Small Signal BW<br>Aperture Delay<br>Aperture Jitter<br>Common-Mode Rejection Ratio | 70   | 5<br>20<br>150<br>80           |              | 70   | 4<br>30<br>150<br>80           |              | MHz<br>nS<br>pS<br>dB | f <sub>CM</sub> = 12.5kHz @ 5 volts<br>2.8kHz @ 3.3 volts                                                        |

| POWER SUPPLIES                                                                           |      |                                |              |      |                                |              | Volts                 |                                                                                                                  |

| V <sub>cc</sub>                                                                          | +3.0 | +5.0                           | +5.5         | +3.0 | +3.3                           | +5.5         |                       |                                                                                                                  |

| Supply Current Operation Mode                                                            |      | 250                            | 400          |      | 150                            | 300          | μA                    | $(\overline{CS}=0)$ 25kHz, 5 volt conversion rate. 5.8kHz 3.3 volts                                              |

| Shutdown Mode                                                                            |      | 0.001                          | 0.5          |      | 0.001                          | 0.5          | μA                    | ( <del>CS</del> =1)                                                                                              |

| Power Dissipation<br>Operating Mode<br>Shutdown Mode                                     |      | 1.25                           | 2<br>2.5     |      | 0.5                            | 0.99<br>1.7  | mW<br>μW              |                                                                                                                  |

| TEMPERATURE RANGE<br>Commercial<br>Industrial<br>Storage                                 | -40  | to +70<br>)° to +8<br>5° to +1 | 85°C         | -40  | to +7(<br>)° to +8<br>5° to +1 |              | С<br>С<br>С<br>С      |                                                                                                                  |

|                    |                                                   | VCC=5.0V VCC=3.3V |      |      |      |      |      |       |

|--------------------|---------------------------------------------------|-------------------|------|------|------|------|------|-------|

| SYMBOL             | PARAMETERS                                        | MIN.              | TYP. | MAX. | MIN. | TYP. | MAX. | UNITS |

| V <sub>cc</sub>    | Supply Voltage                                    | +3.0              | +5.0 | +5.5 | +3.0 | +3.3 | +5.5 | Volts |

| f <sub>CLK</sub>   | Clock Frequency                                   |                   |      | 444  |      |      | 100  | kHz   |

| t <sub>CVC</sub>   | Total Cycle Time                                  | 40                |      |      | 170  |      |      | μS    |

| t <sub>hDI</sub>   | Hold Time D <sub>IN</sub> After<br>CLK^           | 50                | 0    |      | 50   | 0    |      | nS    |

| t <sub>suCS</sub>  | Setup Time CSv<br>Before CLK^                     | 100               |      |      | 150  |      |      | nS    |

| t <sub>suDI</sub>  | Setup Time, D <sub>IN</sub><br>Stable Before CLK^ | 100               | 10   |      | 150  |      |      | nS    |

| t <sub>WHCLK</sub> | CLK High Time                                     | 1                 |      |      | 4.5  |      |      | μS    |

| T <sub>WHCLK</sub> | CLK Low Time                                      | 1                 |      |      | 4.5  |      |      | μS    |

| T <sub>WHCS</sub>  | CS High Time between Data Transfers Cycles        | 100               |      |      | 150  |      |      | nS    |

#### SPECIFICATIONS (cont.) Recommended Operating Conditions

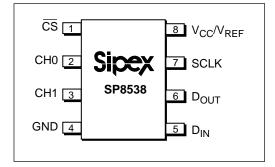

# **PIN DESCRIPTION**

# **PIN ASSIGNMENTS**

- Pin 1-  $\overline{CS}$  Chip Select.

- Pin 2- CH0 Channel 0

- Pin 3- CH1 Channel 1

- Pin 4- GND Ground

- Pin 5- D<sub>IN</sub> Data In

- Pin 6 D<sub>OUT</sub> Data Out

- Pin 7- SCLK Serial Clock

Pin 8-  $V_{CC}/V_{REF}$  - Supply & Reference Voltage

## DESCRIPTION

The **SP8538** is a 12 bit sampling ADC with a programmable two channel multiplexer and serial data interface. The ADC samples and converts 12 bits of data in 40  $\mu$ S with a 5V supply voltage applied. The **SP8538** will also operate at a 3.3V supply at 170 $\mu$ S throughput. The device automatically shuts down to a  $\pm 0.5 \ \mu$ A (MAX) level as soon as the chip is deselected (CS=1). Serial data output is available in an MSB first or LSB first format.

# FEATURES

Two program bits, which are shifted into the device prior to conversion, determine the input configuration. In the single ended MUX configuration the input signal will be applied to either channel 0 or channel 1 and will be ground referenced. The maximum full scale range is VCC. In the full differential mode, the signal will be applied between channel 0 and channel 1. The signals applied at each input may both be dynamic. This is in contrast with pseudo differential devices which must have input low held at a constant level during conversion. The converter will provide significant common mode rejection when used in full differential manner. Both inputs must remain between ground and VCC for proper conversion.

# The device uses a capacitive DAC architecture which provides the sampling behavior. This results in full Nyquist performance at the fastest throughput rate (25 KHz) the device is capable of.

The power supply voltage is variable from 3.0V to 5.5V which provides supply flexibility. At the 5.0V supply level, conversion plus sampling time is  $40\mu$ S and supply current is  $250\mu$ A (1.25 mW). With a 3.3V supply the conversion plus sampling time is  $170\mu$ S and current is reduced to  $150\mu$ A (0.5 mW).

The device features automatic shutdown and will shutdown to a  $\pm 0.5 \,\mu$ A power level as  $\overline{CS}$  is brought high (de-selected). Power is proportional to conversion duty cycle and varies from 250  $\mu$ A at 40 $\mu$ S (Duty cycle = 100%) to 6.25 $\mu$ a at 1.6 ms (Duty cycle = 2.5%).

#### **Examples:**

| <b>Conversion rate</b> | <u>I<sub>cc</sub> @ 5V</u> | Duty Cycle |

|------------------------|----------------------------|------------|

| 40 µS                  | 250 µA                     | 100%       |

| 80 µS                  | 125 µA                     | 50%        |

| 160 µS                 | 62.5 µA                    | 25%        |

#### 0DRESSING

| Mux Addressi | ng       | Cha              | nnel #           | GND              | Comments               |

|--------------|----------|------------------|------------------|------------------|------------------------|

| SGL/DIFF     | ODD/SIGN | 0                | 1                |                  |                        |

| 0            | 0        | V <sub>INH</sub> | V <sub>INL</sub> |                  | Full Differential Mode |

| 0            | 1        | V <sub>INL</sub> | V <sub>INH</sub> |                  |                        |

| 1            | 0        | V <sub>INH</sub> |                  | V <sub>INL</sub> | Single Ended Mux Mode  |

| 1            | 1        |                  | $V_{INH}$        | V <sub>INL</sub> |                        |

# ADC TRANSFER FUNCTION

| INPUT VOLTAGE<br>(V <sub>INH</sub> -V <sub>INL</sub> )* | INPUT VOLTAGE<br>AT $V_{CC}/V_{REF} = 5V$ | OUTPUT<br>CODE |

|---------------------------------------------------------|-------------------------------------------|----------------|

| 0 LSB                                                   | 0V                                        | 0000000000000  |

| 1 LSB                                                   | 0.00122V                                  | 000000000001   |

| 2048 LSB                                                | 2.5000V                                   | 10000000000    |

| 4094 LSB                                                | 4.9976V                                   | 1111111111110  |

| 4095 LSB                                                | 4.9988V                                   | 1111111111111  |

\* See Mux Addressing Table for a definition of  $V_{INH}$  -  $V_{INL}$ .

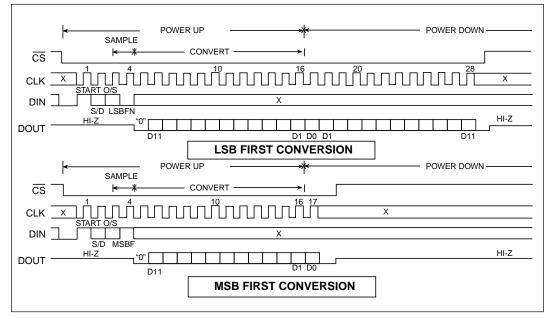

1.6 mS  $6.25 \,\mu\text{A}$  2.5% The device can be configured such that it delivers serial data MSB first requiring 17 clock periods for a full conversion. Alternately, the device can be programmed to deliver 12 bits of data MSB first, followed by the same 12 bits of data LSB first. This sequence will require 28 clock periods to complete. Please refer to the timing diagram.

## **Circuit Operation**

The device will ignore any leading zeros applied to the DIN pin even if CS is low. After Chip Select Bar (CS) is brought low and the START bit is clocked in to the converter, the conversion sequence is initiated. Three additional bits are clocked in immediately following the START bit: SGL/DIFF, ODD/ SIGN & MSBF. The second and third bits clocked in determine the MUX configuration (see MUX addressing table). The fourth bit determines the data output format (MSB first or LSB first). Please refer to the timing diagram.

The SGL/DIFF bit when zero sets the input MUX for full differential mode and when one, sets the input MUX for single ended mode. The ODD/SIGN bit when zero sets channel zero as the positive input (ground referred for single ended operation and referred to channel one in differential mode). With the ODD/SIGN bit one, channel one will be the positive input (ground referred for single ended operation and referred to channel zero in differential mode).

With MSBF set to one, the output data stream will be MSB through LSB, with MSBF set to zero the output data stream will be MSB through LSB followed by the same data in LSB through MSB format.

The **SP8538** is a SAR converter with full differential multiplexed front end, capacitive DAC, precision comparator, Successive Approximations Register, control logic and data output register. After the input is sampled and held the conversion process begins. The DAC MSB is set and its output is compared with the signal input, if the DAC output is less than the input, the comparator outputs a one which is latched into the SAR and simultaneously made available at the ADC serial output pin. Each bit

is tested in a similar manner until the SAR contains a code which represents the signal input to within  $\pm 1/2$  LSB. During this process the SAR content has been shifted out of the ADC serially. If the MSB first format was chosen, the data will appear at the DOUT pin MSB through LSB in 17 clock periods. If the LSB first format was chosen then during conversion the data will appear at the DOUT pin just as before (MSB through LSB) but the LSB will be followed by D1, D2 through the MSB. This sequence will require 28 clock periods. Note that the Chip Select Bar pin must be toggled high between conversions. The DOUT pin will be in a high impedance state whenever Chip Select Bar is high. After Chip Select Bar has been toggled and brought low again, the converter is ready to accept another START bit and begin a new conversion.

# **Full Differential Sampling**

The SP8538 can be configured for single-ended sampling (i.e. CH0-ground or CH1-ground) or full differential sampling (CH0-CH1 or CH1-CH0). In the full differential sampling configuration, both inputs are sampled and held simultaneously. Because of the balanced differential sampling, dynamic common mode noise riding along the input signal is cancelled above and beyond DC noise. This is a significant improvement over psuedo-differential sampling schemes, where the low side of the input must remain constant during the conversion, and therefore only DC noise (i.e. signal offset) is cancelled. If AC common mode noise is left to be converted along with the differental component, the output signal will be degraded.

Full differential sampling allows flexibility in converting the input signal. If the signal low-side is already tied to a ground elsewhere in the system, it can be hardwired to the low side channel (i.e. CH0 or CH1) which acts as a signal ground sense, breaking a potential ground loop. It is also possible to drive the inputs balanced differential, as long as both inputs are within the power rails. In this configuration, both the high and low signals have the same impedance looking back to ground, and therefore pick up the same noise along the physical path from signal source (i.e. sensor, transducer, battery) to converter. This noise becomes common mode, and is cancelled out

# by the differential sampling of the **SP8538**. Layout Considerations

To preserve the high resolution and linearity of the **SP8538** attention must be given to circuit board layout, ground impedance and bypassing.

A circuit board layout which includes separate analog and digital ground planes will prevent the coupling of noise into sensitive converter circuits and will help to preserve the dynamic performance of the device. In single ended mode, the analog input signal should be referenced to the ground pin of the converter. This prevents any voltage drops that occur in the power supply's common return from appearing in series with the input signal.

In full differential mode, the high and low side board traces should run close to each other, with the same layout. This will insure that any noise coupling will be common mode, and cancelled by the converters (patent pending) full differential architecture.

If separate analog and digital ground planes are not possible, care should be used to prevent coupling between analog and digital signals. If analog and digital lines must cross, they should do so at right angles. Parallel analog and digital lines should be separated by a circuit board trace which is connected to common.

The **SP8538** VCC pin is also the reference pin for the device. This means that noise on the VCC pin will be proportionally represented as noise in the converters output data. A noise signal of 1.22mV (at a 5V supply) will produce 1 LSB of error in the output data. The VCC pin should be bypassed to the ground pin with a parallel combination of a 6.8µF tantalum and a 0.1µF ceramic capacitor. To maintain maximum system accuracy, the supply connected to the VCC pin should be well isolated from digital supplies and wide load variations. A separate conductor from the supply regulator to the A/D converter will limit the effects of digital switching elsewhere in the system. Power supply noise can degrade the converters performance. Especially corrupting are noise and spikes from a switching power supply.

To avoid introducing distortion when driving the A/D converter input, the input signal source should be able to charge the **SP8538's** equivalent 20 pF of input capacitance from zero volts to the signal level in 1.5 clock periods.

SP8538 Timing Diagram

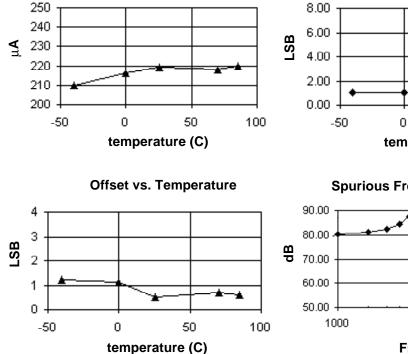

Icc vs. Temperature

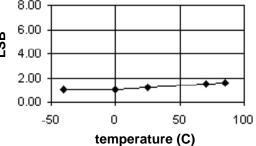

Gain Error vs. Temperature

**Spurious Free Dynamic Range**

Frequency

Frequency

SINAD

Frequency

**Total Harmonic Distortion**

90.00

80.00

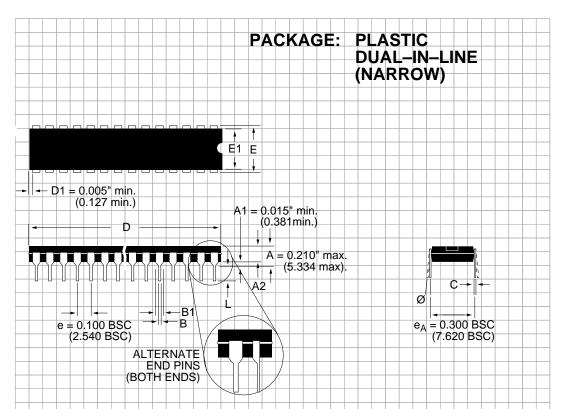

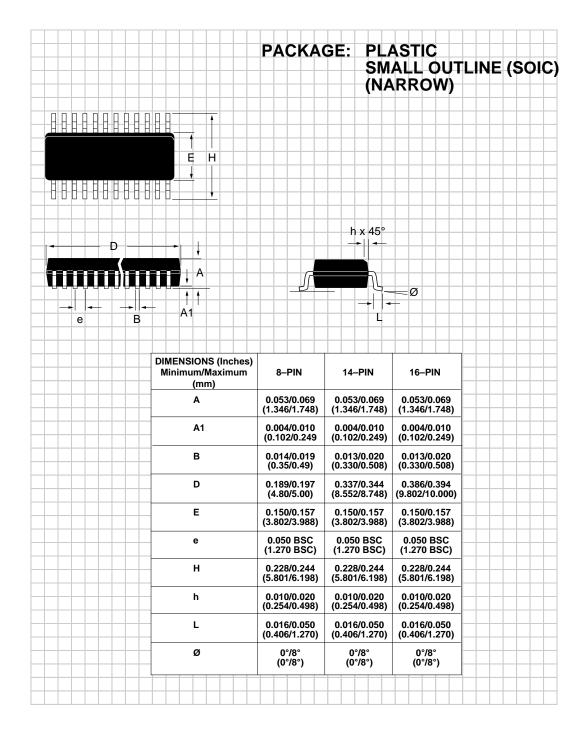

| DIMENSIONS (Inches)<br>Minimum/Maximum<br>(mm) | 8–PIN          | 14–PIN          | 16–PIN          | 18–PIN          | 20–PIN          | 22–PIN          |

|------------------------------------------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| A2                                             | 0.115/0.195    | 0.115/0.195     | 0.115/0.195     | 0.115/0.195     | 0.115/0.195     | 0.115/0.195     |

|                                                | (2.921/4.953)  | (2.921/4.953)   | (2.921/4.953)   | (2.921/4.953)   | (2.921/4.953)   | (2.921/4.953)   |

| В                                              | 0.014/0.022    | 0.014/0.022     | 0.014/0.022     | 0.014/0.022     | 0.014/0.022     | 0.014/0.022     |

|                                                | (0.356/0.559)  | (0.356/0.559)   | (0.356/0.559)   | (0.356/0.559)   | (0.356/0.559)   | (0.356/0.559)   |

| B1                                             | 0.045/0.070    | 0.045/0.070     | 0.045/0.070     | 0.045/0.070     | 0.045/0.070     | 0.045/0.070     |

|                                                | (1.143/1.778)  | (1.143/1.778)   | (1.143/1.778)   | (1.143/1.778)   | (1.143/1.778)   | (1.143/1.778)   |

| С                                              | 0.008/0.014    | 0.008/0.014     | 0.008/0.014     | 0.008/0.014     | 0.008/0.014     | 0.008/0.014     |

|                                                | (0.203/0.356)  | (0.203/0.356)   | (0.203/0.356)   | (0.203/0.356)   | (0.203/0.356)   | (0.203/0.356)   |

| D                                              | 0.355/0.400    | 0.735/0.775     | 0.780/0.800     | 0.880/0.920     | 0.980/1.060     | 1.145/1.155     |

|                                                | (9.017/10.160) | (18.669/19.685) | (19.812/20.320) | (22.352/23.368) | (24.892/26.924) | (29.083/29.337) |

| E                                              | 0.300/0.325    | 0.300/0.325     | 0.300/0.325     | 0.300/0.325     | 0.300/0.325     | 0.300/0.325     |

|                                                | (7.620/8.255)  | (7.620/8.255)   | (7.620/8.255)   | (7.620/8.255)   | (7.620/8.255)   | (7.620/8.255)   |

| E1                                             | 0.240/0.280    | 0.240/0.280     | 0.240/0.280     | 0.240/0.280     | 0.240/0.280     | 0.240/0.280     |

|                                                | (6.096/7.112)  | (6.096/7.112)   | (6.096/7.112)   | (6.096/7.112)   | (6.096/7.112)   | (6.096/7.112)   |

| L                                              | 0.115/0.150    | 0.115/0.150     | 0.115/0.150     | 0.115/0.150     | 0.115/0.150     | 0.115/0.150     |

|                                                | (2.921/3.810)  | (2.921/3.810)   | (2.921/3.810)   | (2.921/3.810)   | (2.921/3.810)   | (2.921/3.810)   |

| Ø                                              | 0°/ 15°        | 0°/ 15°         | 0°/ 15°         | 0°/ 15°         | 0°/ 15°         | 0°/ 15°         |

|                                                | (0°/15°)       | (0°/15°)        | (0°/15°)        | (0°/15°)        | (0°/15°)        | (0°/15°)        |

#### **ORDERING INFORMATION**

| Model    | Linearity (LSB) | Temperature Range | Package                   |

|----------|-----------------|-------------------|---------------------------|

| SP8538BN | ±1.0            | 40°C to +85°C     | 8-pin, 0.3" Plastic DIP   |

| SP8538KN | ±1.0            | –0°C to +70°C     | 8-pin, 0.3" Plastic DIP   |

| SP8538BS | ±1.0            | 40°C to +85°C     | 8-pin, 0.15" Plastic SOIC |

| SP8538KS | ±1.0            | –0°C to +70°C     | 8-pin, 0.15" Plastic SOIC |

| SP8538AN |                 | 40°C to +85°C     | 8-pin, 0.3" Plastic DIP   |

| SP8538JN | ±2.0            | –0°C to +70°C     | 8-pin, 0.3" Plastic DIP   |

| SP8538AS | ±2.0            | 40°C to +85°C     | 8-pin, 0.15" Plastic SOIC |

| SP8538JS | ±2.0            | –0°C to +70°C     | 8-pin. 0.15" Plastic SOIC |

Please consult the factory for pricing and availability on a Tape-On-Reel option.

#### SIGNAL PROCESSING EXCELLENCE

#### Sipex Corporation

#### Headquarters and

Sales Office 22 Linnell Circle Billerica, MA 01821 TEL: (978) 667-8700 FAX: (978) 670-9001 e-mail: sales@sipex.com

Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (978) 934-7500 FAX: (978) 935-7600

#### CELLENCE

#### European Sales Offices:

#### ENGLAND:

Sipex Corporation 2 Linden House Turk Street Alton Hampshire GU34 IAN England TEL: 44-1420-549527 FAX: 44-1420-542700 e-mail: mikeb@sipex.co.uk

#### GERMANY:

Sipex GmbH Gautinger Strasse 10 82319 Stamberg TEL: 49.81.51.89810 FAX: 49.81.51.29598 e-mail: sipex-starnberg@t-online.de

#### Far East:

#### JAPAN:

Nippon Sipex Corporation Yahagi No. 2 Building 3-5-3 Uchikanda, Chiyoda-ku Tokyo 101 TEL: 81.3.3256.0577 FAX: 81.3.3256.0621

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described hereing; neither does it convey any license under its patent rights nor the rights of others.